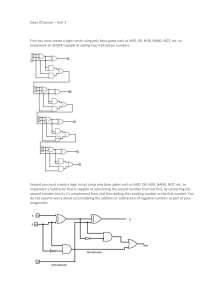

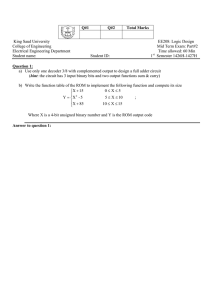

The University of Trinidad and Tobago Bachelor of Applied Sciences Utilities Engineering Point Lisas For Lecturer: Sohan Heerah Digital Electronics- ELEC 2022 LABORATORY R E P O R T O F: Binary Adders and Subtractors Table of Contents Objectives ..................................................................................................................................................... 2 Results:.......................................................................................................................................................... 5 Lab Part 1: ................................................................................................................................................. 5 Lab Part 2: ................................................................................................................................................. 6 Lab Part 3: ................................................................................................................................................. 7 Discussion: .................................................................................................................................................... 8 Conclusion: ................................................................................................................................................. 10 References:.................................................................................................................................................. 11 Objectives 1. To verify the operation of a Full Adder. 2. To verify the operation of a Subtractor. 3. To design and implement a circuit to detect overflow in four-bit signed computations. Prelab: Results: Lab Part 1: Output Inputs A1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 C1 0 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 Expected S1 0 0 1 1 0 1 1 0 1 1 0 0 1 0 0 1 S0 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 C1 0 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 Actual S1 0 0 1 1 0 1 1 0 1 1 0 0 1 0 0 1 S0 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 Lab Part 2: Output Inputs A1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Expected Bin1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Bin0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 B1 1 0 0 0 1 1 0 0 1 1 1 0 1 1 1 1 D1 0 1 1 0 0 0 1 1 1 0 0 1 1 1 0 0 D0 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 Actual Output (2’s Complement) B1 D1 D0 1 0 0 0 1 1 0 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 0 1 0 1 1 0 0 0 1 1 1 1 1 1 1 0 1 0 1 1 0 0 Lab Part 3: Discussion: Synthesis of certain efficient arithmetic circuits for binary and decimal arithmetic suitable for quantum applications have been proposed in this thesis. Reversible logic is used and the designs are realized using simple and efficient reversible logic gates. As more features are integrated within battery powered electronic devices like cell phones, laptops nowadays, it drains the battery quickly. So the need for new technology or circuit technique is necessitated to reduce power dissipation and area of arithmetic units used in processing elements. Various circuit design techniques and algorithms are proposed for arithmetic units using reversible logic. 2’s Complement: 2’s complement is done by taking the 1’s complement of a binary number and then adding binary 1 to it. The 1’s complement of a binary number is simply the inverse of the initial binary. Eg. 0110 1001(1’s complement) 1010(2’s complement). Magnitude overflow. Overflow occurs when the final two carry-outs have different values, and a correct sum is produced when they have the same value Overflow is detected by the logic operation for 4-bit adders Overflow = C3’C4 + C3C4’ For n-bit numbers we have: Overflow = Cn-1 ⊕ Cn Full Adder A full adder is a combination of logic gates that accepts 2 inputs, a carry in, carry out and gives an output. The output is the sum of the two binary inputs. The logic gates that makes up the full adder are 2 XOR gates, 2 AND gates and 1 OR gate Truth table for a Full adder. A1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 Cin 0 1 0 1 0 1 0 1 C0 0 0 0 1 0 1 1 1 Output1 0 1 1 0 1 0 0 1 By usage of a truth table, in the pre-lab a combination circuit was designed to verify if two 4-bit numbers were equal, less than, greater than, or had any overflow. By analysis of the truth table, a combination circuit was derived, and tested. It was shown that the circuit produced the desired output. Conclusion: The operation of the full adder and subtractor was verified. A circuit to detect magnitude overflow was successfully designed and implemented for two 4-bit signed computations. References: https://www.sciencedirect.com/topics/computer-science http://www.ittc.ku.edu/~jstiles/412/handouts https://www.allaboutcircuits.com/textbook ELEC 2022 – Lecture notes: Lecture 3 and Lecture 4.