E15 – FALL 2014 – ZUCKER HOMEWORK 4 1. Convert the

advertisement

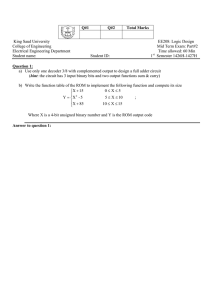

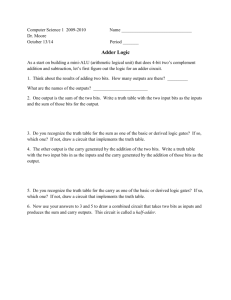

E15 – FALL 2014 – ZUCKER HOMEWORK 4 1. Convert the following decimal numbers to binary 4-bit two’s complement representations, or explain why the conversion is not possible. a. 3 b. ´5 c. 6 d. ´10 e. ´4 f. 14 2. Perform these 4-bit two’s complement sums, following the example below. In addition to the sum, indicate the decimal representations of the addends and the 4-bit result. If the conversion of the 4-bit result from two’s complement binary to decimal does not equal the correct quantity, please indicate that overflow has occurred. Example: 0101 ` 1101. 1 1 (carry bits) 0101 (5) ` 1101 (-3) 1 0010 (2) a. 0100 ` 0011 b. 1100 ` 0101 c. 0111 ` 0101 d. 1101 ` 1011 e. 1110 ` 1001 3. Let A3 , B3 , and S3 represent the MSB of the 4-bit addends and sum, respectively, of a two’s complement addition operation. How can we determine of overflow has occurred simply by examining these three bits alone? 1 E15 – FALL 2014 – ZUCKER HOMEWORK 4 4. Consider this 4-bit ripple carry adder/subtractor circuit, which is comprised by four full adders along with four XOR gates. A3 B3 A2 B2 FA Cout A1 B1 FA S3 A0 B0 FA S2 Op FA S1 S0 The inputs are as follows: A3:0 and B3:0 are the two 4-bit operands, in two’s complement binary. When the Op input is equal to zero, the circuit performs addition (as we showed in class); however, we will now show that the circuit performs subtraction when Op is equal to one. a. What happens to each Bi when Op “ 1? Use the XOR truth table to help you determine this. b. Imagine that each of the bits of A are equal to zero, and imagine that B3 “ 0 (that is, the two’s complement number B is non-negative). In this case, what is the relationship between the number B and the number S? c. Use your answer above to explain how the overall effect of the circuit is to subtract B from A when Op “ 1. 5. Download the binary arithmetic and delay.zip file from the course website. Then modify the four bit rca nodelay.v file to create a new file named four bit adder subtractor.v which implements the circuit depicted above. Verify that your circuit works by compiling the adder subtractor test.v testbench, running the simulation, and comparing the output of your circuit to the expected output in a waveform viewer. Please turn in your completed four bit adder subtractor.v source file, along with a printout of the waveform trace confirming that your module is correct. Note: you should select the “signed” radix/format in your waveform viewer to make sure the numbers are displayed correctly. 2