Boise State University Digital Systems Laboratory Electrical and Computer Engineering Department ECE230L

advertisement

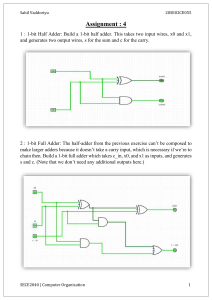

Boise State University Electrical and Computer Engineering Department Digital Systems Laboratory ECE230L Lab 6: Arithmetic Unit Name: ______________________________ Objective: Design, build, and test an adder/subtractor unit In class lecture, you have been shown how to build a larger functional unit using a basic module (with functionality verified). In this lab, you will apply a similar process to build an arithmetic unit with add and subtract functions. This arithmetic unit is to be controlled using just one control bit. Let’s call this control signal add /sub . When add /sub is 0, the arithmetic unit will add. Otherwise, it will function as a subtractor. The arithmetic units in the Xilinx ISE libraries are not allowed. The following are what you are expected to complete for this laboratory assignment (during laboratory time): 1. Design a full-adder for addition of two 1-bit numbers. 2. Now using your design in (1), design an adder that adds two 4-bit numbers. Your design has to be modularized with hierarchy. 3. Modify your 4-bit-adder to function as a subtractor. 4. Use Xilinx ISE and simulator to verify your 1-bit and 4-bit designs. Choose a set of test values that test all scenarios including overflow conditions. This should cover all possible cases for carry-in and carry-out of the most significant bit. You need the test cases for both addition and subtraction. Check-off: ________________ 5. Implement your design on the FPGA using eight switches to input two 4-bit test vectors and one push button as add /sub control signal. 6. Provide a set of test cases (both addition and subtraction) with expected results for the TA to use during check off. (+7) + (+2) (+9) 0111 + 0010 1001 c4 = 0 c3 = 1 Overflow Example test case Check-off: ________________ Report: Record all results (including, but not limited to: 1-bit module, 4-bit module, prototyping platform used, schematic diagram, simulation waveform, results, and discussions) in your team report. Page 1 of 1 Fall 2010