Tunnel Field Effect Transistor (TFET) Review

advertisement

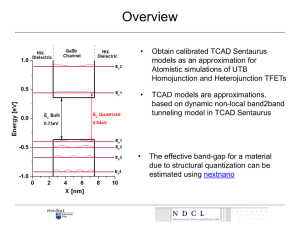

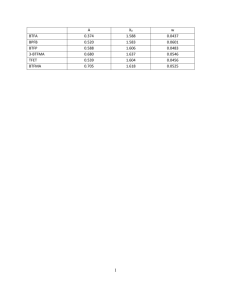

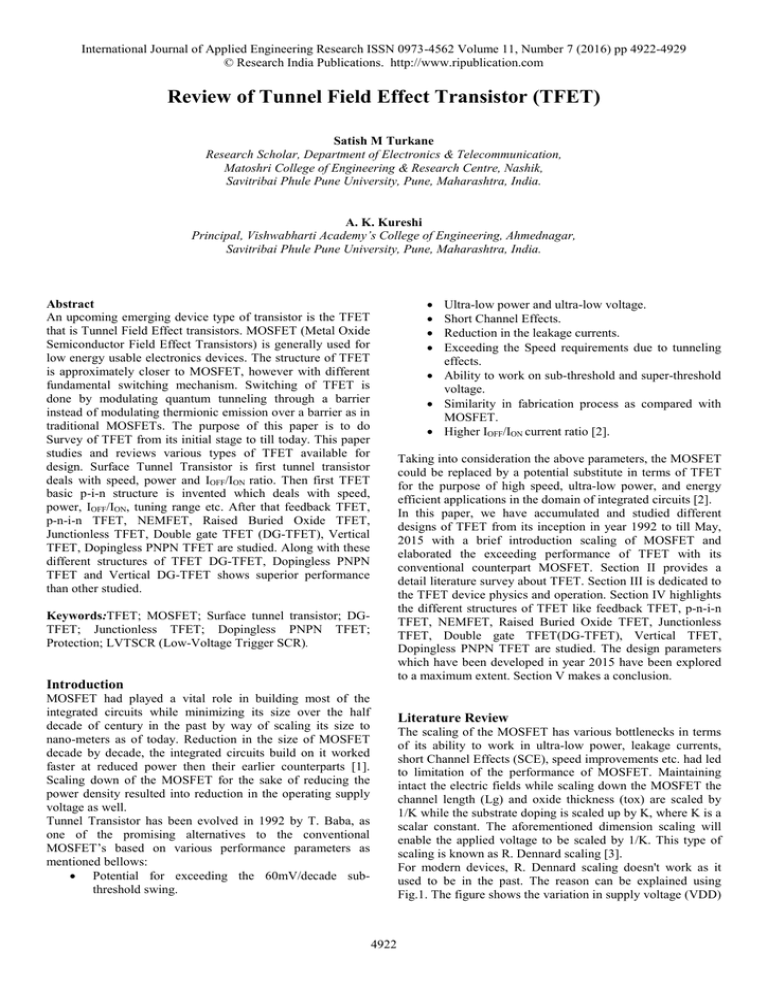

International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com Review of Tunnel Field Effect Transistor (TFET) Satish M Turkane Research Scholar, Department of Electronics & Telecommunication, Matoshri College of Engineering & Research Centre, Nashik, Savitribai Phule Pune University, Pune, Maharashtra, India. A. K. Kureshi Principal, Vishwabharti Academy’s College of Engineering, Ahmednagar, Savitribai Phule Pune University, Pune, Maharashtra, India. Abstract An upcoming emerging device type of transistor is the TFET that is Tunnel Field Effect transistors. MOSFET (Metal Oxide Semiconductor Field Effect Transistors) is generally used for low energy usable electronics devices. The structure of TFET is approximately closer to MOSFET, however with different fundamental switching mechanism. Switching of TFET is done by modulating quantum tunneling through a barrier instead of modulating thermionic emission over a barrier as in traditional MOSFETs. The purpose of this paper is to do Survey of TFET from its initial stage to till today. This paper studies and reviews various types of TFET available for design. Surface Tunnel Transistor is first tunnel transistor deals with speed, power and IOFF/ION ratio. Then first TFET basic p-i-n structure is invented which deals with speed, power, IOFF/ION, tuning range etc. After that feedback TFET, p-n-i-n TFET, NEMFET, Raised Buried Oxide TFET, Junctionless TFET, Double gate TFET (DG-TFET), Vertical TFET, Dopingless PNPN TFET are studied. Along with these different structures of TFET DG-TFET, Dopingless PNPN TFET and Vertical DG-TFET shows superior performance than other studied. Ultra-low power and ultra-low voltage. Short Channel Effects. Reduction in the leakage currents. Exceeding the Speed requirements due to tunneling effects. Ability to work on sub-threshold and super-threshold voltage. Similarity in fabrication process as compared with MOSFET. Higher IOFF/ION current ratio [2]. Taking into consideration the above parameters, the MOSFET could be replaced by a potential substitute in terms of TFET for the purpose of high speed, ultra-low power, and energy efficient applications in the domain of integrated circuits [2]. In this paper, we have accumulated and studied different designs of TFET from its inception in year 1992 to till May, 2015 with a brief introduction scaling of MOSFET and elaborated the exceeding performance of TFET with its conventional counterpart MOSFET. Section II provides a detail literature survey about TFET. Section III is dedicated to the TFET device physics and operation. Section IV highlights the different structures of TFET like feedback TFET, p-n-i-n TFET, NEMFET, Raised Buried Oxide TFET, Junctionless TFET, Double gate TFET(DG-TFET), Vertical TFET, Dopingless PNPN TFET are studied. The design parameters which have been developed in year 2015 have been explored to a maximum extent. Section V makes a conclusion. Keywords:TFET; MOSFET; Surface tunnel transistor; DGTFET; Junctionless TFET; Dopingless PNPN TFET; Protection; LVTSCR (Low-Voltage Trigger SCR). Introduction MOSFET had played a vital role in building most of the integrated circuits while minimizing its size over the half decade of century in the past by way of scaling its size to nano-meters as of today. Reduction in the size of MOSFET decade by decade, the integrated circuits build on it worked faster at reduced power then their earlier counterparts [1]. Scaling down of the MOSFET for the sake of reducing the power density resulted into reduction in the operating supply voltage as well. Tunnel Transistor has been evolved in 1992 by T. Baba, as one of the promising alternatives to the conventional MOSFET’s based on various performance parameters as mentioned bellows: Potential for exceeding the 60mV/decade subthreshold swing. Literature Review The scaling of the MOSFET has various bottlenecks in terms of its ability to work in ultra-low power, leakage currents, short Channel Effects (SCE), speed improvements etc. had led to limitation of the performance of MOSFET. Maintaining intact the electric fields while scaling down the MOSFET the channel length (Lg) and oxide thickness (tox) are scaled by 1/K while the substrate doping is scaled up by K, where K is a scalar constant. The aforementioned dimension scaling will enable the applied voltage to be scaled by 1/K. This type of scaling is known as R. Dennard scaling [3]. For modern devices, R. Dennard scaling doesn't work as it used to be in the past. The reason can be explained using Fig.1. The figure shows the variation in supply voltage (VDD) 4922 International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com and threshold voltage (VT). Where VT is a function of channel length (Lg) [3]. As can be seen, as the channel length reduces below 0. 35 um the linear dependencies between VDD and VT is no longer linear. For example, as if we reduce initial value of VDD up to 1/5th then VT reduces to 50% of its initial value [4]. of its initial value which results in increase in leakage power [4]. Now as technology is scaled down up to nanometers, transistors count per unit chip area increases therefore its leakage power constraints are also increases. Due to this its standby power consumption in the device is also gets increases. The decrease in the VT is not the proper solution from the above discussion [4]. In order to solve these issues, recent literatures have proposed Tunnel FETs (TFETs). The advantages of TFET are low subthreshold current which leads to low leakage per device and its high ION/IOFF ratio can be suitable for memory application, etc. As discussed above there are limitations with VDD and VT scaling. Fig. 2 represents the changes of leakage energy (EL) and dynamic energy (EDYN) with supply voltage VDD for both MOSFET and TFET [7]. Figure 1: The plot of technology generation Vs voltage (i. e. supply voltage and threshold voltage) where reduction of VT is quite less but reduction of VDD is occur with respect to device parameters [5]. The most important consequence of scaling is that the gate overdrive voltage (VGS-VT equivalent to VDD-VT) remains almost constant for advanced technology nodes (short channel lengths). When gate overdrive voltage decreases, the oncurrent decreases, which negatively affects device performances such as ION/IOFF ratio and dynamic speed (CVDD/Ion). There are two possible solutions to this problem of low on-current of advanced technology nodes, (a) Increase VDD (b) Reduce VT [4]. Figure 2: Showing EDYN and EL variations with supply voltage VDD, Energy dissipation is lower for lower SS devices (TFET) [7]. Increasing VDD For an inverter, the dynamic power consumption [6] can be expressed in (1) Pdynamic = f CL VDD2 (1) The expression for (EDYN) and (EL) are as given below [7]: EDYN αVDD2 (3) EL / V DD 2 10(-VDD/SS) Where f is the frequency of operation and CL is the capacitive load. As can be seen, with increase in VDD the dynamic loss in the gate inverter increases. Similarly, the static power consumption [6] is given by (2) Pleakage = Ileak VDD (2) (4) Where SS is the sub-threshold slope of the TFET. Equations (3) and (4) states that for MOSFETs, both leakage and 2 dynamic energy are proportional to𝑉𝐷𝐷 . However, leakage energy also has an additional exponential dependence on SS. Equation (4) shows that lower the sub-threshold slope lower will be the EL [8]. As mentioned before, changing VDD, affects the device performance. Therefore, one way is to find a device with lower sub-threshold slope (SS < 60 mV/dec). TFET exhibits these characteristics. Therefore, at lower voltages (VDD), TFET exhibits lower ET (Total energy = EL + EDYN) compared to a MOSFET [4]. The TFET follows band-to-band tunneling mechanism with the quantum-mechanical generation of carriers. Scaling of a gate length in the MOSFET, it shows short channel effects for a span of higher number of the electron wave-length. TFET is Where Ileak is switch off leakage current of MOSFET in the device structure. It is clear from the above expressions that both static and dynamic power loss of the devices increases as a function of supply voltage (VDD). Reduce VT Second option for keeping the high gate overdrive is to scale down VT. For an average 60 mV/decade reduction in VT, the off-current (IOFF) or sub-threshold current increase by 10 times 4923 International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com highly compatible for standard CMOS process flow. For TFET optimization of the doping profile and better control of one mask are important factors but these are not important for the CMOS flow [9]. Therefore, TFET is an emerging alternative type for next scaling of the gate length however which is not affected by short channel effects [10]. As the device structure of TFET is decreased then its static power consumption is gets reduced ultimately [9]. In the ON state of TFET, the carriers tunnel through the barrier which is band gap between valence band and conduction band for the flow of current from drain-to-source. Whereas in OFF state, available barrier maintains off current magnitude lower than that of off current magnitude of the conventional MOSFET. The inherent properties of TFETs make them suitable for low power digital applications [4]. junction electric field on the gate-source voltage should be maximized [4]. Different Structures of TFET TFET Device Physics and Operation Band to Band Tunneling (BTBT) This phenomenon provides an expression for the tunneling transmission of carriers and can be achieve by Wentzel, Kramer’s and Brillouin (WKB) approximation and considering the tunnel barrier as a triangular shaped potential barrier. According to WKB approximation, 𝑇𝑡 ≈ exp [− 4 √2𝑚. 3 𝑞𝐹ђ 3⁄ 2 . (𝐸𝑔 ) ] Figure 3: Evaluation of Tunnel Field Effect Transistor. A. Surface Tunnel Transistors (1992-2000) Toshio Baba presented the surface tunnel transistor (STT) which was a new type of tunnel device which could operate normally even in very small structures with gate lengths of less than 0.1µm at room temperature. The STT consists of an n+/i/p+ diode structure with an insulated gate in the i-region. Highly degenerated drain had a sharp doping profile for a low doped substrate and makes a tunnel junction with the 2D electron channel under the gate. The STTs were fabricated using a GaAs/AlGaAs Heterojunction in order to study the basic characteristics of this new device. Their current-voltage characteristics exhibited transistor action without saturation characteristics in the drain current similar to a vacuum triode operation. These characteristics of STTs were anticipated by the theory of interband tunneling [13]. (5) Equation (5) is a common way to express BTBT transmission. Here ṁ-the electron effective mass, ђ-Planck's constant divided by 2×2π, Eg is the band gap of the semiconductor material at the tunnel junction, and F is the electric field measured in V/m. This equation can be improved slightly by making it more specific to tunneling transitory [10]. There are four important conditions in order for band-to-band tunneling to take place: 1. Available states to tunnel-from, 2. Available states to tunnel-to, 3. An energy barrier that is sufficiently narrow for tunneling to take place and 4. Conservation of momentum [11]. Subthreshold swing in Tunnel FETs In order to describe the expression for the sub-threshold swing of a BTBT device, consider the BTBT current is given below [11-12] for reverse-biased p-n junction: −𝑏 𝐼 = 𝑎𝑉𝑒𝑓𝑓 𝐸𝑒 𝐸 Where 𝑎 = 𝐴𝑞 2𝑚. 𝑔 3 ђ2 𝜋 2 √𝐸 (6) (7) Where A is the device cross sectional area and 𝑏 = 4√ 𝑚 . 3 𝐸𝑔 ⁄2 3𝑞ђ (8) Accordingly, the sub-threshold swing in a TFET increases with gate-source voltage and much steeper at lower gate voltages. The second term describes that the derivative of the a. Thermal equilibrium 4924 International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com peak-to-valley ratio of 5 and higher current tunneling densities than GaAs MJ-STTs that is 500-times [15]. B. Basic p-i-n structure (2004) Toshio baba proposed tunnel FET (TFET) with the aim of steep swing in 2004 [13]. This device structure is having similarity to Lubistor. It requires higher doping levels and source/drain junction to be abrupt. The TFET works like reverse biased PN diode, where the insulated gate controls the tunneling [16]. b. Weak carrier accumulation (a) (b) Figure 5: (a) Device structure of TFET, (b) band diagram of TFET [16]. c. Strong carrier accumulation Figure 4 (a,b,c): Schematic cross section of an STT and band diagram at the semiconductor surfaces [13]. Bhuwalka et al. predict that after their simulation if the gate oxide gets broader then it will increase a SS. Addition of a δ𝑝 + layer adjacent to the 𝑝+ terminal, it improves the electric field in between i-to-𝑝+ . Proposed SS formula is given by [16]: Fig. 4a shows cross sectional view of the proposed STTs which consists of a drain, a source and an insulated gate. Although the STT structure is match to Si-MOSFET or HEMT, the doping polarity of the drain terminal is different from the source terminal. This is an important difference from conventional FETs. These are crucial factors for STT operation [13]. As surface tunnel transistor is already proposed and then it developed as a new NDR device for high performance with GaAs and InGaAs materials [14]. Then new STTs were proposed as MJ-STTs (multiplejunction surface tunnel transistors). To increase its functionality, in its structure source, gated n+/p+ tunneljunctions and drain are connected in series respectively. MJSTTs have improved in-terms of the characteristics with added logics for multiple-valued circuits. For 6 successive NDR characteristics of transistors operations were accurately demonstrate with InGaAs based MJ-STTs also it has high 𝑆𝑇𝑢𝑛𝑛𝑒𝑙 = ln(10).𝑉𝐺2 𝐵 3⁄ 2𝑉𝐺+ 𝑘𝑎𝑛𝑒 𝐸𝑔 2 (9) ⁄ 𝐷′ Where BKane and D are the constants. Equation (9) shows that for sharp swing VG should be low as possible [16]. By considering ID with BTBT current (IBTBT), by simplifying BTBT current equation we get equation (9). (Igen) is the semiclassical thermal generation current around the junction of semiconductor devices which are operating at room temperature [16]: EID= IBTBT +Igen (10) When IBTBT>Igen, Equation (10) gets the equation for the swing value [16]: 4925 International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com 𝑐 𝑆𝑇𝑢𝑛𝑛𝑒𝑙 ≅ 𝑆𝑇𝑢𝑛𝑛𝑒𝑙 1+𝑆𝑇𝑢𝑛𝑛𝑒𝑙 E. Raised Buried Oxide Tunnel FET (2012) The flow of current in the tunnel FET depends on tunneling probability. As it has a disadvantage of ION in large band gap silicon is lower, so Raised Buried Oxide TFET is designed. Non equilibrium Green’s function formalism is used for the quantum capacitance determination. A heterogate oxide and SOI structure with Raised Buried Oxide in drain is proposed to achieve ITRS requirement and reduced Miller capacitances. For reduction of parasitic bipolar current and increment of current heterogate dielectric structure is used. This proposed structure is used to achieve: Maximum ION, Minimum IOFF, Maximum ION/ IOFF ratio, Minimum SS and Reduced Miller capacitance effect. (11) 𝐼𝑔𝑒𝑛 𝑑 ( ) 𝑑𝑉𝐺 𝐼𝐵𝑇𝐵𝑇 As device is operating at room temperature 𝑑 ( 𝐼𝑔𝑒𝑛 𝑑𝑉𝐺 𝐼𝐵𝑇𝐵𝑇 )takes a 𝑐 𝑆𝑇𝑢𝑛𝑛𝑒𝑙 >STunnel, negative value then we get which is an intrinsic disadvantage of the structure. Also we can say that on the purity of tunneling process a sharp swing is depend. Based on the gate voltage polarity, one of the issues of TFET which rises is about the gate-induced transversal field which increases/decreases the reverse-biased tunnel of the junction [16]. For TFET, if gate bias is applied then it works as a reverse biased pin-diode which is an advantage of the TFET. Purity of the surface defines the static leakage current of the diode and diode reduces it by 2x of magnitude [17]. But it also has a limitation that its sharp swing is present for very thin gate voltage range, at least up to now [16]. A low band gap material improves the tunneling probability like Ge. Hence it has maximum ION (>1mA), transconductance (gm), output conductance, and dynamic power consumption (Pdynamic) of 0. 067X10-5 watt achieved at 109 ION/IOFF ratio and significantly improved overshoot and undershoots with respect to conventional TFET. Therefore, RBO Tunnel FET is widely used for ultra-low power digital applications [19]. C. Feedback FET (2008) Alvaro Padilla et al. proposed the feedback FET which is designed to achieve a steep swing. Its device structure is closer to Lubistor; but it has under lapped gate electrode. It has gate side walls for energy barrier purpose for electrons around n+-i junction (source junction) and for holes i-p+ junction (drain junction). As positive gate voltage is applied at the source and drain junction near the gate sidewalls, some holes and electrons are trapped which lowers the potential of holes and electrons near the drain and source junction respectively. Due to this sudden decrement of barrier height and an abrupt SS (~2mV/decade) occurs [16]. For transition of the OFF state to ON state it requires gate side wall insulator to be charged. It however not a disadvantage of the proposed device, but has some issues like: 1. The VT on the forward sweep and on the reverse sweep is different. 2. The VT always depends on the VD [16]. F. Junctionless TFET (2013) The proposed JL-TFET is a Si-channel heavily n-type-doped with different isolated gates (Control-Gate, P-Gate) with different work-functions. This is because of JL-TFET should be similar to conventional TFET. The subthreshold swing of JL-TFETs is lower than 60mV/decade. These are actually quantum mechanical devices which are based on band-to-band tunneling (BTBT) principle. It has higher electrical performance but lower variability than MOSFET. This happens due to absence of p-n junctions. JL-TFET is mostly attractive because of better tunneling current and low band-gap hetero structure channel [20]. D. p-n-i-n TFET (2011) Wei Cao proposed a new structure which is basically a conventional TFET with a narrow n-layer at the tunneling junction. It has two main advantages like higher ION and lower SS with respect to the conventional TFET. Its IV characteristics and reliability are assured. Recent researches note that reliability issue is one of the major hurdles for TFET. It happens due to near tunneling junction at the channel/dielectric interface, where there is strong electric field in parallel and antiparallel directions [18]. The j (E) is tunneling current density is given by the nonlocal model for the BTBT [18], i. e. (12) j (E) = αT(E)f(Ef1, Efr)ΔE F-1. Asymmetric Junctionless For efficient ON-OFF switching, source and drain are optimized by using the asymmetric junctionless source/body region and junctional drain/body region separately. Due to ndrain/p+body junction, the off-state tunnel barrier can be extended into the drain due to drain/body junction. Therefore, AJ-TFET is an alternative approach for sub-10-nm region [21]. G. Double gate TFET (DG-TFET) (2008-2015) The DG-TFET has an added gate which improves or doubled the current. Due to that it’s On current gets boosted and OFF current gets in the range of fempto amperes or Pico amperes or it can be increases by some factor but remains extremely low. It is a lateral n-type TFET in narrow silicon layer. The separation of this device layer from substrate is done by using dielectric material layer. In between intrinsic and p+ region tunneling take place [22]. Here α-constant, T(E)-tunneling coefficient depended on energy, f(Ef1, Efr)-state occupation factor function of quasiFermi levels at the two different tunneling junction. ΔEenergy range. The thin n-pocket increases the tunneling field Ey. The increment is higher at center of body (x = Tsi/2) than that of the surface of Si (x = 0. 1 nm). Thus changing in device process, the sensitivity of the TFET characteristics may get improved [18]. 4926 International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com Subthreshold Swing in upcoming days will be highly important parameter. So we can consider that Vertical TFET is useful for obtaining maximum ION/IOFF ratio. This can be useful for Si based devices, also could be applied to scaled devices which follow Moore's law [24]. G-1. Dual Material DG-TFET Rajat Vishnoi et al. proposed a double material gate TFET (DMG) [23]. It has lower work function for tunneling gate than auxiliary gate for a n-channel TFET and higher than auxiliary gate for a p-channel TFET [32]. It has maximum ION and minimum IOFF and SS with reduced drain saturation voltage [23]. I. Dopingless PNPN TFET (2013-2015) I-1. PNPN TFET In this semiconductor device gate controls, the BTBT tunneling current between source and channel using modulation due to extra n pocket. For the removal kink effect in PNPN TFET the silicon film thickness optimized [25]. The PNPN Tunnel Structure (Fig. 6) has a tunneling junction formed in between the p+ source and fully depleted thin nlayer (n-pocket) in the gate. It helps in the reduction of tunneling width and it creates local band bending. Addition of thin n pocket region improves the tunneling rate, improves subthreshold and with the same instant of time gives maximum ION with respect to conventional design of TFET [25]. G-2. Triple Metal DG-TFET The main aim of the selection of three metals with different work function is to increase ON current and make a barrier in the channel, due to that its OFF current gets reduced. The surface potential (𝜙𝑠𝑛 (𝑥)) under different metals and the electric fields (𝐸𝑛𝑥 (𝑥), 𝐸𝑚𝑦 (𝑥)) (lateral and vertical electric field respectively) are calculated for the tunneling current value using 2-D Poisson’s equation and Kane’s model. The surface potential under different metals is expressed as: 𝛽 𝜙𝑠1 (𝑥) = 𝐴 𝑒𝑥𝑝(𝜂𝑥) + 𝐵 𝑒𝑥𝑝(−𝜂𝑥) − 1⁄𝛼 (13) 𝑓𝑜𝑟 0 ≤ 𝑥 ≤ 𝐿1 𝑢𝑛𝑑𝑒𝑟 𝑀1 𝜙𝑠2 (𝑥) = 𝐶 𝑒𝑥𝑝(𝜂(𝑥 − 𝐿1)) 𝛽 +𝐷 𝑒𝑥𝑝(−𝜂(𝑥 − 𝐿1)) − 2⁄𝛼 (14) 𝑓𝑜𝑟 𝐿1 ≤ 𝑥 ≤ (𝐿1 + 𝐿2)𝑢𝑛𝑑𝑒𝑟 𝑀2 𝜙𝑠3 (𝑥) = 𝐸 𝑒𝑥𝑝(𝜂(𝑥 − 𝐿1 − 𝐿2)) 𝛽 (15) 𝐹 𝑒𝑥𝑝(−𝜂(𝑥 − 𝐿1 − 𝐿2)) − 3⁄𝛼 𝑓𝑜𝑟(𝐿1 + 𝐿2) ≤ 𝑥 ≤ 𝐿𝑢𝑛𝑑𝑒𝑟 𝑀3 The expression for Electric Field is, Figure 6: PNPN Tunnel Structure [26]. For Lateral Electric Field𝑑𝜙 (𝑥,𝑦) 𝐸1𝑥 (𝑥) = − 1 | = −𝐴 𝜂 𝑒𝑥𝑝(𝜂𝑥) + 𝐵 𝜂 𝑒𝑥𝑝(−𝜂𝑥) 𝑑𝑥 𝑦=0 Table I: Comparative analysis of PNPN TFET and Conv. TFET [25] (16) 𝑓𝑜𝑟 0 ≤ 𝑥 ≤ 𝐿1 𝑑𝜙2 (𝑥, 𝑦) 𝐸2𝑥 (𝑥) = − | 𝑑𝑥 𝑦=0 = −𝐶 𝜂 𝑒𝑥𝑝(𝜂(𝑥 − 𝐿1)) + 𝐷 𝜂 𝑒𝑥𝑝(−𝜂(𝑥 − 𝐿1)) 𝑓𝑜𝑟𝐿1 ≤ 𝑥 ≤ (𝐿1 + 𝐿2)𝑢𝑛𝑑𝑒𝑟𝑀2 𝑑𝜙3 (𝑥, 𝑦) 𝐸3𝑥 (𝑥) = − | 𝑑𝑥 𝑦=0 = −𝐸 𝜂 𝑒𝑥𝑝(𝜂(𝑥 − 𝐿1 − 𝐿2)) +𝐹 𝜂 𝑒𝑥𝑝(−𝜂(𝑥 − 𝐿1 − 𝐿2)) 𝑓𝑜𝑟 (𝐿1 + 𝐿2) ≤ 𝑥 ≤ 𝐿𝑢𝑛𝑑𝑒𝑟 𝑀3 Lg (nm) (17) PNPN TFET Ron SS Ion/ (KΩ/µm) (mV/dec) Ioff 30 35 40 45 50 55 60 (18) 42.6 46.1 48 48.5 50.2 53.3 62 53.1 55.3 62 65.6 68 72.2 73.2 Conventional TFET Ron SS Ion/ (KΩ/µm) (mV/dec) Ioff 108 4×107 6×107 4.2×107 107 0.6×107 106 64.1 61.2 60 58.6 57 53.8 50 93.2 90 91.2 91 90 72 71.3 105 105 0.1×106 0.2×106 0.4×106 0.7×106 106 For vertical Electric Field𝑑𝜙 (𝑥,𝑦) 𝐸1𝑦 (𝑥) = − 1 = −𝐶11 (𝑥) − 2𝑦𝐶12 (𝑥) (19) 𝑓𝑜𝑟 0 ≤ 𝑥 ≤ 𝐿1 (19) 𝑑𝜙 (𝑥,𝑦) 𝐸2𝑦 (𝑥) = − 2 = −𝐶21 (𝑥) − 2𝑦𝐶22 (𝑥) Therefore, PNPN is suitable for low power requirement applications [26]. For PNPN TFET IDS is (20) 𝑓𝑜𝑟𝐿1 ≤ 𝑥 ≤ (𝐿1 + 𝐿2)𝑢𝑛𝑑𝑒𝑟𝑀2 𝑑𝜙 (𝑥,𝑦) 𝐸3𝑦 (𝑥) = − 3 = −𝐶31 (𝑥) − 2𝑦𝐶32 (𝑥) 𝐼𝐷𝑠 = 𝐴𝑘𝑎𝑛𝑒 𝐷2 𝑤𝑔 (21) Where, 𝑑𝑦 𝑑𝑦 𝑑𝑦 −1⁄ 2 3⁄ 𝑓𝑜𝑟 (𝐿1 + 𝐿2) ≤ 𝑥 ≤ 𝐿𝑢𝑛𝑑𝑒𝑟 𝑀 𝐴𝑘𝑎𝑛𝑒 = (𝑒 2 𝑚0 2 ) (18𝜋ℎ2 ) H. Vertical TFET (2006-2015) Vertical TFET have SS in very small range of mV/dec. The doping profile and design flow situations also changes the SS. Therefore, it is an alternative TFET to give lower 𝐵𝑘𝑎𝑛𝑒 = (𝜋𝑚0 2 ) (2𝑒ℎ) 1⁄ 4927 3⁄ 2 )/(𝑉 2 −(𝐵𝑘𝑎𝑛𝑒 𝑊𝑔 𝑉𝐺𝑠 𝑒 𝐺𝑆 .𝐷) (22) (23) (24) International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com Sub-threshold Swing of TFET, 𝑙(𝑙𝑜𝑔𝐼𝑑 ) 𝑆𝑇𝐹𝐸𝑇 = ( 𝑑𝑉𝑔𝑠 [4] −1 ) (25) [5] Sub-threshold Slope, 𝑆𝑇𝐹𝐸𝑇 = ( 2 𝑉𝑔𝑠 )[mV/decade] 5.75(𝑉𝑔𝑠 +𝐶𝑜𝑛𝑠𝑡) [6] (26) I-2. Dopingless PNPN The charge plasma concept is used for the design of dopingless TFET designed on a narrow i-silicon layer. Due to charge plasma concept, doping’s are not required for source and drain. Instead we choose different work functions for source, drain and both metal electrodes. For fabrication of doping-less TFET high-temperature doping/annealing process is not used therefore ultimately it reduces the thermal budget [26]. Surface depletion width is given by[27], 𝑊𝑠𝑢𝑟𝑓𝑎𝑐𝑒 (𝑘, 𝑇, 𝑉𝑔 , 𝑁𝐴 ) = 𝑊𝑠𝑢𝑟𝑓𝑎𝑐𝑒 (𝑘) (27) [7] [8] [9] Dopingless TFET is candidate for low-power and low-cost applications in the future [28]. It shows promising switching behaviour and quite decrement in PVT variations on subthreshold swing and drive current than that of conventional-TFET [29]. Now doping-less TFET shows very good electrostatic control over the channel with reduced thermal budget and process complexity. [10] Conclusion This paper explains different types of TFET from initial stages of its inception to till recent. Surface Tunnel Transistor is first tunnel transistor deals with speed, power and IOFF/ION ratio. Then first TFET basic p-i-n structure is invented which deals with speed, power, IOFF/ION, tuning range etc. After that feedback TFET, p-n-i-n TFET, NEMFET, Raised Buried Oxide TFET, Junctionless TFET, Double gate TFET (DGTFET), Vertical TFET, Dopingless PNPN TFET are studied. Along with these different structures of TFET DG-TFET, Dopingless PNPN TFET and Vertical DG-TFET shows superior performance than other studied. [11] [12] [13] References [1] [2] [3] [14] Alan Seabaugh, “Quantum tunneling is a limitation in today’s transistors, but could be the key to future devices, ” IEEE spectrum, 30th September, 2013. Aswathy, M., Nitha M. Biju, and Rama Komaragiri., “Comparison of a 30nm Tunnel Field Effect Transistor and CMOS Inverter Characteristics,” 3rd International Conference on Advances in Computing and Communications, Cochin, pp 149-152, Aug. 2013. R. Dennard, F. Gaensslen, H.-N. Yu, V. Rideout, E. Bassous, and A. LeBlanc, “Design of Ion-Implanted MOSFETs with Very Small Physical Dimensions,” IEEE J. Solid-State Circuits, vol. 9, no. 5, pp. 256268, October 1974. [15] [16] [17] 4928 Deepak Kumar's M. TECH thesis, “Tunnel FETs and Its Application to Digital Circuits,” Indian Institute of Technology, Kanpur, June 2015. P. Packan, Short Course, International Electron Devices Meeting short courses (IEDM) 2007. Peter Nilsson, “Arithmetic Reduction of the Static Power Consumption in Nanoscale CMOS,” 13th IEEE International Conference on Electronics, Circuits and Systems, pp 656-659, Nice, 10-13 December 2006. Adrian M. Ionescu and Heike Riel, “Tunnel field effect transistors as energy efficient electronic switches,” Nature 479, pp. 329-337, Nov. 2011. Benton H. Calhoun and Anantha Chandrakasan, “Characterizing and Modelling Minimum Energy Operation for Subthreshold Circuits,” International Symposium Low Power Electronics and Design, Newport Beach, CA, USA, pp 90-95, August 2004. Thomas Nirschl, Stephan Henzler, Christian Pacha, Peng-Fei Wang, Walter Hansch, Georg Georgakos and Dons Schmitt-Landsiedel, “The Tunneling Field Effect Transistor (TFET) used in a Single-EventUpset (SEU) insensitive 6 transistor SRAM cell in ultra-low voltage applications,” 4th IEEE Conference on Nanotechnology, pp 402-405, 2004. Th. Nirschl, P. F. Wang, C. Weber, J. Sedlmeii, R. Heinrich, R. Kakoschke, K. Schriife, J. Holz, C. Pacha, T. Schulz, M. Ostermayr, A. Olbrich, G. Georgakos, E. Ruderer, W. Hansch and D. SchmittLandsiedell, “The tunneling field effect transistor (TFET) used in a single-eventupset (SEU) insensitive 6 transistor SRAM cell in ultra-low voltage applications,”4th IEEE Conference on Nanotechnology, 2004. S. M. Sze, “Physics of Semiconductor Devices, ” 2nd edition (New York: John Wiley and Sons, Inc., 1981). Q. Zhang. “Low-Subthreshold-Swing Tunnel Transistors,” IEEE Electron Device Letters, April 2006. T. Baba, “Proposal for Surface Tunnel Transistors, ” Jpn. J. Appl. Phys., Vol. 31, no. 4B, pp. L455-L457, 1992. T. Uemura and T. Baba, “Direct Gate-controlled NDR Characteristics in Surface Tunnel Transistor, ” 1996. T. Baba and T. Uemura, “Development of InGaAs based multiple-junction surface tunnel transistors for multiple-valued logic circuits”, Proc. 28th Int. Symp. Multiple-Valued Logic, Fukuoka, Japan, pp. 7-12, 1998. Yasuhisa Omura, “SoiLubistors: Lateral, Unidirectional, Bipolar-Type Insulated-Gate Transistors,” John Wiley & Sons, Singapore Pte. Ltd., Part seven, chapter 23, pp 247-260, 2013. Thomas Nirschl, Peng-Fei Wang, Walter Hansch and Doris Schmitt-Landsiedel, “The tunneling field effect transistor (TFET): the temperature dependence, the simulation model, and its application,” International International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929 © Research India Publications. http://www.ripublication.com [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] Symposium Circuits and Systems, Vol. 3, pp 713716, 23-26 May 2004. Wei Cao, C. J. Yao, G. F. Jiao, Daming Huang, H. Y. Yu, and Ming-Fu Li, “Improvement in Reliability of Tunneling Field-Effect Transistor with p-n-i-n Structure,” IEEE Transactions on Electron Devices, Vol. 58, no. 7, July 2011. Alvaro Padilla, Chun Wing Yeung, Changhwan Shin, Chenming Hu, and Tsu-Jae King Liu, “Feedback FET: A Novel Transistor Exhibiting Steep Switching Behavior at Low Bias Voltages, ” IEEE International Electron Devices Meeting, San Francisco, 15-17 December 2008. Balmukund Rahi, Bahniman Ghosh and Pranav Asthana, “A simulation-based proposed high-k heterostructureAlGaAs/Si junctionless n-type tunnel FET, ” Journal of Semiconductors, 2014. Chun-Hsing Shih and Nguyen Dang Chien, “Sub-10nm Tunnel Field-Effect Transistor with Graded Si/Ge Heterojunction,” IEEE Electron Device Letters, pp 1498-1500, November 2011. Adrian Ionescu, “Double Gate Tunnel FET with ultrathin silicon body and high-k gate dielectric,” European Solid-State Device Research Conference, September 2006. M. Jagadesh Kumar and Sindhu Janardhanan, “Doping-Less Tunnel Field Effect Transistor: Design and Investigation, ” IEEE Transactions on Electron Devices, pp 3285-3290, October 2013. Zhong-Fang Han, Guo-Ping Ru and Gang Ruan, “A Simulation Study of Vertical Tunnel Field Effect Transistors,” 9th International Conference Association of Surgeons of India, pp 25-28, Xiamen, October 2011. Brinda Bhowmick, Srimanta Baishya and Rajsekhar Kar, “Length scaling of Hetero-gate dielectric SOI PNPN TFET,” 2011 Annual IEEE India conference, (INDICON),Hyderabad, pp.1-4,16-18 December 2011. L. Megala, B. Devanathan, R. Venkatraman and A. Vishnukumar , “Tunneling Field Effect Transistors for Low Power Digital Systems,” International Journal of Innovative Technology and Exploring Engineering, Vol. 2, pp.296-299, April 2013. Cui Ning, Liang Renrong, Wang Jing, Zhou Wei, and Xu Jun, “A PNPN tunnel field-effect transistor with high-k gate and low-k fringe dielectrics,” Journal of Semiconductors, Vol. 33, no. 8, August 2012. M. Saketh Ram, Dawit Burusie Abdi, “Dopingless Tunnel FET with a Hetero-Material Gate: Design and Analysis,” IEEE 2nd International Conference on Emerging Electronics (ICEE- 2014), Bengaluru, 3-6 December, 2014. Avinash Lahgere, Chitrakant Sahu, and Jawar Singh, “PVT Aware Design of Dopingless Dynamically Configurable Tunnel FET,” IEEE Transactions on Electron Devices, Vol. 62, Issue. 8, pp.2404-2409, 2015. Author: Satish M Turkane is Pursuing his Ph. D and working as Associate Professor in E&Tc Engineering at Pravara Rural Engineering College Loni, Ahmednagar, Maharashtra, India. He has more than 16 Years of teaching experience. His area of interest is in the field of Low power FPGA, Interconnects and Post CMOS Devices and Circuits in Analog and Digital domain. He is a Life Member of ISTE, IEI and IETE. A K Kureshi had completed his Ph. D in 2010 in the area of Low Power Techniques and Architecture of FPGAs. He is working as a Principal at Vishvabharti Academy’s College of Engineering, Ahmednagar, Maharashtra, India. He has more than 19 Years of teaching experience. His area of interest is in the field of Carbon Nano Tubes as Interconnects and logics and in Multi-layer Graphene domain. He is a Member of IEEE and Life Member of ISTE, IEI and IETE. 4929