Copyright © 2009 Year IEEE. Reprinted from IEEE ELECTRON

advertisement

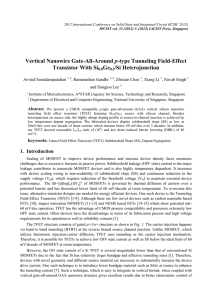

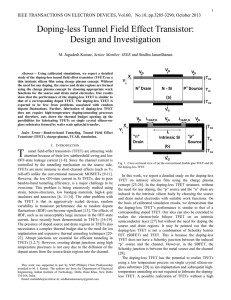

Copyright © 2009 Year IEEE. Reprinted from IEEE ELECTRON DEVICE LETTER. Such permission of the IEEE does not in any way imply IEEE endorsement of any of Institute of Microelectronics’ products or services. Internal of personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permission@ieee.org. 754 IEEE ELECTRON DEVICE LETTERS, VOL. 30, NO. 7, JULY 2009 Demonstration of Tunneling FETs Based on Highly Scalable Vertical Silicon Nanowires Z. X. Chen, H. Y. Yu, N. Singh, N. S. Shen, R. D. Sayanthan, G. Q. Lo, and D.-L. Kwong Abstract—This letter demonstrates a vertical silicon-nanowire (SiNW)-based tunneling field-effect transistor (TFET) using CMOS-compatible technology. With a Si p+ −i−n+ tunneling junction, the TFET with a gate length of ∼200 nm exhibits good subthreshold swing of ∼70 mV/dec, superior drain-inducedbarrier-lowering of ∼17 mV/V, and excellent Ion −Ioff ratio of ∼107 with a low Ioff (∼7 pA/μm). The obtained 53 μA/μm Ion can be further enhanced with heterostructures at the tunneling interface. The vertical SiNW-based TFET is proposed to be an excellent candidate for ultralow power and high-density applications. Index Terms—Gate-all-around (GAA), top-down, tunneling field-effect transistor (TFET), vertical silicon nanowire (SiNW). I. I NTRODUCTION T HE TUNNELING field-effect transistor (TFET) has emerged as a promising device candidate for ultralow power applications [1]–[16], as it can offer a low leakage current (Ioff ), weak temperature dependence, and, more importantly, a subthreshold swing (SS) not limited to kT /q. On the other hand, silicon nanowires (SiNWs) with a gate-all-around (GAA) structure provide volume inversion of the thin silicon body and excellent gate electrostatic control, resulting in immunity to short-channel effects and high transconductance [17]. In addition, vertical GAA SiNW MOSFETs, where the SiNW was fabricated by either chemical synthesis [18] or using fully CMOS-compatible technology [19], have been demonstrated. In this letter, by marrying these two technologies, a highly scalable vertical SiNW TFET is fabricated for low-power and high-device-density applications. The vertical SiNW platform is ideal for TFET fabrication, as source and drain implants can be independently controlled without lithography. It is interesting to note that the carbon-nanotube TFET with GAA has also been reported mainly by simulation to provide high Ion and low SS [14], [15]. In this letter, with Si p+ −i−n+ tunneling junction, the TFET with a gate length of ∼200 nm exhibits a good SS of ∼70 mV/dec, superior drain-induced barrierlowering (DIBL) of ∼17 mV/V, and excellent Ion −Ioff ratio Manuscript received February 3, 2009; revised March 23, 2009. First published May 27, 2009; current version published June 26, 2009. The review of this letter was arranged by Editor B.-G. Park. Z. X. Chen and H. Y. Yu are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, and also with the Institute of Microelectronics, A∗ STAR, Singapore 117685 (e-mail: hyyu@ntu.edu.sg). N. Singh, N. S. Shen, R. D. Sayanthan, G. Q. Lo, and D.-L. Kwong are with the Institute of Microelectronics, A*STAR, Singapore 117685 (e-mail: navab@ime.a-star.edu.sg). Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/LED.2009.2021079 Fig. 1. Vertical SiNW TFET process flow. (a) Nitride hard-mask definition on p-substrate. (b) Nanowire etch using deep RIE. (c) Vertical implant to define n+ region. (d) HDP oxide nonconformal deposition and (e) DHF etch-back. (f) Gate oxide growth, poly-Si gate deposition, and patterning. (g) HDP oxide deposition and DHF etch-back. (h) Isotropic etch of poly-Si tip. (i) Nanowiretip implantation. (j) Aluminum contact formation. Fig. 2. TEM image of a vertical SiNW TFET with large diameter (∼750 nm) showing a gate length of 200 nm and a bottom HDP oxide thickness of 80 nm. The inset shows a SEM image of a vertical SiNW TFET after nanowire etching (diameter of ∼70 nm). of ∼107 with a low Ioff (∼ 7 pA/μm). Given the smaller band gap of Ge, the Ion of 53 μA/μm can be further enhanced with heterostructures (e.g., SiGe) at the tunneling interface, as shown in simulation [7]–[12] and experimental [9] data. II. D EVICE F ABRICATION The fabrication process is schematically shown in Fig. 1. A nitride hard mask was first patterned on 8-in bulk Si wafers 0741-3106/$25.00 © 2009 IEEE Authorized licensed use limited to: ASTAR. Downloaded on July 9, 2009 at 02:01 from IEEE Xplore. Restrictions apply. CHEN et al.: DEMONSTRATION OF TUNNELING FETs 755 Fig. 3. (a) Device characteristics obtained from MEDICI simulations with varying diffusion characteristic length, Y.CHAR, of the p+ doping profile at the p+ −i junction. (b) Id –Vg and (c) Id –Vn+ characteristics of a vertical SiNW TFET with diameter of 70 nm, gate length of 200 nm, and gate oxide thickness of 4.5 nm. (d) n-TFET transfer characteristics with Vn+ = 0 and Vp+ < 0, showing a Vt shift with Vp+ . (p-type, ∼1015 cm−3 ) by nanodots defined lithographically using a 248-nm KrF scanner. This was followed by SiN etch [Fig. 1(a)] and 400-nm Si etch using deep RIE [Fig. 1(b)]. Thermal oxidation at 1000 ◦ C and DHF etch-back was done to smooth the wire surface and to reduce the nanowire diameter. Vertical nanowires with diameters of 30–800 nm were obtained. A vertical As implant and activation was done to dope the substrate and the bottom 80 nm of the nanowire n+ [Fig. 1(c)]. Nonconformal high-density plasma (HDP) oxide deposition [Fig. 1(d)] followed by DHF etch-back [Fig. 1(e)] was performed to cover only the bottom 80 nm of the wire (up to the n+ −p junction) before a 4.5-nm gate oxide was grown and poly-Si was deposited, implanted with BF2 (∼1019 cm−3 ), and patterned to form a gate extension pad [Fig. 1(f)]. HDP oxide deposition and DHF etch-back was once again used to expose only the top of the wire covered with poly-Si [Fig. 1(g)]. The oxide thickness would determine the resulting gate length as the exposed poly-Si was then isotropically etched using RIE to expose the nanowire tip [Fig. 1(h)]. A BF2 implant at a tilt of 45◦ was done from four orthogonal directions to form the p+ region [Fig. 1(i)]. To prevent counterdoping of the poly-Si gate, the same dopant type is used for the gate and top region. Finally, a layer of HDP oxide is added before contact and metal formation using aluminum [Fig. 1(j)]. The TEM image of the fabricated device shown in Fig. 2 was taken on a wider nanowire (diameter of ∼750 nm) for ease of sample preparation, showing the well-defined gate length of 200 nm. The inset of Fig. 2 shows a vertical SiNW with diameter of ∼70 nm. III. R ESULTS AND D ISCUSSION TFETs are essentially gated p+ −i−n+ diodes working under reverse bias and can operate as n- or p-TFETs. By controlling the i region with a gate, a tunneling barrier can be created either at the p+ −i (n-TFET, Vg > 0) or n+ −i (p-TFET, Vg < 0) junctions where carriers are able to tunnel through [16]. The reverse-biased p–i–n diode gives the TFET a low OFF-state diffusion current. The TFET fabricated in this letter was found to have poor p-TFET characteristics, largely due to the more graded junction at the bottom tunneling (n+ −i) interface, compared to the top interface (p+ −i), which is caused by the larger thermal budget applied after the vertical implant. This results in a much wider depletion region at the tunneling junction. MEDICI simulations of the vertical SiNW TFET were performed to study the effects of junction abruptness on device performance. The characteristic length of the doping profile at the p+ −i junction, modeled as a Gaussian function, is varied. In MEDICI, the characteristic length parameter, or Y.CHAR, is defined as the length where the dopant concentration decreases by 1/e. Based on the MEDICI simulations [Fig. 3(a)], the device performs poorer, with high Vt , SS, and low Ion , as the doping profile of the tunneling junction is more graded, i.e., Y.CHAR is larger. The results agree with that of [13]. Therefore, the focus in this letter will be on the n-TFET performance. Shown in Fig. 3(b) and (c) are the n-TFET Id –Vg and Id –Vn+ curves, respectively. These characteristics were obtained from a vertical SiNW TFET with diameter of ∼70 nm, gate oxide thickness of 4.5 nm, and gate length of 200 nm. Excellent Ion −Ioff ratio at Vn+ = 1.2 V is observed (∼107 ), with an Ioff (at Vg = 0 V) of ∼ 7 pA/μm and Ion (at Vg = 1.2 V) of ∼53 μA/μm (normalized with the wire circumference). The resulting high Ion and low DIBL (∼17 mV/V) for this Si TFET is a result of the excellent gate control of the GAA nanowire structure. From simulation [7]–[12] and experimental [9] data, it is believed that having an Si–SiGe interface at the tunneling Authorized licensed use limited to: ASTAR. Downloaded on July 9, 2009 at 02:01 from IEEE Xplore. Restrictions apply. 756 IEEE ELECTRON DEVICE LETTERS, VOL. 30, NO. 7, JULY 2009 R EFERENCES Fig. 4. Band diagrams of a TFET under (a) zero bias, and n-TFET operation with (b) |Vp+ | = 1 V and (c) |Vp+ | = 1.5 V, illustrating the Vt shift with |Vp+ |. Not to scale. junction can further improve the drive current. The obtained SS of 70 mV/dec is beyond the limit of kT /q (≈60 mV/dec), which is likely due to the tunneling junction (p+ −i) not being perfectly abrupt. The n-TFET Id –Vg characteristics with Vn+ = 0 and Vp+ < 0, as shown in Fig. 3(d), shows a Vt shift with Vp+ . This can be explained using Fig. 4. Since the p+ −i−n+ diode is always kept reverse-biased, i.e., Vn+ > Vp+ , an n-TFET (Vg > 0) can operate at Vn+ > 0 or Vp+ < 0, with the other terminal grounded. An n-TFET operating with a |Vp+ | of 1 V, for example, requires a Vg of 1 V to form a tunneling barrier with a certain barrier width [Fig. 4(b)]. If |Vp+ | is increased to 1.5 V, a Vg of only 0.5 V is required to form a tunneling barrier with the same barrier width [Fig. 4(c)], effectively reducing Vt by 0.5 V. This shift in Vt has been observed in [6]. IV. C ONCLUSION The highly scalable vertical SiNW TFET has been demonstrated and has shown to have a high Ion −Ioff ratio and a fairly high Ion of 53 μA/μm. Such a device is ideal for lowpower high-density applications. It is believed that a SiGe layer can be added at the tunneling interface to further enhance Ion . ACKNOWLEDGMENT The authors would like to thank all the staff of the Semiconductor Process Technology Laboratory, IME, for their help in wafer processing. H. Y. Yu would like to thank the support from a Nanyang Assistant Professorship. [1] C. Hu, “Green transistor as a solution to the IC power crisis,” in Proc. 9th Int. Conf. Solid-State Integr. Circuit Technol., 2008, pp. 16–20. [2] W. M. Reddick and G. A. J. Amaratunga, “Silicon surface tunnel transistor,” Appl. Phys. Lett., vol. 67, no. 4, pp. 494–496, Jul. 1995. [3] M. Born, K. K. Bhuwalka, M. Schindler, U. Abelein, M. Schmidt, T. Sulima, and I. Eisele, “Tunnel FET: A CMOS device for high temperature applications,” in Proc. 25th Int. Conf. Microelectron., 2006, pp. 124–127. [4] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, “Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec,” IEEE Electron Device Lett., vol. 28, no. 8, pp. 743–745, Aug. 2007. [5] K. Boucart and A. M. Ionescu, “Double-gate tunnel FET with high-κ gate dielectric,” IEEE Trans. Electron Devices, vol. 54, no. 7, pp. 1725–1733, Jul. 2007. [6] P.-F. Wang, K. Hilsenbeck, T. Nirschl, M. Oswald, C. Stepper, M. Weis, D. Schmitt-Landsiedel, and W. Hansch, “Complementary tunneling transistor for low power application,” Solid State Electron., vol. 48, no. 12, pp. 2281–2286, Dec. 2004. [7] N. B. Patel, A. Ramesha, and S. Mahapatra, “Performance enhancement of the tunnel field effect transistor using a SiGe source,” in Proc. Int. Workshop Phys. Semicond. Devices, 2007, pp. 111–114. [8] K. K. Bhuwalka, J. Schulze, and I. Eisele, “Scaling the vertical tunnel FET with tunnel bandgap modulation and gate workfunction engineering,” IEEE Trans. Electron Devices, vol. 52, no. 5, pp. 909–917, May 2005. [9] T. Krishnamohan, D. Kim, S. Raghunathan, and K. C. Saraswat, “Doublegate strained-Ge heterostructure tunnelling FET (TFET) with record high drive current and < 60 mV/dec subthreshold slope,” in IEDM Tech. Dig., 2008, pp. 947–949. [10] E.-H. Toh, G. H. Wang, L. Chan, G. Samudra, and Y.-C. Yeo, “Device physics and guiding principles for the design of double-gate tunneling field effect transistor with silicon–germanium source heterojunction,” Appl. Phys. Lett., vol. 91, no. 24, p. 243 505, Dec. 2007. [11] O. M. Nayfeh, C. N. Chleirigh, J. Hennessy, L. Gomez, J. L. Hoyt, and D. A. Antoniadis, “Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions,” IEEE Electron Device Lett., vol. 29, no. 9, pp. 1074–1077, Sep. 2008. [12] A. S. Verhulst, W. G. Vandenberghe, K. Maex, S. De Gendt, and M. M. Heyns, “Complementary silicon-based heterostructure tunnelFETs with high tunnel rates,” IEEE Electron Device Lett., vol. 29, no. 12, pp. 1398–1401, Dec. 2008. [13] P. F. Wang, T. Nirschl, D. Schmitt-Landsiedel, and W. Hansch, “Simulation of the Esaki-tunneling FET,” Solid State Electron., vol. 47, no. 7, pp. 1187–1192, Jul. 2003. [14] J. Knoch and J. Appenzeller, “A novel concept for field-effect transistors—The tunneling carbon nanotube FET,” in Proc. 63rd DRC, 2005, pp. 153–156. [15] S. O. Koswatta, D. E. Nikonov, and M. S. Lundstrom, “Computational study of carbon nanotube p–i–n tunnel FETs,” in IEDM Tech. Dig., 2005, pp. 518–521. [16] W. Y. Choi, J. D. Lee, and B.-G. Park, “Novel tunneling devices with multi-functionality,” Jpn. J. Appl. Phys., vol. 46, no. 4B, pp. 2622–2625, 2007. [17] N. Singh, K. D. Buddharaju, S. K. Manhas, A. Agarwal, S. C. Rustagi, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, “Si, SiGe nanowire devices by top-down technology and their applications,” IEEE Trans. Electron Devices, vol. 55, no. 11, pp. 3107–3118, Nov. 2008. [18] J. Goldberger, A. I. Hochbaum, R. Fan, and P. Yang, “Silicon vertically integrated nanowire field effect transistors,” Nano Lett., vol. 6, no. 5, pp. 973–977, 2006. [19] B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D.-L. Kwong, “Vertical silicon-nanowire formation and gate-all-around MOSFET,” IEEE Electron Device Lett., vol. 29, no. 7, pp. 791–794, Jul. 2008. Authorized licensed use limited to: ASTAR. Downloaded on July 9, 2009 at 02:01 from IEEE Xplore. Restrictions apply.