Slew-Rate Effects in First Order Sigma

advertisement

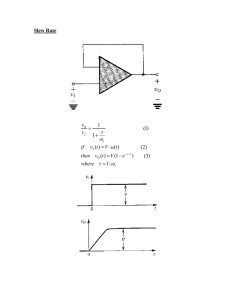

IEEE MELECON 2004, May 12-15, 2004, Dubrovnik, Croatia Slew-Rate Effects in First Order Sigma-Delta ADC’s Selçuk Talay, Günhan Dündar Department of Electrical and Electronics Engineering, Bo aziçi University, stanbul, TURKEY talays@boun.edu.tr, dundar@boun.edu.tr Abstract—This work presents the effect of slew-rate on first order, switched capacitor, Sigma-Delta (SD) analog-todigital converters (ADC). The slew-rate can be a significant problem for SD ADC’s. Thus it should be related to the input signal for accurate estimation of the error produced by the slewing amplifier. In this work, the effects of the signal histogram and its frequency spectrum have been analyzed. Different cases have been presented in order to illustrate the effect. Also, a model for estimating the error caused by the slew-rate has been proposed. helpful for further research into higher order systems. Integrator Input Output 1-bit ADC 1-bit DAC Figure 1. First order SD ADC. The second section shows the effect of slew-rate in the ADC. The following sections propose a model, which can be used to estimate the slew-rate and develop more efficient systems. I. INTRODUCTION Sigma-Delta ADC’s are gaining more and more interest due to their various properties, which allow them to be integrated into systems within various different applications. They are suitable for many applications ranging from medium speed telecommunication applications to low speed, high resolution instrumentation systems. One other advantage of this type of A/D conversion is the small number of different blocks required in their design. However, the number of possible configurations that can be built with these blocks is quite high [1] and designers commonly use only a few SD architectures. There is a lot of research focused on developing a SD design automation system that aims to assist the designer throughout their design in order to overcome this difficulty [1],[2],[3],[4]. However, systems developed by some of these researchers are basically behavioral simulators [2],[5] and they are far from being a design automation system. Even for behavioral SD simulation, the models developed should be accurate enough for an efficient design. Previously developed models are not interested in slew-rate of the SD architecture and they rather prefer to use slew-rate as a specification to be checked after a design has been initially completed or throughout the simulation. Although, this approach is still sufficient for a successfully working SD ADC, it is not suitable for an efficient design. The effect of slew-rate may lead to over estimated components, which will unfortunately yield inefficient designs such as selection of an OPAMP consuming more power and area. This work presents the slew-rate effect in first order SD ADC’s. A first order SD block model is given in Figure 1. The information presented here is believed to be II. SLEW-RATE Previous work on this topic [2], [3] mainly focused on calculating the distortion caused by the slew-rate. However, calculating the distortion is not sufficient. The effects should be estimated for an ADC with a given input signal. Thus more efficient designs can be possible. Slew-rate is effective when the amplifier in the integrator cannot supply sufficient current to the output. As a result, for a switched capacitor integrator, a wrong value of charge can be transferred to the feedback capacitance. The small changes in the input signal do not mean small changes at the input of the integrator; in other words, the voltage, the symbol V in (1) is the voltage at the integrator output. SR= d V (t ) (V/ms) dt (1) Cf Vin Φ1 Φ2 Cs X + Φ2 Φ1 - Figure 2. First order, switched capacitor integrator. In order to show this effect some brief information about the switched capacitor integrator has been given in the following paragraph. Figure 2 shows the circuit diagram of a switched capacitor integrator of a SD ADC [3]. The symbols Φi, This work was supported by TÜB TAK by project number 101E039. 0-7803-8271-4/04/$20.00 ©2004 IEEE + 95 show two non-overlapping clock signals. The charge is collected at the feedback capacitor Cf. The amplifier should be “strong” enough to transfer the charge to this capacitor. The input of the amplifier, node marked with X, is an important node. The values at this node determine whether the ADC enters a slew-rate condition or not. In order to analyse the behaviour of the system a MATLAB-Simulink model has been developed. Also, the model of the non ideal integrator has been integrated into Simulink which represents the nonidealities such as capacitor mismatch, finite amplifier gain, gain error and so on. The subblock that represents the slew rate of this integrator is given in Figure 3. However the information given in Table 1 is not complete. The following sections will add more information. Another important observation from the analysis is the dependence on the frequency of the signal. Although the slew-rate definition seems to be directly related to the frequency, this is not the case in the analysis. The frequency of the signal does not have significant effect in the total error produced by the slew rate. Different input signals have been given as an input to the model. Results showing the effect of the frequency are given in Figure 4 and Table 2. TABLE II MSE FOR TWO DIFFERENT FREQUENCIES Period (number of samples) Mean square error Fig 4a 160 Samples 6.335e-006 Fig 4b 80 Samples 6.156e-006 1 Amplitude 0.5 0 -0.5 -1 150 200 250 1 300 Samples 350 400 450 500 Amplitude 0.5 0 -0.5 Figure 3. Slew-rate block of Simulink Model. -1 The block in Figure 3 uses a linear model for slew-rate. The block can be modified and the linear model can be replaced by its more complex model such as tanh(x). The developed MATLAB model was used to analyze the behavior of the SD ADC with different input signals that vary by their histogram and frequency spectrum. The results showed that if the value of the input signal is nearly half of the maximum input voltage, possibility of errors due to slewing is maximum. In other words, if the number of slewing conditions, which is the number of samples when slewing errors occurs, has been observed for various different DC voltages, it can be seen that the values close to the mid level of the input range result in higher number of slewing conditions. Table 1 summarizes some of these results for an input range from –1V to 1V. 5.0% 0.1V 89.9% -0.2V 79.8% -0.9 5.0% 120 140 160 180 200 220 240 Figure 4 shows the inputs and the outputs, which are converted back to analog by ideal DAC. This figure also represents the effect of the frequency. Even though the frequency has been doubled, the MSE has only changed by less than 3%. These results are achieved when the slewing condition is symmetric for rise and fall of the signal. The results show that the frequency of the signal does not effect the slew-rate distortion. Figure 5 shows the effect of slew-rate with different slewing conditions. The increase in the number of samples that the integrator could not succeed in settling to its desired value, which is also expressed as number of slewing condition, with the frequency can be ignored. The total difference, as shown in Figure 5, is less than 4% for 200% increase in input signal frequency. Figure 5 shows the ratio between the number of error conditions to the total number of samples (RE/T) for different slewing conditions (RC) when the frequency is increased 8 times. The horizontal axis shows the ratio between the output voltage that OPAMP can supply within a sample time and maximum voltage possible at Percent of slewing conditions 0.9V 100 Samples Figure 4. Ramp input for two different frequencies showing the ideal input, ADC output which is slewing and the error between them. TABLE I INPUT LEVELS AND SLEWING CONDITIONS Input Level 80 96 0.4 Figure 1 shows the block diagram of the first order SD ADC. If the input is x[n], output y[n], input of the quantizer w[n] the following equations can be written: RE/T 0.3 y[n]=sgn( w[n] ) w[n]= w[n-1] + x[n-1] – y[n] 0.2 0.1 which leads to: 0 1 0.9 0.8 0.7 w[n] - w[n-1] = x[n-1] – sgn( w[n] ) 0.6 RC (RE/T) for 5 different slewing conditions for increased frequency. node X in Figure 2. Each of the five curves represent different frequencies where the lower values correspond to slower OPAMP’s and the value 1 on the x-axis stands for situations in which the OPAMP will never slew. The number of slewing conditions is very important. The distortion at the output of an ADC can be represented by MSE of the error, where error is the difference between the ideal signal and the converted signal as illustrated in Figure 4. On the other hand it is easier to estimate the slewing condition from the model. The square of the number of slewing conditions is actually linearly proportional to MSE. This relation can be observed from Figure 6. The horizontal axis shows the square of the ratio that is the number of slewing condition occurred over the total number of samples. Three different curves represent different slew rate conditions. -6 x 10 MSE 2.5 2 1.5 1 0.5 0 0 0.02 0.04 0.06 0.08 (3) The left side of the expression in (3) actually shows the difference of the current output of the integrator with the previous output, which causes slewing condition. If the difference is larger than the corners defined in linear slew-rate characteristic, slewing condition occurs. This equation also represents the reason why mid level inputs may cause more slewing conditions. The output of the DAC, which has been represented by the signum function, will have nearly equal number of –1 and +1 for medium level signals and is similar to a square wave oscillator. Thus, smaller x[n] values will bring large number of slewing conditions in a system which has lower slew-rate limits. However, if input has values closer to the limits the DAC output will be either –1 or +1 most of the time. Since the negative feedback tries to compensate, the input and the DAC output will have opposite signs. Thus, the difference between them will bring smaller differences most of the time. However, it will also present a large difference for small amount of time. The simulations have shown that it was 5% of the total samples as it was stated in Table I. Also, slew-rate requirement becomes more stringent. This is the case when both input and the DAC output have the same sign. The information presented here shows that for a system which has a signal histogram having peak values at center and which has a lower slew-rate level will have large number of slewing conditions. This type of input signals requires careful amplifier design. The slew-rate capacity should large enough. Also capacitor values should be selected as small as possible to relax the slewrate requirements. On the other hand, if the signal histogram has values spread all over the input range or having its peak values near the limits, the system may tolerate smaller slew-rate values. Although, this approach will bring error to the system it can be tolerated for mid level resolutions. Depending on the application, this approach may relax the tight limits on the amplifier specifications. Another important result of this analysis is that, the sinusoidal inputs may not be the correct input for testing the slew-rate effect on SD ADC. Since the histogram of the sinusoidal input is mainly collected at the limits of the input spectrum, possibility of slew-rate conditions is very small. More suitable input will be a signal with Gaussian like histogram. Figure 5. Ratio of error conditions to the total number of samples 3 (2) 0.1 (RS/T)2 Figure 6. MSE vs. square of the ratio of slewing conditions to the total sample number. III. SLEW-RATE MODEL Previous sections show the simulation-based information. This information can be obtained from analytical expressions. For a system where the reference levels are –1V and 1V, the DAC output can be expressed by a signum function. Thus, by using the discrete time definitions, an expression for the node X in Figure 2 can be found. However, this expression should be in terms of input such that it allows us to estimate the slewing condition from the input. If the histogram of the input signal is known, the total number of slewing occurrences can be estimated which can lead to the estimation of total error that will add up at the output. IV. EXAMPLE The number of slewing conditions should be defined in terms of input signal in order to estimate the number of 97 taking the value that causes slewing conditions within the input range affecting the slewing is 39%. This is very close to the real value, 40%. In order to test the model some other inputs were applied. The above example is a synthetic example and may not represent real life signal characteristics. Thus, a speech file was given as input. The results showed that the analytical calculations yielded an error less than 5%. Also, some other input signals such as sum of several sine waves were applied to the model and the error between the actual slewing condition number and the calculated slewing condition number was observed to be between 1% to 3% for all different inputs. These examples show that this approach is suitable for quite accurate estimations of slewing conditions, which may be used by designers. Since this approach is only related to the input histogram and DC level of the signal, the calculation time is quite small. slewing conditions. This information then, can be converted to the MSE value with the conversion presented in Figure 6. Although the expression given in (3) summarizes the relation, some numerical results will clarify the situation. For an input signal limited by –1V to +1V, the maximum difference at the node X is basically the maximum of the input signal ±1 from (3); that is if the maximum value of the input signal is ±0.4V, the maximum difference will be –1.4V and +1.4V. For an example design, which allows up to 1.12V per each transition, (3) gives the following values: 2.12V 0.12V (4) -2.12V -1.12V= xlim ±1 = -0.12V These limits determine where the slewing errors start. For input signal values exceeding 0.12V and –0.12V, slewing errors start, which gives a coarse estimate of the number of slewing conditions. For input samples with values greater than ±0.12V such as 0.3V, there are two possibilities according to the digital output. One is 1.3V and the other is –0.7V. Only 1.3V will introduce a slewing condition. For values such as 0.1V there will be no slewing. If the output node has equal possibility of taking –1 or +1 values, which is a coarse estimation, the number of slewing conditions will be equal to the half of the number of samples having values greater than ±0.12V. For our example, the total number of samples is 8192, and number of samples with smaller values than ±0.12V is 2604. If the possibility of the output to take the value, which causes the slewing condition, is 50%, the total number of slewing conditions should be 2794. The MATLAB simulations showed that the real value for slewing conditions is 2301. The error in this approach is nearly 20%. Although this value may give an opinion on the order of magnitude of the problematic situations, the number should more accurate. The reason of this problem is basically taking the possibility of the digital output as 50%. If the possibility is 50%, this means that the average of the input is 0, since the digital output actually shows the average of the input signal. In the given example, it can be observed that the possibility of values causing slewing conditions is less that 50%, actually 40%. Since the limit of the effective range has been defined and the average value of the input signal can be calculated in order to get the ratio of ±1 values at the output, an accurate estimation can be calculated. For the example presented in this section the input signal is a sawtooth signal with ±0.4V of maximum values. The possibility of 1.12V= xlim ±1 = V. CONCLUSION In this work we presented the effect of slew-rate on first order switched capacitor, SD ADC. Also analytical expressions were given in order to clarify the effect. Results selected from various simulations have also been presented. The effect of slew-rate can be very problematic for some applications and if the designer has the required information about the input signals, more efficient circuits can be designed. The information presented here can also be helpful for researchers developing design automation systems for ADC’s [6]. REFERENCES [1] [2] [3] [4] [5] [6] 98 S. R. Norsworthy, R. Schreier & G. C. Temes, Delta-Sigma Data Converters: Theory, Design, and Simulation, IEEE Press, 1998. Malcovati P.et. al., “Behavioral Modeling of Switched-Capacitor Sigma–Delta Modulators” , IEEE Transactions on Circuits and Systems I, vol. 50, no. 3, pp. 352-364, March 2003. F. Medeiro, B. Perez-Verdu and A. Rodriguez-Vazquez, TopDown Design of High-Performance Sigma-Delta Modulators, Kluwer Academic Publishers, Netherlands, 1999. K. Francken, M. Vogels, E. Martens and G. Gielen, “DAISY–CT: A High–Level Simulation Tool for Continuous–Time ∆Σ Modulators”, DATE’02, 2002. R. Castro-Lopez, F. Medeiro, B. Perez-Verdu and A. RodriguezVazquez, “Behavioral Modelling and Simulation of Σ∆ Modulators Using Hardware Description Languages”, DATE’03, 2003 S. Talay and G. Dündar “High Speed Design Tool for Flash and Pipeline ADC’s” ECCTD 2003, Krakow, Poland, September 2003