Fulltext - ETH E

advertisement

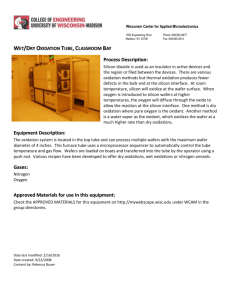

DISS.ETHNo. 13463

An Industrial CMOS

Process Family for

Integrated Silicon

XL/11 k3 VyxVk3

A thesis submitted to the

SWISS FEDERAL INSTITUTE OF TECHNOLOGY ZURICH

for the

Doctor

of

degree

of

Natural Sciences

presented by

Thomas Müller

Dipl. Phys. Universität

Konstanz, Germany

Born April 12, 1965

in

Dresden, Germany

accepted

on

(he recommendation of

Prof. Dr. H. Balles,

Dr. G.

Kissinger,

supervisor

co-examiner

Dr. O. Brand, co-examiner

1999

Contents

Abstract

I

Zusammenfassung

3

Introduction: Silicon Microsensors

5

5

LI

Status and

1.2

Silicon Microsensor Fabrication

1.3

Smart Silicon Sensors

1.4

IC Process

1.5

Major Results

12

1.6

Outline of the Thesis

13

Perspectives

Technologies

6

8

9

Technologies

Adaptation of CMOS for Anisotropic Etching

with

2.1

Electrochemical Etch-Stop

Wafer Contact Network for the

Application

(ECE)

of the

16

Electrochemical Potentials

22

of the Wafer Back

2.2

Preparation

2.3

Implementation

of the

15

Adaptive Steps

into the Production Flow

26

MlCROMACHlNING

29

Using ECE

for

Micromachining Using

3.1

Setup

3.2

Micromachining

of

29

ECE

Fully CMOS Processed Wafers

34

37

Fabricated Devices

4.1

Silicon

37

4.2

N-well Based Island Structures

Diaphragms

41

4.2.1

Thermal Isolation of Circuits

4.2.2

Soft Contacts for

Improved

N-well Structure

41

Edges

44

Contents

Manufacturability and Yield

49

5.1

Function of Contact Network

49

5.2

Stress of Dielectric

53

5.3

Design

5.4

Polymer Coatings

Layers

Rules

54

57

Compatibility Issues Between Sensor-

and

IC

Device Technology

63

6.1

Quality

6.2

Nncleation and Growth of

6.3

Influence of Bulk

6.3.1

of Wet Etched Cavi ti es in Processed CMOS Wafers

Crystal

Back Mask

of

64

Oxygen Precipitates

Defects

Underetching

the

on

and

Quality

67

of Etched Cavities 74

Roughness

{111} Side-Walls

77

6.3.2

Generation of Bulk Microdefccts

6.3.3

Correlation Between Bulk

During

CMOS

Processing

Crystal Defects and Defects

in

Side-Walls

6.3.4

81

Morphology

of Craters in

{111} Side-Walls of Etched

Cavities

6.4

6.5

83

6.3.5

Analysis

6.3.6

Conclusive Remarks

External

of

Gettering

Anisotropically

Etched

(Quality

{100} Silicon Surfaces

of Wet Etched

Cavities)

for Wafers with Reduced Interstitial

6.4.1

Polysilicon

6.4.2

Back Side

6.4.3

Conclusive Remarks (External

Influence of

78

Oxygen

Back Sides

Concentration

88

90

93

Damages

Doping

87

99

on

Gettering)

104

Anisotropic Etching

105

Summary and Outlook

107

References

109

Acknowledgments

121

List

123

of

Abbreviations

Curriculum Vitae

125

/tlJjS 1 MAC 1

An industrial fabrication

technology

for

CMOS-integrated

silicon microscnsors

To this

end, commercial 2 pm and 0.8 pm CMOS device

technologies of Austria Mikro Systeme International AG, Unterpremstätten, Aus¬

developed.

has been

tria

were

adapted

anisotropic etching

adaptive

tact

prepare for

to

of silicon with

process steps include

post-processing micromachining using wet

an electrochemical etch-stop. The developed

the formation of

(1)

a

contact

network and

a con¬

application of the electrochemical potentials to the sensor struc¬

(2) the planari/ation of the wafer back, and (3) the deposition of the etch

on wafer back. Only standard submicron resolution photolithography and

field for the

tures,

mask

deposition steps

of advanced

CMOS

processing were used. Therefore, the

method can be applied to IC device technologies irrespective of their minimum

feature size or the wafer diameter used. Implementation into, e.g., 0.25 pm

device technologies processed on 200 mm wafers is possible with only minor

changes.

integrated microsystems were fabricated using the adapted CMOS pro¬

cesses and micromachining, e.g., ultrasonic sensors, force sensors for atomic

force microscopy co-integrated with fully differential low noise amplifiers, and

Several

chemical

A

new

sensor

systems for the detection of volatile organic compounds.

silicon wafer

oxygen and external

cesses.

tion

It

was

starting

material with reduced concentration of interstitial

gettering

found that bulk

strongly degrade

the

has been introduced for the

crystal

quality

defects

generated

adapted

CMOS pro¬

due to oxygen

of structures obtained

by

wet

precipita¬

anisotropic

etching. The reduction of the initial concentation of interstitial oxygen in the

wafer starting material from around 8-1017cmT3 to 6.0 6.9-1017cmT3 led to a

strongly improved quality of the fabricated structures due to low bulk crystal

defect generation.

-

Since wafer material with reduced

density

of defects has low internal

gettering

capability,

gettering

gettering capability of polysilicon back sides and mechanical damages at the wafer back were

investigated at

various stages of CMOS processes by monitoring the density of crystal defects at

the wafer back. Only crystal defects resulting from a hard mechanical damage

external

was

evaluated. The

1

Abstract

were

result,

of 6.0

found to be stable and

a

-

silicon wafer

6.9-10

starting

crrf° and

a

gettcring-active during

material with

hard mechanical

an

2

processing.

As

a

interstitial oxygen concentration

damage

cation of CMOS-integrated silicon microsensors

CMOS

was

using

the

employed

for the fabri¬

developed technology.

Zusammenfassung

In dieser Arbeit wird eine modifizierte CMOS Prozessfamilie

im Rahmen einer

Nachprozessierung

stellt werden können. Als

anisotropes

sem

integrierte

Fabrikationstcchnologic für die

Nassätzen mit einem elektrochemischen

Mikroscnsoren

herge¬

Mikrosensorcn wurde

Ätzstop eingesetzt.

Zweck wurde eine 2 (um und eine 0.8 pm CMOS

Mikro

von

der Wafer

mit der

vorgestellt

Technologie

Systeme International AG, Unterpremstätten, Österreich um

Zu die¬

der Austria

eine Reihe

Fabrikationsschritten erweitert. Die zusätzlichen Schritte umfassen (l) die

Herstellung

eines leitenden Netzwerkes auf den Wafern für die

den elektrochemischen

Ätzstop notwendigen Potentiale, (2)

Kontaktfeldes auf den Wafern für die elektrische

die

Verteilung

der für

Herstellung

Kontaktierung

eines

der Wafer wäh¬

Ätzens und (3) das chemische Polieren der Rückseite der Wafer sowie

das Abscheiden einer Siliziumnitridschicht als Ätzmaske. Um die Kompatibilität

rend des

der zusätzlichen Schritte mit anderen

Prozesstechnologien und die Prozessierbarkeit auf anderen Waferdurchmessern zu gewährleisten, wurden ausschliesslich

Standard Submikrometer-Photolithographie und -Depositionsschritte verwendet.

Eine Reihe von integrierten Mikrosensorcn und -Systemen wurde mit der entwikkelten

Sensorprozesstechnologie hergestellt, u.a. Ultraschallsensorcn, integrierte

Kraftsensoren für Rasterkraftmikroskope und chemische Sensorsysteine zur

Detektion leicht flüchtiger Gase.

Ebenfalls im Rahmen dieser Arbeit wurde ein

für die

Sensorprozesstechnologie

tung, dass

nass

sehr schlechter

gefunden,

die

entwickelt.

geätzte Strukturen

m

CMOS

neues

Silizium Wafer Startmaterial

Grundlage dafür war

prozessierten! Wafer

geometrischer Qualität sind. Als Ursache

die Beobach¬

Material

von

wurden Kristalldcfekte

Sauerstoffausscheidungen im Inneren der Wafer während der

Hochtempcraturschritte der Prozesse erzeugt werden. In IC Prozessen werden

Sauerstoffausscheidungen und Kristalldcfekte zum Gehern von Verunreinigun¬

an

gen benutzt. Eine

Sauerstoffgchalten

ten

Untersuchung

der

von

Wafern mit verschiedenen

in CMOS Prozessen

Sauerstoffkonzentration

Qualität

des Verhaltens

von

6.0-

ergab, dass Material mit einer reduzier¬

6.9-10l7cnfJ zu einer stark verbesserte

geätzten Strukturen führt. Da dieses Material

Defektdichte aufweist, ist die interne

Getterwirkung

stark

eine

geringe

abgeschwächt.

Darauf¬

aber

nur

hin wurden verschiedene Methoden des externen Getterns mit

Polysilizium-

3

Zusammenfassung

schichten

auf

der

Rückseite

der

Waler

(kontrolliertes Beschädigen der Rückseite

führen)

kung

untersucht. Bei diesen

Dichte

bleibt nach den

von

Wafer,

um

Damages

Kristall defekte einzu¬

Untersuchungen zeigte sich,

chung

für die

6.0

-

getteraktiven Defekten

Hochtemperaturschritten

starken mechanischen

4

der

mechanischen

mit

class die GetierWir¬

bei beiden Methoden im Verlauf der CMOS Prozesse stark nachlässt. Eine

signifikante

von

und

Damage.

Als

6.9-10

der Rückseite der Wafer

der Prozesse

Ergebnis

Sensorprozesstechnologie

an

nur

wurden in

Wafer mit einer

cirf° und einem harten mechanischen

ver¬

auf Wafern mit einem

Folge

dieser Untersu¬

Sauerstoffspezifikation

Damage eingesetzt.

1 Introduction: Silicon Microsensors

Introduction: Silicon

1

Microsensors

Status and

1.1

Perspectives

The world market for micro system

technology (MST) products

grow from $14 billion in 1996 to $38 billion in 2002 [1]. A

this market is held

In modern

by

sensors

automobiles,

a

for automotive

variety

of

is

employed

comfort for driver and passengers. Accelerometers

pretensioners [2].

ment around

counter

a

skirt, such

sensors

position

as

realized in the Electronic

to ensure

safely

and

used to detect crashes

or

and scat-belt

detect critical vehicle

move¬

transmission and brakes to

Stability Program (ESP)

under

development. Firing of

prevented using signals from these sensors.

a

passenger

suspension,

accelerometers

systems, such

are

employed to

initiate engine,

are

To enhance comfort for the occupants,

Low-g

share of

of Rob¬

for scat occupancy detection, child seat detection and out of

instants is

terns, active

to

[3]. Other safety applications using passive infrared and ultra¬

detection of

dangerous

significant

deployment of airbags

sensors are

its vertical axis and

ert Bosch GmbH

sonic

Yaw rate

expected

applications.

sensors

the roll-over of the vehicle and initiate the

is

as

and

parking

new

features, such

aid systems

were

as car

the

airbags

navigation

in

sys

introduced in the 90's.

employed in electrically controlled active suspension

Body Control (ABC) [4]. ABC compensates for the pitch

are

Active

and roll

during accelerating, braking or cornering of the vehicle by adjusting

damping rate of the shock absorbers. Ultrasonic transmitter/receiver systems

used for the measurement of the distance to

an

obstacle in

parking

the

are

aid systems

[5].

An advanced

microprocessor

controlled

engine management [6J requires sensors

to determine the state of the engine. Manifold absolute pressure (MAP) sensors

allow for the measurement of the partial vacuum in the intake manifold. Their

signal is used to detect the air mass flow into the engine in order to optimize fuel

5

1.2 Silicon Microsensor Fabrication

combustion. As

applied

are

In the

near

to

Technologies

part of exhaust gas catalytic

a

adjust

future,

a

the air/fuel ratio to

an

18,9]

systems, oxygen

will be

required

projects

like the

sensors

and ambitious

Highway System (AHS) [10].

Furthermore, monitoring of cabin air quality using chemical

detection of various gases, such

nals from these

sensors

of the air

damper flap

Car and

car

applications

can

supply

subsystem

fabrication

ing techniques

can

increasing

ment in

arc

are

substituting

1.2

sensors

initiate, e.g., automatic closing of the

of the vehicle

during

drive

Silicon microsensors

sensors

based

on

silicon

can

[11,12].

for the

sensors

meet

these

require¬

Silicon microsensor fabrication

measure¬

micromachining technology. Examples

crash-sensing [13], active suspension

sensors

using

a

technologies

use

rate sensors

are

vibrating cylinder [17].

Silicon Microsensor Fabrication

processing,

tunnel

a

[15,16]. Moreover, micromachincd yaw

conventional yaw rate

such

through

used for acceleration and pressure

micromachincd accelerometers for

[14], and MAP

increasing importance. Sig¬

technologies similar to intergrated circuit manufactur¬

to high volume production at low cost per device. Today,

share of the

automobiles

exhaust gas is of

be used to

mentioned above.

lead

as

for the

sensors

manufactures seek small and low-cost

ments. Sensor

an

sensors

value [7j.

optimum

of advanced distance

large quantity

for vehicle collision-avoidance systems

Automated

converter

Technologies

fabrication steps

common

in IC-

deposition, photolithography, and etching of thin films. In

addition, a number of specialized micromachining techniques have been devel¬

oped. They can generally be divided in micromachining at or close to the surface

of a silicon wafer or micromachining in the bulk of a silicon wafer.

In surlace

create the

above

to

or

as

micromachining, patterning of a grown or deposited layer is used to

sensing structure. In the case of a movable mechanical sensor, layers

underneath the micromechanical

free the

sensing

structure

layer

are

removed

(sacrificial layers)

[18].

Micromachining in the bulk offers the possibility to create three-dimensional sin¬

gle-crystal silicon microstructures for microsensor applications [19]. Especially

for mechanical sensors, single crystal silicon offers excellent material properties

120]. Bulk micromachining is usually performed by anisotropic or isotropic etch-

1 Introduction: Silicon Microsensors

ing reaching

into the interior of the wafer.

wafer front side

Wet

an

Fig.

common

bulk

with electrochemical

Silicon

1.1 shows

a

etdi-stop

micromachining technologies

electrochemical

lowing).

may be started either from the

the wafer back.

anisotropic etching

One of the

with

or

Etching

etch-stop

diaphragms for

at

p-n

junction (referred

sensors

pressure

schematic view of

Silicon

a

a

is wet

pressure

can

sensor

anisotropic etching

to

as

ECE in the fol¬

be fabricated this way.

fabricated

using

ECE. ECE

diaphragm (n-type epitaxial layer)

a#»wii»''*«tiw»Ä

P-doped

substrate

Pressure

Etched

cavity

P-N

Back mask

Fig.

(111) crystal

Cross-sectional

1.1:

pressure

cavity is

etch-stop

face

schematic

view

chip (pressure applied

sensor

created

of

a

bulk

micromachined

from the back of the

chip).

The

anisotropic etching with an electrochemical

at the p-n junction. (The deflection of the diaphragm due to

pressure is usually measured using piezoresistors located close to the

edge of the diaphragm).

is based

on

by

junction

the fact that the etch rate of silicon in aqueous

be influenced

by

a

potential

tion in silicon offers the

strongly

high

wet

between silicon and the

possibility

reduced etch rate while

to

keep

leaving

etching

the n-typc

etching

a

can

solution. A p-n

junc¬

potential

with

zone

the p-t>pe silicon at

etch rate. This way, the p-type material under

solutions

at a

potential with a

n-type layer can be seleca

7

1.3 Smart Silicon Sensors

tively

removed

resulting

in

diaphragm with the thickness of the n-type layer

[22,23]. During fabrication of a piezoresistive silicon pressure sensor, ECE is

commonly applied at the p-n junction between a n-type epitaxial layer and a

p-doped substrate wafer. After fabricating the necessary sensor components on

the wafer front, such as the implantation and the diffusion of the piezorcsistors, a

masking layer is deposited on the wafer back. The masking layer is structured by

double-sided photolithography and reactive ion etching (RIE) or wet etching

resulting in rectangular openings. Deep cavities arc etched in the wafer starting at

the mask openings. Common anisotropic etchants, such as potassium hydroxide

(KOH) or tctramethyl ammonium hydroxide (TMAH) solutions arc used. Etch¬

ing is automatically stopped at the lower surface of the n-type epitaxial layer.

Furthermore, single crystal silicon exhibits a strongly reduced etch rate in (111)

crystal direction in wet anisotropic etchants [211. Thus, all cavities have the form

of a truncated pyramid bound by 4 (11 l)-oriented crystal faces and one (lOO)-oriented crystal face.

a

Smart Silicon Sensors

1.3

A silicon

sensor

is

usually regarded

'smart1

(or integrated) when circuits for

amplification, compensation, and trimming of the raw sensor signal are co-inte¬

grated with the sensing structure on a single silicon chip [24]. This concept has

been demonstrated for pressure

lar

IC

in

sensors

already

in the late 70's

[25]. Today, bipo¬

with ECE are routinely employed for

technologies

high-volume fabrication of MAP sensors [26.27]. Other silicon sensors fabri¬

cated using this technology include, e.g., a piezoresistive acceleromcter [28].

combination

Compared to bipolar technologies, CMOS offers additional features for smart

sensors: complex logical circuits for signal conditioning, such as

digital signal

processors (DSP), analog/digital converters (ADC, DAC), microprocessor cores,

and memory

pressure

on

sensors

chip

can

based

be

on

co-integrated

smart

ECE

The

early 90's [29,30]. A

presented in 1995 [31].

instrumentation

amplifiers

and DAC's.

DSP and nonvolatile memory

recently 132].

8

sensing

CMOS technology and ECE

late 80's and

was

with the

for

structure.

were

Integrated

introduced in the

CMOS accelerometer fabricated

on-chip circuitry

Integration

compensation

of

a

of the

sensor

pressure

sensor

and calibration

using

includes

was

with

a

shown

1 Introduction: Silicon Microsensors

The

features of CMOS make the

special

opment of

chemical

concepts. As

new sensor

sensors are

subject

to

sible commercialization of the

thesis

was

focused

commercially

1.4

on

the

IC Process

The results

presented

example,

an

very attractive for the devel¬

electronic

noses

based

on

smart

extensive research [33]. In order to allow for pos¬

developed

integration

available CMOS

technology

sensor

of ECE

as a

systems, the work towards this

versatile

technology

sensor

into

technologies.

Technologies

in this thesis

the author and Austria Mikro

based

are

Systeme

on

the close collaboration between

International AG,

Unterpremslättcn, Aus¬

tria (AMSiAG) within the joint research project AMSYST funded by the Swiss

Priority Program Micro und Nano System Technology (MINAST) 134]. A num¬

ber of research

projects at the Physical Electronics Laboratory (PEL) were based

on the developed sensor technology, such as the MINAST projects PROXYST

(development of ultrasound based proximity sensors), FAMOS (development of

integrated force sensors for atomic force microscopes), and NOSE (development

of microsensors for the detection of volatile

technologies

The process

following.

Further details

technologies

boron-doped

of AMSiAG used

arc

Czochralski

wafers

were

of interstitial oxygen

organic compounds

during

this thesis

in

are

air).

described in the

available in

(CZ)

[35]. As starting material for all process

100 mm diameter, 525 pm thick,

grown,

used.

By part,

wafers with reduced initial concentration

used in order to

improve

the surface

quality of micromachined structures (see Chapter 6.3). In some cases, standard epitaxial (weakly

p-doped epitaxial layer on heavily p-doped substrates) were replaced by non-epi¬

taxial wafers with a resistivity of 14-24 Qcm.

were

For the first two wafer

runs

processed dining

this

thesis,

a

CMOS

(CBT, Device numbers (Dev.) 6927, 8331) process

nology

offers attractive features for MEMS

junction depths and an additional

Using the electrochemical etch-stop

ent

diaphragm

devices

in

thicknesses

deep

Chapter 4.2).

and

a

In

can

n-well

Fig. 1.2,

be

based

2.0 pm

was

high voltage

used. This tech¬

applications: two n-wells with differ¬

p-well inside the deep n-wcll are available.

at

the n-well/substrate

obtained.

junction,

different

Furthermore, integration of CMOS

micromechanical

structures

the main features of this device

is

possible (see

technology

are

listed

device cross-section is shown.

9

Technologies

.4 IC Process

Core process

P-substrate twin-well

Drawn channel

length

2.0 pm

Isolation method

LOCOS

Interconnect

2 metal

Layer

Gate oxide thickness

17 nm

Mask Levels

13

S

(Local

Oxidation of

Silicon)

layer (AISiCuTi)

or

51

G

S

D

G

CMOS, poly Si gate

nm

(high voltage)

S

D

G

D

'BPSG

iLp+fa y_/p+J

kP

Deep

we

N wel

CMOS in

High-Voltage PMOS

deep

N-well

Poly Si

P-Substrate

Fig.

1.2:

Field Oxide

2.0 pm

High-Voltage CMOS technology CBT (S:

MOS transistors).

gate, D: drain of

In the

course

(CYE,

Dev.

of this work, also

8654)

cross-section

platform

During

employed.

displayed in Fig.

was

The main features of this

1.3. In the

technology

future, it is planned

and

a

(CU-) and 0.8 pm BiCMOS technologies (BY-) of AMSiAG

as a

the work

on

within the research

designs

development

research and

on

IC-microsensors.

development

were

assembled

were

into

fabrication of 10 wafers. In most cases,

silicon microsensors at PEL

single design

a

design support,

were

and

processing steps required

the IC

wafers

were

developed

Micromachining

mask

provided.

The

submitted

Engineering

to

Ser¬

fabrication, and the

than 20 wafers per

more

cated. Additional

line of AMSiAG.

on

fabricated within the frame of the

vice of AMSiAG. This service includes

processed

near

projects mentioned, microsensor designs

AMSiAG. The wafers

10

technology

use

for research and

individual

advanced 0.8 pm 5 V CMOS

to

are

0.6 pm CMOS

an

source, G:

run were

for the fabrication of

fabri¬

sensors out

of

and carried out in the wafer fabrication

of wafers

was

performed exclusively

after

1 Introduction: Silicon Microsensors

Core process

Drawn channel

P-Epi

length

twin-well

0.8 pm

Isolation method

LOCOS

Interconnect

2 metal

Layer

Gate oxide thickness

16

Mask Levels

15

Fig.

1.3:

of MOS

0.8 pm 5 V CMOS

layer (AISiCuTi)

nm

technology

CYE

(S:

source, G:

gate,

D: drain

transistors).

completion

con

CMOS, poly Si gate

of IC

processing, mostly at PEL. ECE and further structuring

diaphragms by RIE were used as micromachining techniques.

of sili¬

11

1.5

Major

1.5

The

I

Results

Major Results

major

results

Integration

presented

in this thesis

are

stated below.

of ECE into industrial CMOS

A

technology

foi

technique

the

preparation

of CMOS

wafers for ECE using standard CMOS pro¬

cessing only

developed. It includes the

creation of a conducting network with a con¬

tact field (on top of the Figure) for the con*

5

<

nection

'

'

was

and

the

electrochemical

»

distribution

potentials

of

the

and the

tion and

penaliza¬

back. Using

masking of the wafer

pre-processed wafers of this kind, numerous

microsystems were fabricated, such as ultra¬

sonic sensors, force

microscopy

compounds.

and chemical

sensor

sensors

for atomic force

systems for the detection of volatile organic

II

Development of a new silicon wafer starting

co-integrated with CMOS circuits.

material for silicon

A

new

material

sensors

its

a

for

was

wafer

starting

integrated

developed. It

very low defect

dining

thus,

silicon

sensors

CMOS

silicon

exhib¬

generation

processing and,

strongly improved quality

of cavities obtained by wet aniso¬

tropic etching (right side of the

Figure compared to the left side

con

wafer

material).

Due to the low defect

gettering of impurities is supressed. As a

damage of the crystal lattice at the wafer

12

a

showing a cavity in standard sili¬

density in the new material, internal

consequence, external

back

was

introduced.

gettering using

a

1 Introduction: Silicon Microsensors

Outline of the Thesis

1.6

Following this introduction, the integration of ECE into a commercial CMOS

process family is described in Chapter 2. The micromachining of wafers using

ECE is adresscd in

presented in

co-integrated CMOS

ogy is

with

Chapter 3. A variety of devices fabricated using this technol¬

Chapter 4. Force sensors for atomic force microscopes (AFM)

are

vapors

feature

described.

size

of

circuits and

Furthermore,

n-well

based

Chapter 5, manufacturability

and

a

smart sensors

technique

organic

for the reduction of the minimum

micromcchanical

yield aspects

for the detection of

of the

is

presented.

In

developed technology

are

structures

adressed.

In the second part of the thesis

(Chapter 6). compatibility problems between

CMOS and ECE are discussed. Special attention is paid to internal gettering with

bulk microdefects used in contemporary CMOS processing. Microdefects in the

wafer bulk, such as stacking faults and dislocations used for internal gettering

deteriorate the surface quality of cavities created using ECE. Detailed investiga¬

tions of the influence of the initial concentration of interstitial oxygen of the

wafer starting material on the bulk microdefect generation and the quality of

etched cavities

and back side

result,

a new

externa]

carried out. External

were

damages

are

silicon wafer

gettering using

sive remarks and

an

a

investigated

starting

in

gettering using polysilicon back sides

order to replace internal gettering. As a

material with reduced interstitial oxygen and

back side

damage

outlook to future work

is introduced. In

are

Chapter 7,

conclu¬

aiven.

13

1.6 Outline of the Thesis

14

2

Adaptation

of CMOS for

Anisotropic Etching

Adaptation

2

with Electrochemical

of

Etch-Stop

CMOS

Anisotropic

for

Etching with

Electrochemical

Etch-Stop

In this

chapter,

the modification of

an

industrial CMOS process

family

for the

application of anisotropic etching of silicon with an electrochemical etch-stop

(ECE) is presented. The modified CMOS processes provide wafers prepared for

the connection of the etching potentials through a wafer holder with spring

loaded contacts. For the connection to the wafer holder contacts,

a

large

contact

field is created at the wafer border. A wafer-wide

to the contact field

is formed to

supply

the

conducting network connected

electrochemical potentials to all struc¬

tures to be micro machined.

The network and the contact field

thography steps performed

on

created

are

by

a

number of additional

wafer-steppers together

of the standard metallizations. Therefore, the method

photoli¬

with the

can

be

photolithography

applied to present

and future IC device

diameter. After

technologies irrespective of minimum feature size or wafer

standard IC-processing, a penalization of the wafer back and the

deposition

PECVD silicon nitride

of

a

Up to now, the method has been

(CYE) CMOS device technologies at

out.

Unterpremstatten,

In the

following,

Austria

the

masking layer on the wafer back is carried

implemented into 2 pm (CBT) and 0.8 pm

Austria Mikro

Systeme

(AMSiAG) (sec Chapter 1.4).

changes

in the process

mation and the treatment of the wafer back

for the formation of

(a)

a

method

using

a

an

cycle

International AG,

necessary for the contact for¬

explained in detail. Two methods

supply for the ECE potentials to the wafer are presented:

additional metal layer employed for the first devices proare

15

2.1 Wafer Contact Network for the

cessed

only

during

of the Electrochemical Potentials

the work towards this thesis and

standard advanced

on

Application

(b) the

formation based

photolithography using wafer-steppers.

Wafer Contact Network for the

2.1

contact

Application

of the

Electrochemical Potentials

Modern CMOS

technologies provide weakly doped n-well s diffused in weakly

or epitaxial layers. Thus, the electrochemical etch-stop technique

p-doped wafers

can be applied at

the p-n

junction

and the substrate

n-well)

have to be

electrically

between the n-well

(to be referred

[36]. However, all structural n-well

connected

together

as

structural

areas on

the wafer

and routed to the outside to

electrochemical

arise

CMOS

an

potential from a potentiostate. Difficulties

processing since wafer-stepper lithography provides

fields with

nels

containing

arc

variety

a

ment. The individual

of structures for process

step fields have, in

a

scribe channels must be

bridged by

bridges

In the

low-resistivit}

general,

a

corners

ing step

frame

(now available

of the step fields

by

a

potentials

close-up

fields

on a

routed via the first

as

a

library

metal structures

layer of

arc

a

AMSiAG). Fig. 2.1 (a)

connected to each other at the

placed

in the scribe channel. Thus,

throughout

the wafer

supplying

the

structural n-wclls and the

p-substrate. Fig. 2.2

potentials among 4 neighbor¬

completely processed CMOS wafer. The substrate potential is

metal layer while the n-well potential is routed via the second

the CMOS processes. The

during processing

connected to the

n-well and

to the

element at

view of the connection of the

may be clustered inside

16

fields, the

in the scribe channels.

schematic of the frame. The frames

(a) shows

are

align¬

electrical connection to each

suitable metal structures. The construction of

must not affect the structures

electrochemical

frame

no

and mask

connection between the step

the frames build up two contact networks

metal

monitoring

scribe chan¬

concept developed during this thesis, each step field is surrounded by

predefined

shows

modern

array of step

separated by approximately 100 pm wide

other. In order to form

these

in

the

mutual connection.

no

the step fields

Usually,

apply

of the

a

single

design

microsystem design

is

placed

inside the

data for mask fabrication. Small

frame. All structures in

a

designs

design requiring ECE

etching potentials by routing them from the frame to the

p-substrate contacts of the structures. Ohmic contacts to the structures

2

Adaptation

of CMOS for

Anisotropic Etching

with Electrochemical

Etch-Stop

Microsystem design

SL

"S

M

ir.

F

;j ,

,

(b)

(a)

lb"——"--—-— "-%

Fig.

2.1

:

tials, (b)

Schematic of

array of

step

(a)

frame

distributing

fields surrounded

the electrochemical

poten¬

connected frames;

by mutually

requiring etch-stop, grey:

etched through the openings of

black: contact network for the structural n-wells

contact network for the substrate to be

the mask at the wafer back.

miiiHi

.:

ï-îîiÀffc^-.i .:;:

ISC

.-.^'ÄSfiW

(b)

(a)

»sYy

11111111

H

1 200

pml

(a) photograph of connection of frames carrying the electro¬

chemical potentials among four neighbored step fields in a processed

wafer (Dev. CBT 6927) (SC: scribe channels), (b) for identification,

close-up of frame crossings taken from Fig. 2.1, black lines supplying the

n-well potential are removed at top right of the picture; dashed: additional

Fig.

2.2:

metal structures in the scribe channel.

17

2.1 Wafer Contact Network for the

Application

generated by heavily doped, shallow

source/drain diffusions).

are

In order to avoid short circuits of the

area on

the wafer is limited

edge free

leaving

of structures. For the

step field array is removed

on

stepped exposures of the photo

of one single step field).

of the Electrochemical Potentials

and

n-

potentials

an area

same reason,

at

with

the

p-diffusions (p

a

the wafer

excess

both metal mask levels

resist with

the

mm at

stepped

the wafer

metallization outside the

by

'free' reticle

a

edge,

width of 3

standard

n

,

additional automated

(mask for the exposure

In bulk

micromachining using ECE, a waferholder with spring loaded contacts is

commonly used to apply the electrochemical potentials to the wafer. Macro¬

scopic metallized areas large enough to ensure reliable contact to the contact pins

of the holder have to be created

identical in conventional

the wafer.

wafer-step per

contacts (to be referred

scopic

potential

field.

on

Unfortunately, all stepped fields arc

processing. Thus, the creation of macro¬

ECE contacts in the

following) to supply the

from the outside to the wafer would consume expensive area on each

Two different concepts to solve this problem arc described in the following.

Contact formation by

For the first wafer

Dcv. CBT

create

8331),

a

network

additional metal layer

processed during

runs

third metal

the ECE contacts

every step field

an

layer

this thesis

structured

[37]. Medium sized

used to connect the

were

distributing

as

by

a

contact

potentials

(Dev. CBT 6927, part of

lift-off

technique

pads (400

pm

by

from the ECE

was

used to

400

pm)

contacts to

on

the

the ECE

potentials. The etching potentials were routed from

the frames to these contact pads. The actual ECE contacts were created at the

edge of the wafer using a third metal layer. Metal lines were routed from the ECE

contacts to the medium sized contact pads of the nearest step field. In Fig. 2.3, a

photograph of a wafer processed using this technique is shown.

Exposure on a wafer aligner was used to structure the PEC VD silicon nitride pas¬

sivation layer at the end of the CMOS process in order to generate the pad open¬

ings.

The

photo

resist at the location of the ECE contacts

Therefore, bonding pads

lift-off, a negative photo resist

at this location

mask

large

schematically

chromium

development

18

shown in

areas

forming

of the resist,

a

was

not

exposed.

remain covered with silicon nitride. For

was

deposited

Fig.

2.3

and

exposed through

a

single wafer

(b). The wafer mask pattern contains

the ECE contacts

6000 A aluminum

two

during further processing. After

layer was deposited on the wafer

2

Adaptation

of CMOS for

Anisotropic Etching

with Electrochemical

Etch-Stop

Fig. 2.3:

Photograph of (a) wafer (Dev. CBT 6927) with contacts for the

application of the electrochemical potentials created by a third metal

layer, (b) mask pattern for the lift-off mask. A close-up view of the area

enclosed by a dashed rectangle in (a) is shown in Fig. 2.4 (b).

surface

formed

by low-temperature sputtering. Lift-off of

in an ultrasonically agitated acetone bath.

the aluminum

layer

The described method has two main draw backs: First, the exposure of the

vation

layer

with

wafer mask

a

Second, problems

causes

frequently

observed. As

wafer

was

piesent. In

along

the step

helped

a

result,

some

ferent

overcome

technique

to

by 400 pm

medium sized contact

pads

were

ohmic contact to n-wells and substrate of the

a

scratch with

a

wafer

prober

needle directed

the electrical connection from the ECE contacts

Photographs showing

displayed in Fig. 2.4.

Wafer-stepper-based

In order to

no

cases,

to restore

to the wafer.

are

passi¬

of several pm.

with the step coverage of the third metal at the transition

between third metal and the 400 pm

problem

varying alignment

errors

per¬

was

the

alignment

error

and the step coverage

contact formation

the difficulties associated with the third metal

create

the ECE

contacts

was

developed.

layer,

The

a

dif¬

technique

19

2.1 Wafer Contact Network for the

Alignment

error

of

of the Electrochemical Potentials

Application

passivation layer

Poor

step coverage

3rd

metal

"lULiuutinu

(a)

SS^^SHO

200 pm

'

urn

W,m^v;

Substrate

potential

N-well

potential

(a) a bonding pad and (b) the connection of

the structured third metal layer to the medium sized contact pads present

on every step field (Dev. CBT 6927).

Fig.

Photographs

2.4:

involves standard

is

of

No additional metal

layer

which has the

same

wafer-stepper lithography steps only.

required.

At the wafer

size

as

border,

a

dedicated 'contact' step field is

the other step fields. This

at the second metal mask

reticle. The

done

by

a

field

generated single

to

of the step field array

the

on

spimg-loaded

a

contacts of the

the wafer is chosen in

Fig. 2.5,

using

special

large bonding pads

contains two

field hits the wafer holder contacts. In

photo resist

second exposure of the

level of the CMOS processes

the connection of the wafer

layout

is

printed

to allow

for

wafer holder. The

way that the contact step

stepper-based

passivation layer at the

schematic of the

a

contact construction is shown.

a

'contact'

of the

Dining patterning

end of the IC process, a procédure similar to the creation of the contact field is

used to remove the passivation from the contact field: at the location of (he con¬

tact

field, the photo

in the

wafci-stepper. Again,

removed

'empty'

to

20

resist is

on

exposured through

the

excess

both metal mask levels

reticle.

Fig.

2.6 shows

a

a

special

'contact

metallization outside the

using

automated

photograph

of

a

stepped

wafer

stepped

area

exposures with

pre-processed

allow for ECE at CMOS n-wclls. The individual step field

reticle

opening'

size

is

an

in that way

is 15

mm

by

15

2

Adaptation

of CMOS loi

Anisotiopic Etching

with Electtochemical

Etch-Stop

Contact field

Microsystem design

Single

step

field

Fig.

2.5:

Schematic of the

stepper-based network construction; on top

field for the application of the electrochemical

picture: contact

potentials via spring loaded

of the

Fig.

contacts in

a

wafer holder.

Photograph of a 100 mm wafer (0.8 pm CMOS, Dev. CYE 8654)

with

pre-processing for anisotropic etching with electrochemical

etch-stop (ECE).

2.6:

21

2.2

of the Wafer Back

Preparation

mm.

If

tive die

required,

the step field size

be reduced in order to increase the effec¬

can

the wafer.

area on

The third-metal-based method for the creation of the ECE contacts

additional masks,

outside the

one

stepped

wafer mask for the

'empty'

array

on

reticle for the removal of the

the

patterning

The

wafer,

one

wafer mask for

of the third metal

excess

outside the

'contact"

reticle for the removal of the

the second method is

Additionally,

wafers must be

On the other

one

piocessed

in the

reticle, and

one

requires

excess

'contact

one

also three

metallization

opening'

expensive than the first

wafer-stepper two times more.

more

hand, the stepper-based

and

layer.

the creation of the ECE contacts

array,

three

metallization

pad opening,

stepper-based method for

additonal masks, one 'empty'

stepped

requires

one

reticle.

since the

formation

technique is only based

standard submicron resolution photolithography. The technique is not

on

restricted to the minimum feature size and wafer diameter of a particular process

technology. It can simply be applied to future IC process families. Furthermore,

the overall reliability of the additional processing is much higher.

contact

engineering wafer runs (10-20 wafers each) were processed during this

thesis. The first one (CBT, Device number (Dev.) 6927) and part of the second

Three

(CBT,

one

based

on

8331)

were

processed

with the ECE contact formation method

the third metal. The last wafer

exclusively

2.2

Dev.

with the

run

(CYE, Dev. 8654)

was

processed

stepper-based technique.

Preparation

of the Wafer Back

Anisotropic wet etching with an electrochemical etch-stop starting at the wafer

back requires a back mask. In initial tests, PECVD silicon nitride layers were

deposited directly on the back of CMOS-processed wafers using a STS 310 PC

equipment. Roughness of the wafer back, scratches, and particles deposited dur¬

ing processing deteriorated the mask quality Therefore, an in-fab spin etcher

(SEZ AG, Villach, Austria,

see

[381)

at

AMSiAG

was

used to

planarizc

the wafer

back before

cal

masking. Photographs of the wafer back before and after the chemi¬

penalization arc shown in Fig. 2.7. The method utilizes a stream of an isotro¬

pic

silicon ctchanl

of the

rotating

containing H2S04,

wafer. The wafer floats

HE

on

HNO^, EI3PO4 directed onto the

a nitrogen cushion protecting its

back

front

2

Adaptation

'

k"T<

\

'

,,

<«

«'"«•ft

••

é:j.m"'

>\

^

with Electrochemical

Etch-Stop

...

«*-..

1

I

H^

i>. \

,

*

ï1-

Anisotropic Etching

•'M^.-^'J*

't.

.

4»

»u

of CMOS for

««

4

,

.>:•>' :

'

»Si

«-•.'..

i

'ro

"Vit

y*i

'"i~

ST^^';^ ;50

•-

«s*

Fig.

2.7:

side

throughout

»

pm

50 pm

>

.

Photographs of the wafer back before (a) and after (b) the

chemical planarization. In (b) shallow sickle-shaped patterns caused by

bulk stacking faults can be observed.

the entire

routinely employed

packages

can

as a

etching

process.

last step in CMOS

Thinning

of wafers after

processing

be reduced due to the smaller thickness of the dies.

of 0.06 pmmls with

a

spatial wavelength

of

is

because the size of the die

the substrates from 525 pm to 380 pm in around 100

roughness

processing

results in

s

of

Spin-etching

a

back surface

approximately

300 pm.

The

spin-etcher has a recycling system tor the silicon etchant. The etchant is

replaced routinely after approximately 300 wafers. Tt was observed that wafers

thinned

just

exhibited

before the

an

increased

replacement

roughness

of the etchant had

a

dull appearance and

of up to 0.14 pmims. In order to determine

a

maximum number of wafers

of wafers for

wafers

sensor

already etched in the same etchant before thinning

applications, the following experiment was performed, lest

thinned from 525 pm standard thickness to

were

thickness after 0, 83, 208, 250. and 310

the

same

etchant. The surface

mechanical

roughness

profile

(production) wafers

of the test wafers

stylus profiler (P-10. KLA-Tcncor Corp.,

UBM

long

taken

380 pm

have been thinned in

was

determined

San Jose,

using

USA).

using

a

For the

optical profiler

GmbH, Ettlingen, Germany), The influence of the number of

measurement a

(Microfocus.

5

approximately

mm

scan

was

an

wafers

already thinned in the same etchant on the roughness of the test wafers is

shown in Fig. 2.8. A typical profile of the wafer back is shown in the same figure.

The profile was taken after 83 wafers being thinned using the same etchant. A

detailed description of this experiment is given in f39]. As a result of this investi¬

gation, wafers for sensor applications are not allowed to be processed if more

23

2.2

Preparation

of the Wafer Back

10 pm

(a)

0

100 mm

0

150

CO

E

CO

CO

CD

C

JZ

(b)

100

CT)

=3

O

CD

Ü

CO

H—

*—

en

50

0

100

200

300

Number of wafers etched

Fig.

2.8:

100

mm

(a)

over-all

wafer and

number of wafers

than 200 wafers

profile

of

a

(b) roughness

etched in the

already

were

chemically planarized

of the wafer back

already

etched

same

using

the

back side of

a

function of the

as a

etchant.

same

etchant.

(see Chapter 2.3,

STR).

Poor adhesion of silicon nitride

STS 310 PC

on

the

planaiized

back

using

a

frequently observed during etching in 27% KOH

Especially at the position where the wafer holder O-ring seals

equipment

solution at 90°C.

layers deposited

was

(see Chapter 3.1) press on the wafer back, a delaminalion of the nitride layer was

observed. Due to that, perforation of the wafer at the delaminated areas and

breakthrough

In contrast,

of the etchant into the wafer holder occured.

we

observed that the standard silicon nitride

0.8 pm CMOS process CYE

(see Chapter 1.4) deposited

on

passivation

the

for the

planaiized

back

2

Adaptation

of the wafers

of CMOS for

(Concept

and adhesion

was

below 1

properties

"

cm

Scratches

implemented

ticle

density

the back and

(Surfscan,

found

were

at the

layer

as

the

in

rinsing

a

a

test

wafer after

rinscr-dryer.

of silicon nitride

deposition

Data

handling

were

not

from the wafer-handler of the

the front side of the wafer.

front side of

pinhole density

part of the back end of the CMOS pro¬

particles originating

on

San Jose,

shows excellent mask¬

the front side due to front side wafer

on

observed. On the other hand,

PECVD system

etching. Therefore,

Etch-Stop

Systems Inc.,

in 27% KOH solution at 90°C. The

after 3 firs

at the wafer back was

cesses.

One PECVD system, Novel lus

much better results. The silicon nitride

USA) yields

ing

with Electrochemical

Anisotropic Etching

Fig.

deposition

were

2.9 shows the par¬

of silicon nitride

taken with

a

particle

on

counter

KLA-Tencor

wafer-handler

can

be

Corp., San Jose, USA). The 'particle image' of the

clearly seen. Particles on the frontside of the wafer may

O

/

'

(a)

(b)

o

o

w

Fig. 2.9:

(a) particle density at the front side of a test wafer after the

deposition of silicon nitride on the back (black: particles with sizes from

2.4 pm to 100 pm) and (b) shape of wafer-handler used in the PECVD sys¬

tem.

cause

problems during

photo

resist

ing

was

with

not

or

other

layers

possible.

clean

further

is

A way

wiper

processing

of the wafers

required. Complete

to remove particles

if, e.g., deposition of

removal of the

particles by

of this kind is to

wipe

rins¬

them off

with both, wafer and

wiper immersed in a sink with

deionized water. Similar particle cleaning procedures using brushes arc com¬

monly employed for after-CMP (Chemical Mechanical Polishing) -cleaning. An

a

room

25

2.3

Implementation

of the

Adaptive Steps

additional detrimental effect

processed

were

was

wafers: electrostatic

detected

on

into the

Production Flow

observed with the back side

discharge (ESD)

Chapter

phenomenon

were

Testwafers

with standard silicon

bonding tests

planaiized and coated

were

was

was

the wafer back is not

2.3

subject

to

a

Pyrex

planaiized wafers.

nitride passivation (see

wafers. An electrostatic

glass

(SB 6, Karl Suss AG, Munich, Germany). Bonding

used

at 300°C and

performed

is

carried out with the

bonded with their back to

bonding equipment

fully

5.1.

Some initial wafer

above)

of

defects with sizes of several pm

the front side of coated wafers. This

detailed discussion in

coating

a

voltage

of 500 V.

prime-grade, large

of the

Implementation

Although

unbonded

the surface

areas were

Adaptive Steps

quality

of

not observed.

into the

Production Flow

IC manufacturers

monitoring

commonly

travellers

use run

or run

sheets for controlling and

the

production. For every processing step called a location (deposi¬

tion, photolithography, etching, etc.), and every process technology, a set of

instructions is stored in

locations for

out

specified

a

a

computer system. A printout of the complete

wafer

run

is called

is attached to the wafer box and

process. Process

gram

numbers,

monitoring

are

run

as

or run

the wafers

layer thicknesses,

traveller. In order to

steps for ECE into the real world of IC

lent instruments had to be

raveller

accompanies

data, such

recorded in the

a run

manufacturing,

sheet. This

through

of

print¬

the whole

machine and pro¬

bring

run

set

the

preparation

travellers

or

equiva¬

developed.

Run Travellers

complete run traveller was developed for the 2.0 pm CMOS technology (CBT)

together with an additional metallization for the creation of the ECE contacts.

The new, adapted process called CBU includes all additional steps required for

A

ECE, such

as

contact

nalization and

formation

masking

A number of difficulties

using

the third-metal-based method and the

pe¬

of the wafer back.

arose

with this concept. First, for any other basic process

technology (0.8 pm (CY-), 0.6 pm (CU-). etc.) a new special run traveller would

have to be developed. Second, compared to other wafer runs at AMSiAG. the

number of wafers

26

processed

for ECE

sensor

applications

is

currently

rather

2

Adaptation

small.

of CMOS for

Processing

of wafers with

unnecessary holds and

Therefore, it

called

was

Special

Anisotropic Etching

waiting

decided to

Test

times.

use

special

Etch-Stop

not very well known run traveller caused

a

standard

Request (STR).

monitor parameters of

with Electrochemical

run

STR's

travellers in combination with

are

Irequenlly

a so

used at AMSiAG to

during ongoing production. An STR

contains special instructions at specified locations for specified wafer runs

(devices). It is stored in the computer system and automatically activated at the

specified locations. A dedicated STR for the adaptive steps required for ECE was

developed during this thesis. A similar STR was applicaled for the fabrication of

process steps

the 2.0 pm CMOS devices CBT 8331 and the 0.8 pm CMOS device CYE 8654.

A schematic of the STR used for ECE

preparation

with the

stepper-based

genera¬

tion of ECE contacts is shown in Table 2.1.

Table 2.1

:

Run Traveller and

Loc.

Process

1200

Initial oxidation

(Start)

and Si-nitride

Special

Test

Request

STR Instruction (condensed)

Step

dep.

-

1670

N-well

implant

mask

Inspection

stepped

of

area

from wafer

developed resist,

outer

boundary

must have at least 3 mm

of

distance

edge

-

8780

Metal I mask

Second

(stepped)

remove

excessive metallization outside

area

exposures of

photo

resist to

stepped

(see Chapter 2.1), inspection

-

8880

Metal 2 mask

Second exposure of

tact' reticle, further

resist to

remove

stepped

area

photo

resist

(stepped)

through

'con¬

exposures of

photo

excessive metallization outside

(see

Chapter 2.1), inspection

-

27

2.3

Implementation

Table 2.1

:

of the

Run Traveller and

Loc.

Process

8900

Deposition

8950

Adaptive Steps

Step

of Pas-

into

the Production Flow

Special Test Request

STR Instruction

Deposition

(condensed)

of low stress

sivatiou

CMOS,

Passivation mask

Second exposure of

see

Chapter

passivation

of 0.8 pm

5.2

photo

resist

through

opening' reticle, (see Chapter 2.1)

'contact

-

9100

Thinning

of sub¬

strates

Thinning

of substrates to 380 pm, not

200 wafers

already

etched in the

same

more

than

etchant

(see Chapter 2.2)

9200

Back mask

Deposition of

Chapter 2.2)

silicon nitride

on

wafer back

(see

-

...

9375

Electrical map

-

(End)

This STR

can

be used for different process

technologies

On the other hand, it is obvious that this solution is not

ume

28

production.

without

major changes.

satisfactory

for

high

vol¬

3

3

Micromachining using

ECE

Micromachining

CE

In this

given.

sured

chapter,

a

detailed

description

The electrochemical

using

wafers. The

test

of the setup used for

micromachining

current-voltage

characteristic of the setup is

micromachining

of

fully processed

is

mea¬

CMOS wafers is

described.

3.1

for

Setup

Micromachining Using

The conventional 4-electrode

basic setup used

methods

throughout

ECE

(4EC) setup introduced by Kloeck et.al. f40] is the

this thesis. A

general

introduction in electrochemical

be found in

(41], The n-well(s) and the p-doped bulk of the pro¬

cessed CMOS wafers form the working electrodes, an Ag/AgCl electrode is used

can

as

reference electrode and

as

counter

The

platinum

electrode. The setup is

Ag/AgCl

anisotropic

wire

partly

schematically

enclosed in

shown in

reference electrode is used to create

etchant. A 6M KOFI solution at 90°C

electrode consists of

KCl

a

electrolyte.

an

Ag

wire convered with

a

Fig.

a

glass

tube is used

3.1.

well-defined contact

was

AgCl

used in most

The

cases.

salt in contact with

the

to

a

3M

The KCl

electrolyte itself is in contact with the KOFI solution

via a semipermeable diaphragm. The potential of this electrode vs. the etchant is

given by the sum of the cell voltage of the Ag/AgCl/3M KCl cell and the diffu¬

sion voltage of the liquid junction 3M KC1/6M KOI I. The temperature dependent

cell

voltage is approximately 130 mV at 90°C. The diffusion voltage cannot

measured directly but calculations yield a \aluc of approximately 25 mV.

detailed

description

order to prevent the

ence

electrode

no

of the

depletion

current

impedance negative input

ence

electrode. The

(Platinum wire) and

Ag/AgCl/3M KC1/6M

of the KCl

should flow

of

KOH cell is

an

etching

in

electrolyte in the interior of

through it. For that purpose,

operational amplifier

operational amplifier is operated

the

given

solution in

a

be

A

[42]. In

the refer¬

the

high

is connected to the refer¬

via the counter electrode

closed-loop

mode. Therefore, the

Setup

3.1

for

Micromachining Using

^reference

ECE

O

Potentiostate

Counter

electrode

N-we

P-substrate

Fig.

3.1

Schematic of the 4EC setup used in this thesis.

:

voltages at the negative and

equal and the potential of the

reference

etchant is

are

the

positnc input

of the

reference electrode may

rents,

a

kept

with respect to the Ground.

supply

potentiostate

potentials

are

the

voltage (Vref). In this way, the potential between silicon electrodes and

regulated by shifting the potential of the etchant. The structural n-wells

connected to Ground and the p-type substrate is

(Vbias)

operational amplifier

be adjusted by varying

Operational amplifier,

voltage, and a display were integrated in

throughout the work towards this thesis. Standard

a

for the bias

used

used

at a fixed bias

for

the

driver for

a

voltage

larger

cur¬

home-built

values of (he

micromachining of wafers were Vlcl -1.5V and

Vbias -5 V. The bias current flow ing through the reverse-biased junction and the

termination of the etching of the p-substrate for Vb]as <

2.4 V were used to con¬

=

=

-

trol the function of the apparatus. In

tials in the 4EC is shown.

30

Fig. 3.2,

a

schematic of the various poten¬

3

Micromachining using

ECE

n-Si

Ground

Vb,as -2.4 V

(etch-stop substrate)

=

Passivation

p-Si at passivation

potential

Etching

V:bias

-5V

p-Si

Fig.

3.2:

Schematic of various electrodes and their

potentials in the

4EC configuration, dashed: p-Silicon at passivation potential (potential

for etch-stop). Etching of the n-silicon may be initiated if its potentia!

(Ground) is shifted to values lower than the dashed line.

Wafer holders sealed with

O-rings (EPDM, Angst

&

Pfisler, Switzerland) and

equipped with spring loaded contacts were used during the work towards this the¬

sis. Generally, the wafer holder consists of two parts, the bottom part containing

the

by

spring

a

loaded contacts and the

number of stainless steel

sealed with the

O-rings.

wafer holder press

on

If

fittings

and

The wafer is

the contact

areas

present

beginning of the work towards this

designed and built. The potential supply

teflon hose and

stainless steel

thesis,

a

fittings.

because overpressure in the etch holder caused

etching

solution may

damage

tion of the

spring

was

stainless steel holder

a

A pressure release is

is

was

required

high temperature of the

diaphragms. Later, plexiglass

by

the

used for the

improved

At

realized

were

body

of the holder. Isola¬

loaded contacts from each other is easier to realize

material. Moreover, process control

part

Chapter 2.1).

pressure release

the micromachined

(polymethylmethacrylate (PMMA))

the bottom

loaded contacts of the

the wafer (see

on

and

on

between both parts and

placed

correctly positioned, the spring

screws.

the

using

lid to be fixed

a

using

this

since the wafer holder is trans¬

parent. In initial experiments, creeping of the wafer holder material

at

the

etching

j

I

3.1

Setup

for

temperature

very

Fig.

bulky.

3.3:

Micromachining Using

was

In

ECE

observed. To avoid this, the

Fig. 3.3,

a

plexiglass

holders

were

designed

wafcrholder of this kind is shown.

Photograph and schematic

cross-section

of

a

plexiglass

waferholder.

Current-Voltage Characteristic

In order to characterize the

were

determined. P- and

tion of 6.5-10

pose. A

p4

or

etching setup, the passivation potentials and -currents

n-doped, 100 mm test wafers with a dopin° concentra-

cm° and 1-10

create ohmic contacts to

(CYE,

created

32

a

CMOS process

(CBT,

see

Chapter 1.4)

this pur¬

standard

were

the bulk of the wafers. A standard silicon nitride

Chapter 1.4) was deposited on

by patterning the silicon nitride la\er using

see

prepared for

together with a

were

n+ standard source/drain tilt fusion

aluminum metallization of

tion

cm~\ respectively,

used to

passiva¬

the wafer back. An etch mask

back side

lithography

was

and

3

reactive ion

Micromachining using

etching (RIE) giving rectangular openings

done in order to reduce the etched silicon surface

for the

of mm-size. This

and, thus, the

current

ECE

was

required

etch-stop.

scanning potentiostat (362, EG&G PARC) and electrodes

from Metrohm AG, Flerisau, Switzerland were used. Measurements were carried

out

with

using

At

A

a

a

a

potential scanning

teflon sink with

potential

of

of I mVs"

.

Etching

temperature controller (T

=

performed

90+1 °C).

was

in the dark

approximately

sivation of silicon

panied by

a

rate

occurs

0.9 V with respect to the reference electrode pas¬

and the etching is terminated. The etch-stop is accom¬

peak-shaped etch-stop current [40J. Fig. 3.4 shows the passivation

potentials and passivation currents. As to be seen, the Open Circuit Potential

a

Etching

Passivation

P-silicon

N-silicon

._.

<D

T3

C

0)

zs

iwiMwWtlWtf^WwiM»!"'

Ü

0

Vppn

2

0

Voltage

Fig. 3.4:

doped n-

vs.

Electrochemical

reference electrode

[V]

Current

Voltage characteristic of lightly

and p-silicon in KOH solution, voltages measured with respect

to the reference electrode (

Vpp: passivation potential, OCP: open circuit

potential). The standard values (see above) of Vref -1.5 and Vbias -5 V

(measured with respect to Ground) correspont to values of +3.5 V for

p-silicon and -1.5 V for n-silicon, respectively, measured with respect to

=

=

the reference electrode.

33

3.2

of

Micromachining

Fully

CMOS Processed Wafers

(OCP) and the Passivation Potential (VPP) of p-doped silicon are shifted to

slightly lower values compared to n-silicon. Similar results for KOH solution

[43] and TMAH solution [44]

3.2

After

Micromachining

receiving

to

was

an

other authors.

Fully CMOS

Processed Wafers

measured. The measurements

semiconductor parameter

the ECE contacts

istic of

by

ECE-prepared wafers from AMSiAG, the current-voltage

the junction between the p-substrate and all interconnected

structural n-wclls

a

of

obtained

the

characteristic of

using

were

on

analyzer (4156 A,

the wafer. In

ECE-prepared

Fig. 3.5,

a

wafer is shown. The

were

performed

Hewlett

in the dark

Packard) connected

typical current-voltage character¬

forward voltage drop of the diode

50

<

CD

0

-

Ü

-50

-3

-2

-1

Applied

Fig. 3.5:

Current-voltage

CYE

(Dev.

8654).

0

Bias

characteristic

[V]

of

an

ECE-prepared

wafer

is shifted to values around 0.4 V because of the the very large area of the

p-n

between

all

structural

n-wclls

and

the

substrate. A gradual breakdown

junction

can

be observed at

now not

34

approximately

understood. It

was

1.5 V

re\ersc

bias

present in wafers of all

.

This

phenomenon

engineering

runs

is up to

processed

3

during

not

the work towards this thesis. Howe\er,