A HIGH dI/dt CMOS DIFFERENTIAL OPTICAL TRANSMITTER FOR

advertisement

A HIGH dI/dt CMOS DIFFERENTIAL OPTICAL

TRANSMITTER FOR A LASER DIODE

APPROVED:

____________________________________

Martin A. Brooke, Chairman

____________________________________

Joy Laskar

____________________________________

Russell Callen

____________________________________

Thomas Habetler

____________________________________

??????

Date approved by chairman:_____________

TABLE OF CONTENTS

ACKNOWLEDGMENTS ......................................................................... iii

LIST OF TABLES .................................................................................... vii

LIST OF FIGURES ................................................................................. viii

SUMMARY

..................................................................................... xi

Chapter I

INTRODUCTION .............................................................. 1

Chapter II

BACKGROUND ................................................................ 7

2.1

Optical Interconnect Systems and Optical Media................... 7

2.2

Optical Sources ..................................................................... 10

2.3

Optical Transmitters.............................................................. 14

2.4

Eye Diagram ......................................................................... 19

Chapter III Through-Silicon Optical Interconnect Systems .................... 23

3.1

Introduction and Applications............................................... 23

3.2

Optical Devices..................................................................... 25

3.3

Single-Ended Transmitter Design......................................... 28

3.4

Single-Ended Receiver Design ............................................. 31

3.5

Two-Layer Systems .............................................................. 34

3.6

Three-Layer Systems ............................................................ 38

Chapter IV DIFFERENTIAL LASER DRIVER..................................... 41

4.1

Introduction........................................................................... 41

4.2

Differential Transmitter Design............................................ 44

ii

4.3

Simulations ........................................................................... 48

4.4

Layout .................................................................................. 52

4.5

Scalability ............................................................................. 53

Chapter V PACKAGING PARASITIC CONSIDERATION................ 55

5.1

Introduction........................................................................... 55

5.2

Background ........................................................................... 57

5.3

Modeling of the Parasitics .................................................... 59

5.4

Differential Topology ........................................................... 65

5.5

Decoupling Capacitors.......................................................... 67

5.6

Parasitic Effect Simulation ................................................... 69

5.7

Chip Layout .......................................................................... 74

5.8

Measurements ....................................................................... 76

Chapter VI A DIFFERENTIAL LASER DRIVER FOR LVDS

STANDARD......................................................................... 85

6.1

Introduction and Application ................................................ 85

6.2

Differential Transmitter Design for LVDS Standard............ 87

6.3

Simulation and Layout.......................................................... 91

Chapter VII CONCLUSIONS AND PROPOSED FUTURE

RESEARCH........................................................................... 96

6.1

Contribution ........................................................................... 96

6.2

Future Research ..................................................................... 99

6.3

Conclusions.......................................................................... 101

iii

Appendix A

BRIEF LVDS SPECIFICATION ................................... 103

Appendix B

EDGE EMITTING LASER FABRICATED IN

GEORGIA TECH ........................................................... 105

Appendix C

HSPICE INPUT CONTROL FILES AND BSIM

MODEL PARAMETERS USED IN SIMULATION..... 111

REFERENCES

.................................................................................. 143

VITA

.................................................................................. 153

iv

LIST OF TABLES

Tables

Page

1.1

List of recently published optical transmitters..................................... 3

4.1

Design specification of the differential laser driver........................... 43

5.1

The parameter values for the model of bonding wires ...................... 60

5.2

The length and width of metal strips in PCB..................................... 62

5.3

The value of parasitic model.............................................................. 64

6.1

Design specification of the differential laser driver for LVDS.......... 86

7.1

The performance comparison of the transmitter in this research

with recently published transmitters .................................................. 97

v

LIST OF FIGURES

Figures

Page

2.1

A block diagram of a typical optical communication system.............. 8

2.2

The light output versus current characteristic of Laser and LED ...... 12

2.3

An example of the LED driver circuit I ............................................. 15

2.4

An example of the LED driver circuit II............................................ 15

2.5

An example of the laser driver I ........................................................ 18

2.6

An example of the laser driver II ....................................................... 18

2.7

Characteristics of an eye diagram ...................................................... 20

2.8

SONET eye diagram mask................................................................. 22

3.1

Diagram of vertical optical interconnect system ............................... 24

3.2

Illustration of the optical device integration on Si circuit substrate .. 26

3.3

Circuit schematic of single-ended transmitter ................................... 28

3.4

The microphotograph of the transmitter with integrated LED .......... 30

3.5

The measured eye diagram of the integrated transmitter

at 155 Mbps

.................................................................................... 30

3.6

Overall circuit schematic of the receiver ........................................... 31

3.7

The microphotograph of the receiver with integrated

I-MSM detector.................................................................................. 32

3.8

The measured eye diagram of the integrated receiver at 155 Mbps .. 33

vi

3.9

Test setup block diagram for through-wafer system.......................... 35

3.10

The microphotograph of the OEIC for two-layer system .................. 36

3.11

The microphotograph of the two-layer system .................................. 36

3.12

The measured eye diagram of two-layer system at 10 Mbps............. 37

3.13

The measured eye diagram of two-layer system at 40 Mbps............. 37

3.14

Layout of the OEIC for three-layer system........................................ 39

3.15

Microphotograph of three-layer system............................................. 40

3.16

The measured eye diagram of three-layer system at 1 Mbps............. 40

4.1

Design procedure of differential transmitter...................................... 42

4.2

A differential laser driver................................................................... 46

4.3

The optimization in terms of the transistor size................................. 47

4.4

Equivalent Model of a laser diode ..................................................... 48

4.5

Transient response of 1 Gbps differential laser driver....................... 49

4.6

Temperature simulation at 27 and 200 degree................................... 50

4.7

Transient response of differential laser driver at 2 Gbps................... 51

4.8

MAGIC layout of the driver .............................................................. 52

4.9

MAGIC layout of the driver using 0.18 µm technology.................... 54

4.10

Transient response of differential driver at 10 Gbps ......................... 54

5.1

The example of the delta-I noise in a circuit...................................... 58

5.2

The PCB for the driver testing ........................................................... 61

5.3

The diagram of metal strip in PCB .................................................... 62

5.4

The final equivalent model of packaging........................................... 63

5.5

Bias current comparison between single-ended and differential

vii

drivers

................................................................................. 66

5.6

The model of the capacitor ................................................................ 68

5.7

Parasitic impedance effect simulation ............................................... 70

5.8

Output signal with the ideal decoupling capacitor............................. 71

5.9

Output signal with the real model of 10 nF decoupling capacitor..... 72

5.10

Cadence layout of the chip submitted to fabrication ......................... 75

5.11

The block diagram of the test structure.............................................. 77

5.12

Microphotograph of the chip ............................................................. 78

5.13

Test board with a bonded chip ........................................................... 79

5.14

622 Mbps pulse waveform................................................................. 82

5.15

622 Mbps eye diagram....................................................................... 82

5.16

900 Mbps pulse waveform................................................................. 83

5.17

900 Mbps eye diagram....................................................................... 83

5.18

1 Gbps pulse waveform ..................................................................... 84

5.19

1 Gbps eye diagram ........................................................................... 84

6.1

The differential amplifier for the pre-driver stage ............................. 89

6.2

The overall schematic of the driver for LVDS .................................. 90

6.3

Transient response of LVDS compatible differential laser driver

at 1 Gbps

................................................................................... 92

6.4

The layout of the overall driver for LVDS ........................................ 93

6.5

The final layout of the whole chip submitted to fabrication.............. 94

6.6

Microphotograph of the chip for LVDS compatible driver ............... 95

viii

SUMMARY

As high data rate and large throughput are necessary in telecommunication

systems, optical communication systems have become attractive solutions to cope with

bottleneck of the electrical communications. In optical communication systems, an

optical transmitter is one of the key components, where it performs as the interface

between the electronics and the emitters. It is very challenging to design optical

transmitters since its requirements of large output current and high speed are

contradictory, necessitating a large driving signal and large output transistors.

To date, the majority of optical transmitters have been designed using GaAs HBT

or GaAs MESFET due to wider bandwidth and good quality of passive components.

However, the standard digital CMOS technology provides advantages such as low power,

low cost of fabrication due to high yield, and a higher degree of integration. Thus, Si

CMOS technology, which is well known for low cost and high density is preferred for

design of optoelectronic circuitry.

This thesis describes the development of a high dI/dt differential transmitter

meeting greater than 1 Gbps data rate for free-space optical communication. Since the

performance of the system is limited by unwanted packaging parasitics as the data rate is

increased, the equivalent circuit model of parasitics is developed and incorporated in the

design process. To overcome the effect of parasitics, the solution using a decoupling

capacitor is suggested and verified in the simulation and measurement. To test optical

transmitters, chip-on-board (COB) technology is employed and printed circuit board

(PCB) is designed and manufactured for it.

In addition, the optical transmitter compatible with low-voltage differential signal

(LVDS) that is one of the IEEE standards is introduced. The simulation results show that

the transmitter can meet the 1 Gbps data rate.

ix

1

CHAPTER I

INTRODUCTION

As high data rate and large throughput are necessary in telecommunication

systems, optical communication systems have become attractive solutions to cope with

bottleneck of the electrical communications [1-6]. Compared to the conventional

electrical counterparts, optical communication can provide larger bandwidth, smaller

channel crosstalk, shorter interconnection delays, and lower levels of power

consumption. Thus, it is commonly used in digital transmission system such as long and

short haul tele-communication and data communication, and also used in many

applications such as optical storage system, printers, and cable TV [7].

The typical optical communication system consists of a transmitter, optical

source, transmission media, a detector, and a receiver [8]. In such a system, an optical

transmitter is one of the key components, where it performs as the interface between the

electronics and the emitters. It is very challenging to design optical drivers since its

requirements of large output current and high speed are contradictory, necessitating a

large driving signal and large output transistors. Therefore, suitable circuit structures,

2

suitable decoupling techniques, and a series of optimization steps are necessary for

optical transmitters.

To date, to attain the high-speed data rates, many researchers have designed and

fabricated optical transmitter using various technologies different applications such as

GaAs MESFETs, AlGaAs/GaAs HEMTs, AlGaAs/GaAs HBTs, Si Bipolar transistors, or

SiGe Bipolar transistors [9-18] as shown in Table 1.1. However, those technologies are

not compatible with the non-optoelectronic digital circuits that are widely used in

telecommunications.

The enormous development of research in the field of optical transmitter in

different technologies is not only because bipolar or GaAs transistors usually provide

wider bandwidth, but also because the process technology associated with these

transistors can provide relatively good quality of passive components such as resistors

and capacitors. However, standard digital CMOS technology provides advantages such as

low power, low cost of fabrication due to high yield, and a higher degree of integration

which gives more function blocks in a given size [19].

In the past years, standard digital CMOS technology has been steadily improved

[20,21], and therefore, is intruding the area of other technologies. In addition, new

technology such as Epitaxial-Lift-Off (ELO) [22-26] is now available to integrate a

hybrid-material device into a silicon material substrate. This technology enables to

achieve low cost and high-speed optical communication systems.

3

Table 1.1. List of recently published optical transmitters

Channel

Length

Ref.

Process

or

Optical

Source

Speed

[Gbit/s]

Max. Output

Current or

Output

voltage

Eye

Diagram

BER

Remark

fT

[3]

Si Bipolar

0.6 um

Off-chip

Laser

5

45 mA

Yes

No

-Electrical test

[4]

GaAs MESFET

0.5 um

LiNbO

electro-optic

Moculator

5

36 mA

Yes

No

-Measured in

package

Modulator

20

[5]

AlGaAs/GaAs

HBT

105

GHz

-Electrical test

4 Vpp

Yes

No

-On-wafer

measure

-Electrical test

[6]

AlGaAs/GaAs

HEMT

0.3 um

On-chip

Laser

20

90 mA

Yes

No

- Measured in

package

-Electrical test

[7]

AlGaAs/GaAs

HEMT

0.2 um

Modulator

30

2.2 Vpp

Yes

No

- Measured in

package

-Electrical test

[9]

CMOS

0.5 um

On-chip

VCSEL

2.5

1.6 mA

Yes

Yes

-Optical test

[10]

CMOS

1.2 um

On-chip

Laser

1

1.2 mA

Yes

Yes

-Optical test

[11]

CMOS

1.0 um

On-chip

VCSEL

0.622

40 mA

Yes

No

-Optical test

[31]

SiGe Bipolar

0.3 um

Modulator

23

2 Vpp

Yes

No

- Measured in

package

-Electrical test

[32]

SiGe Bipolar

0.2 um

Modulator

20

0.8 Vpp

Yes

No

- On-wafer

measure

-Electrical test

[33]

CMOS

0.8 um

Laser

2.5

40 mA

No

No

- On-wafer

measure

-Electrical test

[34]

CMOS

0.35 um

VCSEL

1

NA

No

No

-Simulation

results

4

Consequently, Si CMOS technology, which is well known for low cost and high

density is preferred for design of optoelectronic circuitry. Several CMOS driver circuits

have been previously reported for high-speed operation but they have provided small

output current to a laser to achieve high-speed [27-34].

As the data rate is increased, the performance of the system is limited by

packaging parasitics [35,36]. The output of optical transmitter is degraded when

packaging parasitics are combined with abrupt current ripple in bias lines. However not

enough research has been done on packaging parasitics with optical transmitter design.

Thus, thorough research is necessary to address the related issues such as the

simultaneous switching nose. Also, the extraction of packaging parasitics is required. The

primary objective of this research is to develop an differential optical transmitter suitable

for high-speed and high-power using standard digital CMOS technology. The CMOS

optical transmitter will be hybrid integrated with an edge emitting laser using ELO

technology. It is low cost at a given die size, easy to manufacture, and meets high-speed

requirement on optical communication.

In this research, two types of optical transmitters are introduced to achieve the

objective. First one is a scaleable, high dI/dt differential transmitter to meet greater than 1

Gbps data rate. Second one is the optical transmitter compatible with low-voltage

differential signal (LVDS) that is one of the IEEE standards to meet 1 Gbps data rate. To

test optical transmitters, chip-on-board (COB) technology is employed and printed circuit

board (PCB) is designed and manufactured for it. With this technology, 1Gbps

5

performance of the first differential transmitter was achieved with 10-11 bit-error-rate

(BER) electrically due to the poor laser development.

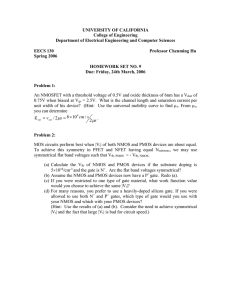

This dissertation consists of 7 chapter. In chapter 2, background to design an

optical transmitter is reviewed. The brief description of optical communication systems

are reviewed and the each components related to optical transmitters are described. Basic

technologies of design optical transmitters for LED’s and lasers are presented and the

advantages and disadvantages of each design methods are addressed. A LED and a laser

are briefly compared. As criteria of evaluating the performance of optical transmitters,

eye diagram is discussed.

Chapter 3 starts with discussion of through silicon optical interconnect system

which is an example of free space optical communication. The MSM photodetector and

InP LED, which is integrated onto the circuit substrate using ELO technology are

described followed by the optical receiver and transmitter circuitry. Also, the test strategy

and methods used for verifying the performance of the system is described. Finally, 2 and

3 layer through silicon systems are implemented and the details of operation including

layout, integration of detector, and measurement results are presented.

Chapter 4 addresses the development and application of a scaleable differential

laser transmitter. The design, simulation, and layout of the differential transmitter are

presented in detail. The scaleability of the transmitter is discussed based on the

simulation using a different minimum gate-length.

6

Chapter 5 states the effect of packaging parasitics in optical transmitter design. In

first section, it starts with the description of the simultaneous switching noise caused by

packaging parasitics. The equivalent circuit model of parasitics is developed by spice

model generator of Advanced Design System (ADS) tool and the values of parasitics are

extracted. To overcome the effect of parasitics, two solutions are suggested. Using

differential topology in transmitter design, the current ripple in the bias line can be

minimized and using decoupling capacitors, the voltage bias is stabilized in the presence

of parasitics. The simulation results, a chip layout, and measurement results of

differential transmitter is presented with 1 Gbps speed operation.

Chapter 6 describes the development of LVDS compatible transmitter which

consists of pre-driver stage and laser driver stage. For high-speed and high-gain, a

differential amplifier with an additional current source are described in pre-driver stage.

The simulation results and layout are presented. However, the measurement results are

not available at the time of this writing due to the bonding problem.

The final chapter of this dissertation is devoted to summarizing the results and

contributions of this research. Also, the possible future work after this research of optical

transmitter is addressed.

7

CHAPTER II

BACKGROUND

In this chapter, three main part of the optical interconnect system are reviewed.

The first one reviewed is optical media which propagates light signal to the optical

detector. Next, two primary optical sources which generate light signal related to the

driving current are review. The next one reviewed is optical transmitter circuitry to drive

optical sources. In addition, the criteria such as eye diagram to evaluate the performance

of the system are reviewed.

2.1 Optical interconnect systems and optical media

An Optical communication system is similar in basic concept to any type of

communication system. The function of a general communication system is to transmit

the signal from the information source through the transmission medium to the

destination. A block diagram of a typical optical interconnect system is shown in Figure

2.1. It consists of a transmitter, optical source, optical media, optical detector, and a

8

receiver. At the transmitter, the information source provides electrical signal to a

transmitter circuitry and it drives an optical source such as a laser and a LED to give

modulation of the lightwave carrier. The optical source converts electrical signal to

optical signal and the light output is propagated through the optical media such as optical

fiber and free space. The light signal from the optical media is collected on an optical

detector such as avalanche photodiodes and p-i-n photodiodes and converted to the

electrical signal. Finally, the electrical signal is amplified and recovered by the optical

receiver.

Information

Source

Optical

Transmitter

Optical

Receiver

Optical

Source

Recovered

Information

Optical Optical

Media Detector

Figure 2.1. A block diagrm of a typical optical communication system

For optical interconnects, optical transmission media is categorized into free

space, optical fibers, and integrated optical waveguides [1]. The difficulties associated

with the fiber-optic approach stem from the alignment requirements for the fibers and

detectors. Also, the fibers cannot be allowed to bend too much since bends cause

radiation losses. In waveguide approach, the difficulties lie on the requirement to

9

efficiently couple into and out of the guides. Careful alignment of the sources with the

integrated waveguides is required.

The other major category of optical interconnects is free-space techniques which

light is propagated in the free space. Free-space interconnects can be distinguished

between two types of techniques, unfocused [37] and focused [38-40]. Unfocused

interconnections are established simply by propagating the optical signals to the entire

electronic chip. However, the system is very inefficient since only a small fraction of the

optical energy might be absorbed on the photosensitive areas of the detectors and the rest

is wasted. Therefore, inefficient use of optical energy may result in requirements for the

extra amplification of the detected signals on the chip. In focused interconnections, the

optical source is actually imaged by an optical element onto a multitude of detection sites

simultaneously. The efficiency of such a scheme can obviously exceed that of the

unfocused case, provided that the optical elements have suitable efficiency. However, the

disadvantage of the focused interconnect technique is the very high degree of alignment

precision that should be achieved and maintained to ensure that the focused spots are the

appropriate places on the chip.

10

2.2 Optical Sources

Optical transmitters in optical interconnection consist of two main parts, a driver

circuit and an emitter [41]. The driver circuit converts electrical signals into an emitter

drive current and the emitter converts this current into light. The two primary light

sources used in telecommunications are semiconductor lasers and light emitting diodes

(LED) [42,43]. These optical sources have several requirements for optical emitter. First,

they should be linear with the electrical input signal to minimize the distortion and noise.

Second, they should emit light at wavelengths which has low losses and low dispersion.

Last, they should have capability to maintain a stable optical output in the condition of

temperature variation.

In a forward biased p-n junction, the normally empty conduction band of the

semiconductor is populated by electrons injected into it by the forward current through

the junction, and light is generated when these electrons recombine with holes in the

valence band to emit a photon. The energy of the emitted photons is roughly equal to the

bandgap energy of the semiconductor material which gives a much wider spectral

linewidth. Therefore, the drawbacks of the LED are low output power, higher divergence

degree, and wide optical spectral bandwidth which are not suitable for high-speed

communication. However, the LED has been widely used in low-speed communication

as an alternatives to the laser since the LED has a number of distinct advantages which

are simpler fabrication, less expensive, high reliability, less temperature dependence,

simpler driver circuitry, and higher linearity. The LED has been developed for edge or

11

surface emission. The edge-emitting LED shows more output power and a somewhat

narrower spectral width since it has a structure more like a laser but it requires the

complexity both in fabrication and in driver circuitry. In contrast to the edge-emitting

LED, the surface-emitting LED shows long device lifetime, low cost, and insensitivity to

ambient temperature.

The term laser is an acronym for light amplification by stimulated emission of

radiation. The light is stimulated utilizing the addition of an optical cavity and mirror

facets to provide feedback of photons. The emission process of the laser can occur in two

ways, which are spontaneous emission and stimulated emission. First, spontaneous

emission is occurred with the same mechanism in which the atom returns to the lower

energy state in a random manner. Second, stimulated emission is occurred when a photon

having an energy equal to the energy difference between the tow states interacts with the

atom in the upper energy state causing it to return to the lower state with the creation of a

second photon. Therefore, LEDs and Lasers have different characteristics as shown in Fig

2.2. In Figure 2.2, it may be observed that the laser emits little light output in the region

below the threshold current but above threshold current, the light output increases

eminently and linearly for small increases in current though the device acting as an

amplifier of light. This linear region can be used for data transmission.

12

Light

Output

(Power)

Laser

LED

Threshold

current

Current

Figure 2.2. The light output versus current characteristic of Laser and LED

There are two broad kinds of lasers, edge emitting lasers and vertical cavity

surface emitting lasers (VCSELs). VSCEL has been interested because it has low

threshold current and a symmetric output for efficient optical coupling to the fiber.

However, it has shortcomings including small lifetime, high cost and short wavelength

because of the lack of mirrors for 1.3 to 1.55 µm. 1.3 to 1.55 µm wavelengths has been of

interest for fiber optic communication since the optical fiber has zero dispersion near the

1.3 µm wavelength and has lower loss near 1.55 µm wavelength although 0.85 µm range

is still useful since the wavelength is compatible with on-chip Si detectors.

Several kinds of structure have been developed such as Gain-guided lasers, Indexguided lasers, and Quantum-well lasers for edge emitting lasers. The simplest and least

expensive laser is the double heterostructure Fabry-Perot (DH FP) laser. However, the

13

modulation bandwidth is limited by relaxation oscillations which is the oscillation

between the carrier and photon population when the current is suddenly increased. In

addition, it shows frequency chirp which is the critical for long haul communication due

to fiber dispersion. For long haul communication, distributed feedback (DFB) lasers has

been developed with single frequency operation. The structure is the distributed Bragg

diffraction grating which provides frequency selective feedback in the optical cavity.

For the high-speed communication faster than 10 Gbps, lasers cannot be used

with direct modulation due to chirp but they can be used with external modulator such as

electro-absorptive modulator and mach-zehnder modulator. As a result, the optical source

should be selected carefully in terms of the application area.

14

2.3 Optical transmitters

There are two categories in optical transmitter circuitry with respect to the optical

sources, LED and laser. Although the application of the LED is restricted compare with

the laser, it can be an effective alternative to the laser for low-capacity and short-distance

link such as local area network.

For the on-off keying modulation in digital transmission, the LED are operated with

switching on and off of a current in the range of a few tens to a few hundreds mA. This

current switching is performed in response to input logic voltage levels at the driving

circuit. A common method of performing this current switching operation of the LED is

shown in Figure 2.3. The common emitter configuration is adapted with a bipolar

transistor providing current gain. In this circuit, the output current flowing through the

LED is set by the value of R2. However, the switching speed is limited by the diffusion

capacitance which means that the bandwidth and current gain have the tradeoff relation.

To increase the switching speed, low impedance driver is developed as shown in Figure

2.4. In this configuration, the emitter follower stage is placed with the common emitter

stage to drive the LED. As well as these LED transmitters, many kinds of transmitter

circuitry have been developed in terms of the requirement such as emitter-coupled logic

(ECL) or transistor-transistor logic (TTL) compatibility [44-47]. In digital transmission,

the interface between the transmitter and a common logic family is a frequent

15

requirement. In addition, LED has been considered for analog transmission because of

the linear output response of the optical power as seen in Figure 2.2.

V CC

LED

R2

V in

R1

V EE

Figure 2.3. An example of the LED driver circuit I

V CC

V in

R2

R1

LE D

V EE

Figure 2.4. An example of the LED driver circuit II

16

The laser transmitter circuitry is somewhat different from the LED drivers since

as shown in the light-versus-current characteristics of the laser in Figure 2.2, the light

output is very small until the DC current reaches the threshold current [48]. After the

threshold current, the optical power is approximately linear with current. The problem

associated with typical lasers is that the characteristic curve is not linear at high current

and tends to shift to the right as both the temperature and device ages are increased. This

results in unwanted changes in output power, extinction ratio, and turn-on delay in digital

transmission. Thus, the laser should be biased near the threshold current when it is in off

state to reduce the turn-on delay and to minimize any relaxation oscillations, and also to

easily compensate for variations in threshold due to temperature and device ageing. For

biasing the laser, a bias control circuit is necessary in designing laser driver circuits.

A simple laser driver circuit used to connect the output of a current driver circuit

directly to the laser diode is shown in Figure 2.5 [49]. The threshold current for a laser is

provided by Vbias and modulation current is provided by source resistor, Rmod,

respectively. This type of single-ended laser driver is typically used with low operating

speed due to the unwanted parasitic inductance from the package’s bonding wires. When

this parasitic inductance is combined with the capacitance of the laser driver circuits and

lasers, it degrades output of the laser’s rise time and causes power supply current ripple.

Another example of the laser driver circuit is shown in Figure 2.6 when the driver

circuit and the laser are placed in different package. In this topology, a matching circuitry

between the driver and the laser is necessitated to overcome the large impedance mis-

17

match. In this circuit, Ibias controls the DC threshold current and Imod provides the

modulation current for the laser.

With these laser drivers, many types of drivers has been developed with various

technology in terms of the different application areas [50-55]. As mentioned above, it

becomes critical to consider the interactions among circuitry, interconnections and

packaging at high-speed operation. As a result, the suitable topology should be selected

in the design of the drivers and also, interconnections and packaging should be

considered.

18

Laser

Input

Signal

Rmod

Vbias

VSS

Figure 2.5. An example of the laser driver I

VCC

Laser

Vin-

Imod

Ibias

VEE

Figure 2.6. An example of the laser driver II

19

2.4 Eye Diagram

To evaluate the system performance, the eye diagram is a simple method for

digital transmission systems [56]. The performance of the systems depends on the

amount of intersymbol interference (ISI) and noise [57]. ISI can be occurred when the

signal passes through the dispersive system. In optical interconnect system, dispersion is

associated with the fiber, coupler, the transmitter circuitry, and the receiver circuitry. ISI

is that the pulses corresponding to any one-bit smear into adjacent bits and overlaps. So,

if ISI is large enough, this might trigger a false detection in the adjacent time slot. As a

result, an increasing number of errors may be encountered as the ISI becomes more

pronounced.

When observing data transmitted by optical driver on the oscilloscope, there is a

visual method that is often used to qualitatively measure the properties of a recovered

data waveform. If the pulse stream is applied to the vertical input and the sampling clock

is applied to the external trigger, a waveform looking like a human eye is obtained. This

is called an eye-diagram due to its similarity of shape to a human eye.

An eye diagram is easily generated using an oscilloscope that is triggered by the

symbol-timing clock and keeping the curve trace for certain duration of time. The eye

diagram is a composite of multiple pulses captured with a series of triggers based on

data-clock pulse fed separately into the scope. The scope overlays the multiple pulses to

form the eye diagram.

20

Usually, long pseudo-random data patterns are often used when generating eyediagrams to guarantee that the eye-diagram is representative of virtually all possible

symbol transitions. By measuring the width of the eye opening both in the vertical and in

horizontal directions, the information about the system’s ISI, noise, and jitter is obtained

as shown in Figure 2.7. The jitter, which is due to variations in the pulse duration or the

accuracy of the symbol clock, will cause the eye closing in the horizontal direction. Noise

and ISI are indicated by the vertical width of eye diagram. The ideal decision sampling

point occurs at the time of maximum vertical opening. This point corresponds to the time

when the signal-to-noise ration is at its maximum. Also, the size and shape of the eye

diagram changes depending on the data rate.

Optimum

sampling time

Sensitivity to

timing error

Distortion of

zero crossings

Noise margin

Peak distortion

Figure 2.7. Characteristics of an eye diagram

21

After the signal is displayed in the form of eye diagram in oscilloscope, the signal

should meet the certain criteria to ensure the proper performance of the system.

Therefore, eye pattern mask is defined and employed measuring the eye diagram. As an

example of eye mask, the SONET specifications provide a mask inside and around the

eye diagram with required parameter values that can sustain the system link BER as

shown in the Figure 2.7 according to the Bellcore’s technical report [58].

22

1 + Y1

Normalized Amplitude

1

Logic "1" level

1 - Y1

0.5

Y1

0

Logic "0" level

- Y1

0

X1

X2

1 - X2 1 - X1

1

Time [UI]

Rates

X1

X2

Y1

OC-1 and OC-3

0.15

0.35

0.20

OC-9 through OC-24

0.25

0.40

0.20

Figure 2.8. SONET eye diagram mask [58]

23

CHAPTER III

THROUGH-SILICON OPTICAL INTERCONNECT

SYSTEMS

3.1 Introduction and Applications

Advances in integrated circuit have remarkably increased device densities and

speeds. However a large portion of the available area and bandwidth is consumed by

interconnects. As line lengths get longer, propagation delays, crosstalk between lines, and

dominance of line capacitance will restrict the utility of conventional electrical

interconnections [2]. Therefore, new chip architectures are required to cope with

associated interconnect problems. One possible solution is multichip modules (MCM’s).

However, as the density of chips on an MCM substrate increases and the interconnections

between chips increase, problems with unwanted coupled noise and simultaneous

switching noise limit the scalability of these architectures [59]. Another approach is to

use vertical optical interconnections [60-66]. They provide high speed, high bandwidth,

24

low

loss,

small

crosstalk,

short

interconnect

delay,

and

massively parallel

interconnection.

In this chapter, through-wafer vertical optical interconnect system between

stacked silicon circuitry shown in Figure 3.1 is introduced.

It is utilized by using

optoelectronic devices operating at wavelengths which silicon substrate is transparent. To

achieve the system, a receiver, a transmitter, and optical devices such as a LED and a

detector are contained. The OEIC (Opto-Electronic Integrated Circuit) was fabricated in

0.8 µm CMOS process through MOSIS foundry. Then optical devices were integrated

onto silicon circuit substrate using thin film hybrid integration technology. This

integration provides the reduction of the packaging parasitics between the optical devices

and the silicon circuits compared with hybrid packaging using wire bonding.

InP/InGaAsP

InGaAsP

Detector

Emitter

Detector Amplifier

Silicon Circuitry

Emitter Driver

Silicon Circuitry

Emitter

Detector

InGaAsP

InP/InGaAsP

Emitter Driver

Silicon

Detector

Silicon Circuitry

Figure 3.1. Diagram of vertical optical interconnect

25

3.2 Optical Devices

Optoelectronics have been explored as a solution to bypass bottlenecks in

electrical interconnections. The extent of the problem has justified the integration of

optical devices onto a fabricated circuit substrates. Monolithic integration of optical

devices and high-speed circuitry has been demonstrated. However, the costs of these

systems are expensive due to the expensive substrates, growth technologies, and poor

yield [67,68].

An alternative method for combing optical devices with electrical circuits is a

hybrid approach. Hybrid integration enables individual optimization of the optical

devices and of the electrical circuits. In this method, optical devices are grown and

fabricated on their own growth substrate and then attached onto silicon circuitry by either

flip-chip technology or thin film integration. Flip-chip technology attaches optical

devices onto a silicon substrate using bump bonds. However, bump bonding consumes a

large amount of expensive optical materials.

Thin film integration, bonding to the host substrate is performed using standard

microelectronic processing techniques since the devices are on the order of 0.01 to 5

microns thick [23][25]. Furthermore, only a small quantity of optical materials is required

to integrate a large number of host substrates minimizing the use of expensive optical

materials. Another advantage of thin film devices is integration into three-dimensional

systems [63], which are useful for parallel applications such as image processing.

26

In this research, InP based light-emitting diodes (LED’s) [69] and metalsemiconductor-metal (MSM) photodetectors [70,71] are fabricated and integrated onto

silicon circuit substrate as illustrated in Figure 3.2. The operating wavelength of these

optical devices is in the range of 1.3-1.6 µm where silicon is transparent. The thin-film

optical devices are fabricated by epitaxial lift off (ELO) technology [23]. As shown in

Figure 3.2, the thin film materials and devices are processed separately and bonded

without degrading the quality of the devices by parasitics due to packaging.

Final Integration

Figure 3.2 Illustration of the optical device integration on Si circuit substrate.

27

For vertical interconnects, LED’s are used since they have demonstrated high

reliability, and are low cost, simple to fabricate. Also, LED’s can be operated at the

desired modulation speed up to 155 Mbps with good quantum efficiency. Although the

divergence angle of LED’s is large, it also results in a high degree of alignment tolerance

for the vertical interconnects. In the case of detectors, inverted MSM (I-MSM) detectors

are selected since they have low capacitance per unit area and high responsivity that are

important factors in design of high speed and low power receiver units. MSM detectors

have low capacitance but low responsivity because of the shadowing effect of the

electrodes. Therefore, I-MSM detectors are developed to overcome the low responsivity

of MSM’s defining electrodes on the bottom of the detector to eliminate the shadowing

effect.

To construct through-wafer system, 100 µm LED’s and 50 µm I-MSM

photodetectors are integrated onto transmitters and receivers respectively and then each

chip containing silicon circuits and integrated optical devices is stacked together.

28

3.3 Single-Ended Transmitter Design

The single-ended CMOS transmitter is designed to meet the SONET OC-3 speed

specification of 155 Mbps. The transmitter circuit was optimized to drive up to 80 mA of

output modulation current to the emitter. It consists of two tapered buffers, a current

switch, and a current mirror as shown in figure 3.3. The transmitter is fabricated through

the MOSIS foundry in a 0.8 µm Si CMOS process.

VDD

M1

M3

M5

M2

M4

M6

M9

M10

M11

I2

V1

D1

I1

M7

M12

M8

VSS

Figure 3.3 Circuit schematic of single-ended transmitter.

29

The two-stage tapered buffer input is designed to minimize power consumption at

desired speeds and begins with a minimum geometry inverter used to drive a current

switch. The ratio of two inverter sizes has the tradeoffs between speed, power, and chip

size. For the maximum speed, the ratio of 2.7 is rational but it reveals high power

consumption. If the ratio is above 2.7, speed is slightly decreased but also power

dissipation is decreased. Thus, the optimal value of the ratio considering the tradeoff

between speed and power is set to 5 for 155 Mbps. The current switch was used before

the power transistor stage to avoid large voltage spikes and signal distortion in the output.

In output stage, a current mirror for dc bias of the emitter is included for increased speed.

To test the optical performance of the transmitter unit, the transmitter circuits with

integrated LEDs were wire-bonded onto a quad flat pack. 27-1 psudo random bit

sequence (PRBS) were generated by Tektronix 1400TX and the emitted light was

detected by a New Focus 1811 receiver. A microphotograph of the transmitter with

integrated LED is shown in Figure 3.4. In Figure 3.5, the eye diagram of testing the

integrated chip is shown at 155 Mbps. Bit error rate (BER) was measured by Tektronix

1400RX and 10-13 was achieved at 100 Mbps.

30

Transmitter

Integrated LED

Figure 3.4 The microphotograph of the transmitter with integrated LED.

Figure 3.5. The measured eye diagram of the integrated transmitter at 155 Mbps.

31

3.4 Single-Ended Receiver Design

The single-ended transimpedance receiver was designed and fabricated through

the MOSIS foundry in a 0.8 µm Si CMOS process [72]. To obtain the target bandwidth,

which is greater than 155 Mbps, the receiver used a multistage low-gain-per-stage open

loop configuration. The receiver consists of five identical cascaded stage with a current

gain of 3, an offset circuit, and bias circuitry as shown in Figure 3.6.

.

VDD2

VDD1

Offset

Pi1a

120

si2

Pi1

120

Stage 1

Pba

2.4

Pi2a

2.4

P5a

2.4

P8a

2.4

P6a

7.2

si1

Pi2

2.4

P5

2.4

P8

2.4

P6

7.2

BiasP

Pb

2.4

iin

Isource

N2

2.4

Ioffset

Ni1

120

ig2

Nia2

2.4

ig1

Nia1

2.4

N7

2.4

N1

2.4

vout

N4

7.2

RL

N4a

7.2

Isink

Ni2

120

N3

2.4

N7a

2.4

Nb

2.4

VSS1

AI = 3

AI = 3

AI = 3

AI = 3

AI = 3

Figure 3.6. Overall circuit schematic of the receiver.

VSS2

BiasN

32

Since this receiver is a current –mode amplifier, the current gain of each stage, AI,

is set by the gate width ratio of two transistor in a current mirror. Also, overall

transimpedance gain of the receiver is given by

R = AI * *5 * RL = 243 * RL

(3-1)

Figure 3.7 shows the microphotograph of the receiver integrated with I-MSM

photodetector. To bond the thin-film detector to the input side of the circuit, two small

pads are required. The pad size should be small enough to minimize the pad capacitance

since this capacitance increases the total input capacitance of the circuit limiting high

bandwidth.

Figure 3.7. The microphotograph of the receiver with integrated I-MSM detector.

33

The receiver with integrated I-MSM detector was tested and an eye

diagram was measured using 27-1 PRBS input data which is generated by Tektronix

1400TX. The input signal is fed into a modulator to generate a light emitting with a laser

source. Then the lightwave is illuminated onto the I-MSM detector of the receiver. The

detected light signal is converted into an electrical signal and amplified in the receiver.

The output of the receiver is measured in an oscilloscope with an output load of 50 Ω.

Figure 3.8 shows the measured eye diagram at 155 Mbps. In eye diagram, top trace is the

clock signal and the bottom trance is the eye diagram of the amplifier output. Bit error

rate (BER) was measured by Tektronix 1400RX and 10-10 was achieved.

Figure 3.8. The measured eye diagram of the integrated receiver at 155 Mbps.

34

3.5 Two-Layer Systems

To demonstrate vertical optical interconnects, two-layer system is realized [64].

Each integrated circuit layer in the two-layer stack consisted of an optical transmitter and

an optical receiver. Each of the chips were integrated with a thin film LED and an IMSM photodetector. Figure 3.11 shows the microphotograph of each layer before

integrating of optical devices and stacking of two chips. This chip stacked with two

layers where the top chip is rotated 180o relative to the bottom chip as illustrated in

Figure 3.11. After all three layers were assembled, the system was wire-bonded into a

LDCC 44-pin flat package for testing.

To test the two-chip stack, the test set up is shown in Figure 3.9. 27-1 PRBS

digital signal from Tektronix 1400TX was fed into the bottom transmitter. Then the

transmitter supplies current to drive an emitter and the electrical input signal is converted

into the light output signal from the emitter. The voltages and currents in each circuits of

the system were controlled using Keithley 238 source measurement units. An

oscilloscope measured the output signal from the top receiver circuit. The two-layer

system performed well at 10 Mbps with 3.5 V power supply voltage for both the

transmitter and the receiver as shown in Figure 3.12. However, a ringing due to ground

bounce was noticeable in output eye diagram. It causes significant noise, as the bit rates

are higher as shown in Figure 3.13. This noise is primarily due to decoupling problems in

the test fixture. Therefore, the system worked up to 40 Mbps even though each

components of the system has been tested up to 155 Mbps.

35

M ic r o w a v e L o g ic

LE D

L E D D r iv e r

g ig a B E R T - 1 4 0 0 T X

D e te c to r

R e c e iv e r

T e k t r o n ix 1 1 4 0 3 A

O s c illo s c o p e

M ic r o w a v e L o g ic

g ig a B E R T - 1 4 0 0 R X

C lo c k f o r T r a n s ie n t o u t p u t c u r v e a n d B E R s y n c h r o n iz a t io n

Figure 3.9. Test setup block diagram for through-wafer system

36

Figure 3.10. The microphotograph of the OEIC for two-layer system.

Figure 3.11. The microphotograph of the two-layer system

37

Figure 3.12. The measured eye diagram of two-layer system at 10 Mbps.

Figure 3.13. The measured eye diagram of two-layer system at 40 Mbps.

38

3.6. Three-layer systems

To demonstrate the applicability of through-wafer optical interconnects, a threelayer system is also introduced [65]. The same components, which were used in twolayer system are used in this system. The three-layer system was assembled by aligning

the individual layers using an infrared backplane mask aligner. After all three layers were

assembled, the system was wire-bonded into a 144-pin grid array (PGA).

Figure 3.14 shows the layout for three-layer system. In this layout, isolation

method was used to minimize the noise coupled from the digital section to the sensitive

analog input stage of the receiver since this system contains several digital blocks such as

a transmitter, a clock generator, and a comparator. Isolation method is to attempt to keep

the sensitive analog circuitry separated from the noisy digital circuitry, or to block the

transmission of the noise from the digital circuitry to the analog circuits using n-well or

p-well appropriately. In Figure 3.14, n-well and p-well contact are shown between the

receiver part on the left side and the digital blocks on the right side.

Figure 3.15 shows a microphotograph of the packaged 3-D systems, which is

measured to show the performance of the whole system.

The primary goal of this system is to demonstrate optical through-wafer

interconnect from the bottom layer to the top layer. First, the data from the bottom

transmitter goes to the receiver of the middle layer, then the middle layer routes the

39

receiver data through the comparator to the transmitter input. Last, the data is transmitted

from the middle layer to the top layer.

To test three-layer systems, the same test setup as in Figure 3.9 was used. 27-1

PRBS data was generated by pattern generator and the eye diagram is measured by

oscilloscope. BER was also measured by Tektronix 1400RX. The test results at 1 Mbps

was shown in Figure 3.16 with 1.3x10-9 BER. As well as two-layer systems, the speed of

the system is limited due to decoupling problem of the test fixture and signal coupling

within the high-pin PGA package. High-speed demonstrations would be enabled by

utilizing improved decoupling method, by using different package and by employing

differential topology in the design of CMOS transceiver circuits.

Figure 3.14. Layout of the OEIC for three-layer system

40

Figure 3.15 Microphotograph of three-layer system

Figure 3.16 The measured eye diagram of three-layer system at 1 Mbps.

41

CHAPTER IV

DIFFERENTIAL LASER DRIVER

4.1 Introduction

In chapter 3, the free space optical communication was implemented. However, as

the speed is increased, the receiver requires high incident optical power for high signalto-ratio (SNR) and high sensitivity. Therefore, the laser should be chosen for optical

source since it has low divergence degree and high power efficiency. A differential

CMOS transmitter circuit to drive a laser is introduced in this chapter. The driver was

fabricated in a 0.35 µm technology process through national semiconductor. A laser

driver circuit that is capable of operating above Gbps and providing large output current

for high optical power is designed for high-speed optical interconnect.

For the development of high-speed driver, the differential topology is employed to

stabilize current ripple in the power supply lines [73], which would otherwise corrupt the

laser output. Differential design minimizes simultaneous switching noise by using

parallel but inverted signal paths with subsequent subtraction of the two signals. In

42

addition to conventional differential pairs, current mirrors are used to provide adjustable

threshold current and modulation current for the laser.

In this research, the goal is to design the driver with greater than 1 Gbps speed

operation providing high modulation output current (up to 180 mA) to the laser. The

driver has been laid out using MAGIC layout tool. Then the parameters of the circuit

layout has been extracted and simulated. When the simulation result did not meet design

specification, the design procedure has been repeated as shown in Figure 4.1.

D e s ig n

Layout

E x t r a c t io n

S im u la tio n

No

S p e c ific a tio n

Yes

F in a l

Layout

Figure 4.1 Design procedure of differential transmitter

43

Final layout has been converted into cadence layout with existing electric static

protection pads, which is provided by National Semiconductor. After the chip was

fabricated, it has been tested to meet the design goal, which was predetermined.

The predetermined design specification of the transmitter is shown in the table

below. The specification was predetermined by the optical device group in Georgia

Institute of Technology.

Table 4-1. Design specification of the differential laser driver

Specification

Predetermined Goal of Design

Speed

Greater than 1Gbps

Output Current

Current Density

DC range: 0 – 30 mA

AC range: 0 – 180 mA

Less than 30uA/1um square meter

44

4.2 Differential Transmitter Design

The silicon CMOS high dI/dt differential laser driver circuit described herein was

designed to meet the predetermined specification. For giga bit interconnect, some laser

drivers using CMOS has been recently reported [27-35]. However, these laser drivers

provide small output modulation current as shown in Table 2.1. The driver in this

research consists of current mirrors and a current switch, as illustrated in Figure 4.2. In

this driver circuit, the output delivered to the laser diode is composed of Ith for dc biasing

the laser near the threshold current, and Imod for the modulation current above threshold.

In an integrated implementation, the diode would be removed and a laser would be

integrated instead of the diode. Also, Z1 would be replaced either a laser or a resistor. As

shown in Figure 4.2, the switching circuit is realized by differential NMOS transistors in

common source configuration. The current sources for dc biasing and modulation current

are realized by current mirrors, where a reference current should be supplied through the

external source measurement unit.

The transistor size is optimized for up to 180 mA peak-to-peak modulation

current and up to 30 mA laser-biasing current. The primary effects of determining the

operating speed are switching delay of input transistors and the RC time constant of wire

interconnect on a chip. As transistor size increases, higher output currents are achievable

but the speed is decreased since the gate capacitance of the input transistor increases the

total input capacitance, which is given by

45

Ctotal = Cox (WL )n ,

(4-1)

Cox = εxoxox ,

where the oxide permittivity εox is 3.9εo F/cm when silicon dioxide is used as the gate

insulator, xox is oxide thickness, and W and L are the width and the length of the input

transistor. In this expression, εo is the permittivity of free space and εo≈8.854×10-14 F/cm.

If total capacitance is increased, it causes large switching delay of the circuit.

Thus, the optimization of the transistor size is necessary for the design of the

driver circuit to provide large modulation current maintaining high-speed operation. Also

careful layouts to reduce parasitic capacitance of transistors are required. The simulated

results of the speed versus output current and speed versus input magnitude are illustrated

in Figure 4.3. The speed is proportional to input magnitude but inversely proportional to

output current. In Figure 4.3 (b), it is shown that the speed is saturated above 2 V peakto-peak input magnitudes since drift velocity of electron is saturated. As a result, the

optimal size of transistor has been selected to perform 1 Gbps operation driving proper

modulation current and laser-biasing current.

46

VDD

Z1

M1

D2

M2

V1

V2

Ith

Imod

M6

M4

M3

M5

VSS

Figure 4.2. A differential laser driver.

M7

47

25

Speed (Gbit/s)

20

15

10

5

0

0

200

400

600

800

Output current (mA)

(a) Speed versus output current

14

Speed (Gbit/s)

12

10

8

6

4

2

0

0

0.5

1

1.5

2

2.5

3

Input magnitude (V)

(b) Speed versus input magnitude

Figure 4.3. The optimization in terms of the transistor size

48

4.3 Simulation

The HSPICE simulation on the overall transmitter has been performed using 0.4

µm, BSIM level 4 model parameters (See Appendix II) provided by national

semiconductor. The simulation has been done with extracted SPICE files from magic

layout. Figure 4.5 shows the transient response of the driver at 1 Gbps speed with 180

mA output current. In the simulation result, the top trace represents the psudo random bit

input signal and the middle trace is the transient output. The bottom trace is the eye

diagram to prove that there is not any missing bit. As shown in the simulation results, the

driver works properly at the predetermined design specification.

For the SPICE simulation of the laser and the driver circuit, the electrical

equivalent circuit model of the laser is developed and presented as shown in Figure 4.4

[74,75]. For practical usage, it should be as simple as possible to minimize calculation

time.

Lb

Rs

Cp

Rj

Figure 4.4. Equivalent Model of a laser diode

Cj

49

In this model, chip and package parasitics are included, but for simplicity they are

not incorporated in simulations. In Fig. 4.4, the components of the equivalent circuit

model are inductance Lb due to the wire bond, capacitance Cp of the laser chip, resistance

Rs from the metal contacts, capacitance Cj from the p-n junction, and resistance Rj from

the p-n junction. Using this equivalent model, optical output of the laser is treated as an

electrical output, which can be displayed by SPICE.

4.5 Measurement and Test Results

Figure 4.5. Transient response of 1 Gbps differential laser driver

50

Figure 4.6. Temperature simulation at 27 and 200 degree

Next, temperature is considered since integrated circuits slow as temperature

increases due to the mobility variation. Thus, this simulation is to verify that the driver

works properly at higher temperature. Figure 4.6 shows the transient response of the

driver with temperature variation at 27 degree and 200 degree. The top trace is the

transient output at 27 degree and the second trace is the eye diagram of the top trace. The

third trace represents the transient output at 200 degree and the bottom one is the eye

diagram of the third trace. As shown in Figure 4.5, output is a little slower at 200 degree

than room temperature 27 degree but still shows a wide-open eye diagram.

51

Figure4.7. Transient response of differential laser driver at 2 Gbps.

Figure 4.7 shows the transient response of the drive operating at 2 Gbps. The top

trace is the input signal and the middle trace is the transient output. The bottom trance

represents the eye diagram of the output current. Even though the laser driver was

designed and optimized for 1 Gbps operation with 180 mA modulation current, it worked

well at 2 Gbps as shown in Figure 4.7. Compared with the 1 Gbps simulation result, the

rising and falling time is a little slow but still works with a wide-open eye diagram.

52

4.4 Layout

The driver was laid out carefully for fabrication using magic layout tool as shown

in Figure 4.8. While the driver was laying out, every effort was made to minimize the

parasitic capacitance of input transistors since it was found out that the capacitance was

very critical for the system performance. In the layout, multiple finger structure with one

wide transistor is used to minimize the depletion capacitance such as metal to poly and

metal to metal.

Figure 4.8. MAGIC layout of the driver

53

4.5 Scalability

Since the driver has been designed using 0.35 µm standard CMOS process

without any passive components, the design is scalable, which means there is a room for

speed up in advanced technology. In the CMOS, the speed is related to gm/C. So, The

speed can be improved by a scale factor because the capacitance (C) of the device is

reduced while the transconductance (gm) of the device is almost same. The performance

scalability of the integrated circuits is important to reduce chip area and to improve the

circuit performance [76-80].

The driver in Figure 4.2 is scaled down from 0.35 µm to 0.18 µm with a scale

factor of 1.944 and the bandwidth of the driver increases from 2 Gbps to 10 Gbps as

shown in Figure 4.10. In this simulation, there are two factors increasing the speed. One

is from scaling down the minimum gate length and another is from decreasing the

modulation current from 180 mA to 25 mA. Since the total transistor size is depending on

the current density of the gate in CMOS, reduced current result in the smaller total

transistor size, which allows the smaller parasitic capacitance. Figure 4.9 shows the

layout of the driver that is scaled down using 0.18 µm technology.

In Figure 4.10, the top trace is the input signal and the middle trace is the transient

output. The bottom trance represents the eye diagram of the output current.

54

Figure 4.9. MAGIC layout of the driver using 0.18 µm technology.

Figure4.10. Transient response of differential driver at 10 Gbps.

55

CHAPTER V

PACKAGING PARASITIC CONSIDERATION

5.1 Introduction

The signal degradation due to the presence of the parasitics associated with

packages and bonding wires has been a crucial factor as the higher data rate and higher

density is required in telecommunication [81]. These parasitics causes switching noise

known as delta-I noise when the current is switched in power distribution systems [8284]. This noise degrades edge rate of digital signal, reduces noise margins, and finally

causes false switching of digital logics that is the error of the system. Therefore,

packaging parasitics should be included in the design of the drivers.

To date, silicon CMOS drivers for bit rates up to several gigabits per second for

low cost, low power consumption implementations have been reported. Also, delta-I

noise has been analyzed and investigated by many researchers [85-87]. However, the

parasites of the package and bonding wires have not been considered in the design of

56

these laser drivers due to the lack of efficient methods and models, although they are

bonded into a package.

In this research, an equivalent circuit model of parasitics containing bonding

wires and packages are developed. The equivalent model is included in HSPICE

simulation of the driver and shows the effect of the parasitics.

In order to solve the parasitic problem, the differential topology can be selected

instead of single-ended topology by stabilizing the bias current since it has symmetric but

inverse current flowing path to the power supply lines [88]. However, the effect of the

parasitics cannot be eliminated fully due to a device mismatch in the differential pairs and

a different delays in the current path, although it has better bias current stabilization

compared with single-ended version.

Thus, use of an decoupling capacitor is also

suggested to eliminate the effect of packaging parasitics [89-93]. In the simulation of the

driver, actual equivalent model of capacitors is included to predict the precise effect of

decoupling capacitor when the driver is tested and compared with the ideal capacitor.

Finally, the differential driver described in chapter 4 has been tested with the

decoupling capacitor and shows the good accordance with the simulation results.

57

5.2 Background

In a single chip package and printed circuit board (PCB) system, voltage

fluctuation named simultaneous switching noise or delta-I noise has exceeding increased

and affected the performance of integrated circuits as the circuit transition time is

increased. The delta-I noise is caused by the parasitic inductance of the power supply

lines in the package and abrupt current change in the switching circuits.

To describe the mechanism of delta-I noise, a simple inverter with parasitic

inductance is shown in Figure 5.1. When the input signal of the inverter (Vin) switches

state from low-to-high or high-to-low, it causes an abrupt current change to the power

supply distribution system through the interconnections. This results in a voltage drop in

the power supply (Vp) in the presence of the parasitic inductance (L_parasitics) as

explained in

Vnoise = L

dI

dt

(5-1)

The magnitude of the delta-I noise is proportional to the parasitic inductance and

power supply current variation. If the magnitude of the voltage drop becomes too large, it

results in the errors of the system. Therefore, the current variation should be reduced to

minimize the voltage drop and it can be achieved by choosing differential topology in

58

circuit design. Another way of reducing the delta-I noise is to minimize the parasitic

inductance with carefully selecting package and PCB. However, the delta-I noise is not

fully eliminated but partially reduced since the inductance has always a finite value in

bonding wires as well as in the package and PCB. Therefore, by placing the decoupling

capacitor near the internal power supply to provide charge during switching, delta-I noise

can be effectively reduced as illustrated in Figure 5.1.

L_parasitics

Vin

C_decouple

Figure 5.1. The example of the delta-I noise in a circuit.

Vp

59

5.2 Modeling of the parasitics

A lumped-element equivalent model (RLC) for the packaging parasitics is

developed to predict and analyze the behavior of the parasitics in the driver design. The

model includes package bonding wire impedance, PCB metal line impedance, and bias

wire impedance. The model and the values of the PCB impedance were generated and

extracted from Advanced Design System (ADS) design tool. And the inductive

impedance of bonding wires and bias wires were calculated [94] by

L=

4l

µ ol

(ln( ) + µrδ − 1)

d

2π

(5-2)

where µo is the permeability of free space, µr is the relative permeability of the bonding

wire material, d is diameter of the boding wire, l is the length of the bonding wire, δ is the

skin effect factor give by

δ = 0.25 tanh(

4ds

),

d

And the skin depth of the bonding wire material is given by

(5-3)

60

ds =

ρ

πfµrµ 0

(5-4)

where ρ is the resistivity of the bonding wire material and f is the frequency. The

resistive impedance of bonding wires is ignored since the length of bonding wires is very

short which means the associated resistance is very low.

To calculate the values of bonding wire impedance, the parameter values are

shown in Table 5.1. The material of bonding wires is gold.

Table 5.1. The parameter values for the model of bonding wires

Parameter

Value

Unit

µo

4π×10-7

H/m

µr

1

H/m

ρ

2.44×10-8

Ohms/m

l

3

mm

d

0.0363

mm

61

The PCB is specially designed and built for the driver testing. As shown in Figure

5.2, the board is designed as small as possible to minimize the parasitics. However, the

board has parasitic impedance in itself that should be modeled for realistic prediction of

the signal behavior. The size of the board is 4.5 cm × 4.5 cm. The model of metal strips

in the board is constructed by ADS with five-ladder structure. In the board, the metal

strip is partitioned into five parts as illustrated in Figure 5.3 for modeling since the metal

strip is tapered to fit SMA connectors and bonding wires.

Figure 5.2. The PCB for the driver testing.

62

l1 l2 l3 l4

w1

l5

w2

w3

Figure 5.3. The diagram of metal strip in PCB

To extract the values of the board impedance, the lengths and widths are shown in

Table 5.2. The material of the metal strip is tin.

Table 5.2. The length and width of metal strips in PCB

Parame

l1

l2

l3

l4

l5

w1

w2

w3

59.421

16.745

21.33

27.735

620.18

10.01

29.981

49.894

mil

mil

mil

mil

mil

mil

mil

mi.

-ter

Value

L1

R1

B ia s W ire

L2

C2

R2

L3

C3

R3

C4

R4

L5

R5

L6

R6

C5

C6

L7

W ire

B o a rd T ra c e

L4

B o n d in g

P rin te d C irc u it

63

Figure 5.4. The final equivalent model of packaging

64

The final equivalent model of packaging is shown in Figure 5.4. It consists of

bonding wire, board line, and bias wire parasitics. The value of parasitic impedance in the

model is given in Table 5.3.

Table 5.3. The value of parasitic model

Parameter

Value

Parameter

Value

L1

105 nH

C4

0.367874 pF

L2

1.38664 nH

C5

0.367874 pF

L3

1.38664 nH

C6

0.367874 pF

L4

1.38664 nH

R1

0.1 Ω

L5

1.38664 nH

R2

0.0280365 Ω

L6

1.38664 nH

R3

0.0280365 Ω

L7

3.996 nH

R4

0.0280635 Ω

C2

0.367874 pF

R5

0.0280635 Ω

C3

0.367874 pF

R6

0.0280635 Ω

65

5.3 Differential Topology

As described in Chapter 5.2, the performance of the IC is limited by the