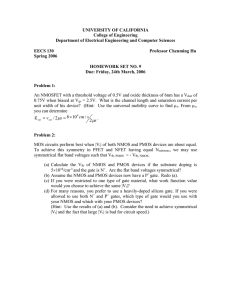

11.1

Unit 11 – Semiconductor

Technology

With focus on MOS Transistors

11.2

Evolution of transistor in ICs

• BJT invention, Bell Labs, 1947

• Single transistor, TI, 1958

• CMOS gate, Fairchild, 1963

• First processor, Intel, 1970

• Very Large Scale Integration, 1978

•

Up to 20k transistor

• Ultra Large Scale Integration, 1989

•

More than 1 million per chip

• System-on-Chip, 2002-2015

•

Form 20-30 million transistors to several

billion transistors

11.3

Invention of the Transistor

• Vacuum tubes ruled in first half of 20th century

Large, expensive, power-hungry, unreliable

• 1947: first point contact transistor

– John Bardeen and Walter Brattain at Bell Labs

– See Crystal Fire

by Riordan, Hoddeson

11.4

Growth Rate

• 53% compound annual growth rate over 50

years

• No other technology has grown so fast so long

• Driven by miniaturization of transistors

– Smaller is cheaper, faster, lower in power!

– Revolutionary effects on society

[Moore65]

Electronics Magazine

11.5

Minimum Feature Size

11.6

Intel 4004 Micro-Processor

1971

1000 transistors

1 MHz operation

11.7

Intel Core I7

2nd Gen. Intel Core i7 Extreme Processor for

desktops launched in Q4 of 2012

• #cores/#threads: 6/12

• Technology node: 32nm

• Clock speed: 3.5 GHz

• Transistor count: Over one billion

• Cache: 15MB

• Addressable memory: 64GB

• Size: 52.5mm by 45.0mm mm2

11.8

ARM Cortex A15

ARM Cortex A15 in 2011 to 2013

• 4 cores per cluster, two clusters per chip

• Technology node: 22nm

• Clock speed: 2.5 GHz

• Transistor count: Over one billion

• Cache: Up to 4MB per cluster

• Addressable memory: up to 1TB

• Size: 52.5mm by 45.0mm

8

11.9

Cortex-A72

11.10

IBM z13 Storage Controller

11.11

Annual Sales

• >1019 transistors manufactured in 2008

– 1 billion for every human on the planet

11.12

Cost per Transistor

cost:

¢-per-transistor

1

0.1

Fabrication capital cost per transistor (Moore’s law)

0.01

0.001

0.0001

0.00001

0.000001

0.0000001

1982

1985

1988

1991

1994

1997

2000

2003

2006

2009

2012

11.13

Internet Traffic Growth

11.14

Transistor Types

• Bipolar transistors

– npn or pnp silicon structure

– Small current into very thin base layer controls

large currents between emitter and collector

– Base currents limit integration density

• Metal Oxide Semiconductor Field Effect

Transistors

– nMOS and pMOS MOSFETS

– Voltage applied to insulated gate controls current

between source and drain

– Low power allows very high integration

11.15

NMOS and PMOS Transistors

• NMOS conducts when gate input is at a high voltage

(logic ‘1’)

• PMOS conducts when gate input is at a low voltage

(logic ‘0’)

Output

( Drain )

Controlling

Input

( Gate )

Source

Controlling

Input

( Gate)

Output

( Drain)

Source

NMOS

(On if G=1)

Indicates a

P-type

PMOS

(On if G=0)

11.16

NMOS and PMOS Transistors

NMOS Transistors

1

0

Current Flows

(Small resistance between

source and output )

No Current Flows

( Large resistance between

source and output )

PMOS Transistors

0

Current Flows

(Small resistance between

source and output)

1

No Current Flows

( Large resistance between

source and output)

11.17

NMOS Transistors in

Series/Parallel Connection

• Transistors can be thought as a switch controlled by its

gate signal

• NMOS switch closes when switch control input is high

A

B

X

Y

Y = X if A and B

A

X

B

Y

Y = X if A OR B

NMOS Transistors pass a “strong” 0 but a “weak” 1

11.18

PMOS Transistors in

Series/Parallel Connection

• PMOS switch closes when switch control input is low

A

B

X

Y

Y = X if A AND B = A + B

A

X

B

Y

Y = X if A OR B = AB

PMOS Transistors pass a “strong” 1 but a “weak” 0

11.19

NMOS and PMOS Transistors

• NMOS transistors work best when one

terminal is connected to a low voltage

source, pulling the other terminal

down to that voltage

– Normally, source terminal is connected to

GND=0V

• PMOS transistors work best when one

terminal is connected to a high

voltage source, pulling the other

terminal down to that voltage

– Normally, source terminal is connected to

power supply voltage (+5V, +3V, etc.)

0V

NMOS

+3V

PMOS

11.20

CMOS

• Complimentary MOS (CMOS)

– Use PMOS to connect output to high

voltage source

+3V

• We call this the Pull-Up Network

– Use NMOS to connect output to low

voltage source (usually = GND)

PMOS

Pull-Up

Network

• We call this the Pull-Down Network

– Either PMOS or NMOS should

create a conductive path to

output, but not both

Pull-up OFF

Inputs

Pull-up ON

Pull-down OFF Z (float)

1

Pull-down ON

X (crowbar)

0

Output

NMOS

Pull-Down

Network

11.21

Signal Strength

• Strength of signal

– How close it approximates ideal voltage source

• VDD and GND rails are strongest 1 and 0

• nMOS passes strong 0

– But degraded or weak 1

• pMOS passes strong 1

– But degraded or weak 0

• Thus nMOSes are best for the pull-down

network, pMOSes are best for the pull-up

11.22

CMOS Inverter

• Inverter can be formed using

one PMOS and NMOS

transistor

• The input value connects to

both gate inputs

• The output is formed at the

junction of the drains

Vdd

A

A

GND

11.23

CMOS Inverter

• When input is 1, NMOS conducts and output is

pulled down to 0V (GND)

• When input is 0, PMOS conducts and output is

pulled up to 3V (VDD)

Vdd

Vdd

OFF

1

0

ON

0

1

ON

OFF

GND

GND

11.24

CMOS ‘NAND’ Gate

• If A and B = 1, the output

of the first circuit is pulled

to 0 (opposite of AND

function)

• If A or B = 0, the output of

the first circuit is pulled to

1 (opposite of AND

function)

Vdd

A

Vdd

B

A•B

A

B

NAND

portion

GND

NAND

11.25

CMOS ‘AND’ Gate

• If A and B = 1, the output

of the first circuit is pulled

to 0 (opposite of AND

function)

• If A or B = 0, the output of

the first circuit is pulled to

1 (opposite of AND

function)

• Inverter is then used to

produce true AND output

Vdd

A

Vdd

Vdd

B

A•B

A

A•B

B

NAND

portion

GND

NAND

Inverter

GND

Inverter to

produce AND

11.26

CMOS ‘NOR’ Gate

• If A or B = 1, the output of

the first circuit is pulled to

0 (opposite of OR

function)

• If A and B = 0, the output

of the circuit is pulled to 1

(opposite of OR function)

Vdd

NOR

portion

A

B

A+B

A

B

GND

NOR

GND

11.27

CMOS ‘NOR’ Gate

• If A or B = 1, the output of

the first circuit is pulled to

0 (opposite of OR

function)

• If A and B = 0, the output

of the circuit is pulled to 1

(opposite of OR function)

• Inverter is then used to

produce true OR output

Vdd

Vdd

NOR

portion

Inverter

A

A+B

B

A+B

A

B

GND

GND

OR

GND

11.28

CMOS (cont.)

• Complementary CMOS gates always produce 0 or 1

• Ex: NAND gate

– Series nMOS: Y=0 when both inputs are 1

– Thus Y=1 when either input is 0

– Requires parallel pMOS

Y

A

B

• Rule of Conduction Complements

– Pull-up network is the dual (complement) of pull-down

– Parallel -> series, series -> parallel

11.29

Compound Gates

• How could you build this gate?

• You could try building each gate

separately

– Two AND gates = ____ transistors

– One NOR gate = ____ transistors

• Or you could take build it as a

single compound gate.

11.30

Compound Gates

• Compound gates can do any inverting function

• Ex: AND-OR-INVERT (AOI)

Y = A•B + C•D

A

C

A

C

B

D

B

D

(a)

A

(b)

B C

D

(c)

D

A

B

(d)

C

D

A

B

A

C

B

D

A

B

C

D

Y

(e)

C

(f)

Y

11.31

Compound Gate Approach

• For an inverting function just look at the

expression (w/o the inversion) and…

– Implement the PDN using:

• Series connections for AND

• Parallel connections for OR

– Implement PUN as dual of PDN

• Swap series and parallel

• If function is non inverting just add an inverter

at the output

11.32

Compound Gate Example

Y = D • (A + B + C)

A

B

C

D

Y

D

A

B

C

11.33

Compound Gate Example

B

A

C

D

OUT = D + A • (B + C)

A

D

B

C

11.34

Compound Gate Example (cont.)

B

A

C

This is really a CMOS

inverter (2 transistors) but

we just show it this way to

save space and focus on the

1st stage cell

D

OUT = D + A • (B + C)

A

D

B

C

11.35

Another Compound Gate Example

OUT = A•D + B(C + E)

Add an inverter at the output

OUT = A•D + B(C + E)

Implement inverting function

using compound CMOS

gate

11.36

BACKUP

11.37

Series and Parallel Summary

•

•

•

•

a

a

nMOS: 1 = ON

pMOS: 0 = ON

Series: both must be ON

Parallel: either can be ON

0

g1

g2

(a)

(b)

a

g1

g2

(c)

a

g1

g2

b

0

1

b

b

OFF

OFF

OFF

ON

a

a

a

a

0

1

1

1

0

1

b

b

b

b

ON

OFF

OFF

OFF

a

a

a

a

0

0

b

1

b

0

b

1

1

0

g2

a

b

a

g1

a

0

0

b

(d)

a

0

1

1

0

1

1

b

b

b

b

OFF

ON

ON

ON

a

a

a

a

0

0

0

1

1

0

1

1

b

b

b

b

ON

ON

ON

OFF

11.38

Complementary CMOS

• Complementary CMOS logic gates

– nMOS pull-down network

– pMOS pull-up network

– a.k.a. static CMOS

Pull-up OFF

Pull-up ON

Pull-down OFF Z (float)

1

Pull-down ON

X (crowbar)

0

pMOS

pull-up

network

inputs

output

nMOS

pull-down

network

11.39

CMOS (cont.)

• Complementary CMOS gates always produce 0 or 1

• Ex: INVERTER gate

– A=0: nMOS is OFF, pMOS is ON, OUT is _______

– A=1: nMOS is ON, pMOS is OFF, OUT is _______

11.40

CMOS (cont.)

• Complementary CMOS gates always produce 0 or 1

• Ex: NOR gate

– Parallel nMOS: Y=0 when either input is 1

– Thus Y=1 when both inputs are 0

– Requires parallel nMOS

• Rule of Conduction Complements

– Pull-up network is complement (aka dual) of pull-down

– Parallel -> series, series -> parallel

0

0