Product Preview

PE3282

1.1-GHz / 510-MHz

Dual Fractional-N

PLL IC for

Frequency Synthesis

Applications

Features

•

•

•

•

• Modulo-32 fractional-N main

Cellular handsets

Cellular base stations

Spread-spectrum radio

Cordless phones

Description

The PE3282A is a dual fractional-N phase-locked-loop integrated

circuit for frequency synthesis fabricated on Peregrine’s patented

UTSi® CMOS process. Each PLL includes a prescaler, phase

detector, charge pump and on-board fractional spur compensation. The 32/33 RF prescaler (PLL1) operates up to 1.1 GHz and

the 16/17 IF prescaler (PLL2) operates up to 510 MHz.

counters

• On-board fractional spur

compensation: no tuning

required, stable over

temperature

• Improved phase noise

compared to integer-N

architectures

• Low power — 7.5 mA at 3 V

The PE3282A provides fractional-N division with power-oftwo denominator values up to 32. This allows comparison frequencies up to 32 times the channel spacing, providing a lower

phase-noise floor than integer PLLs.

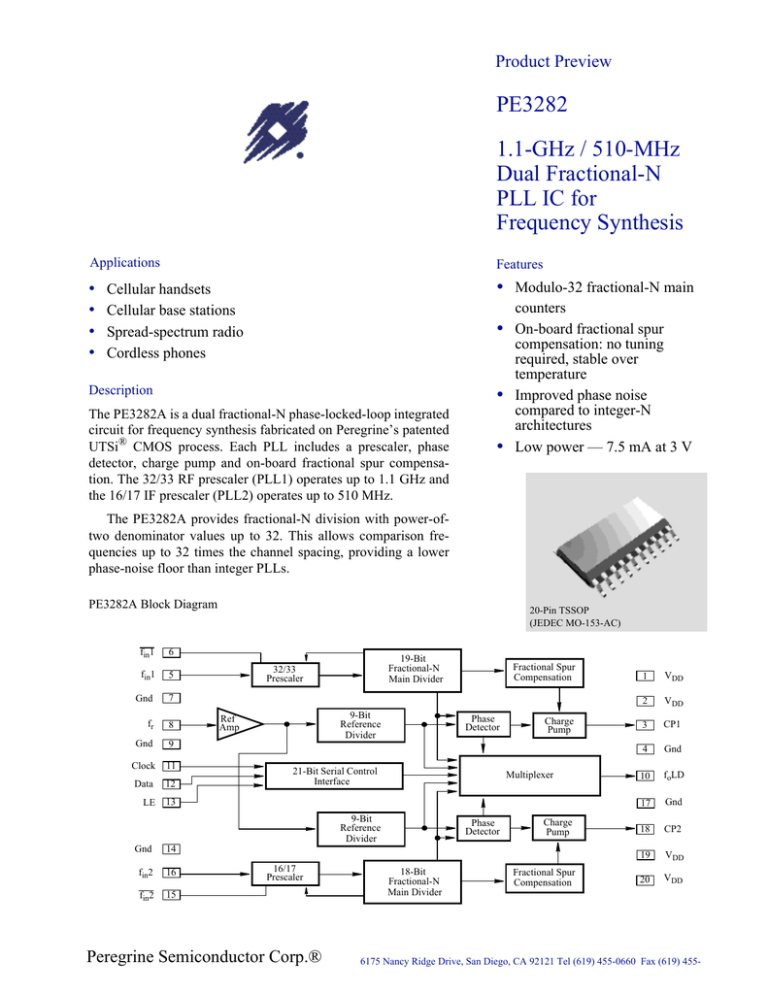

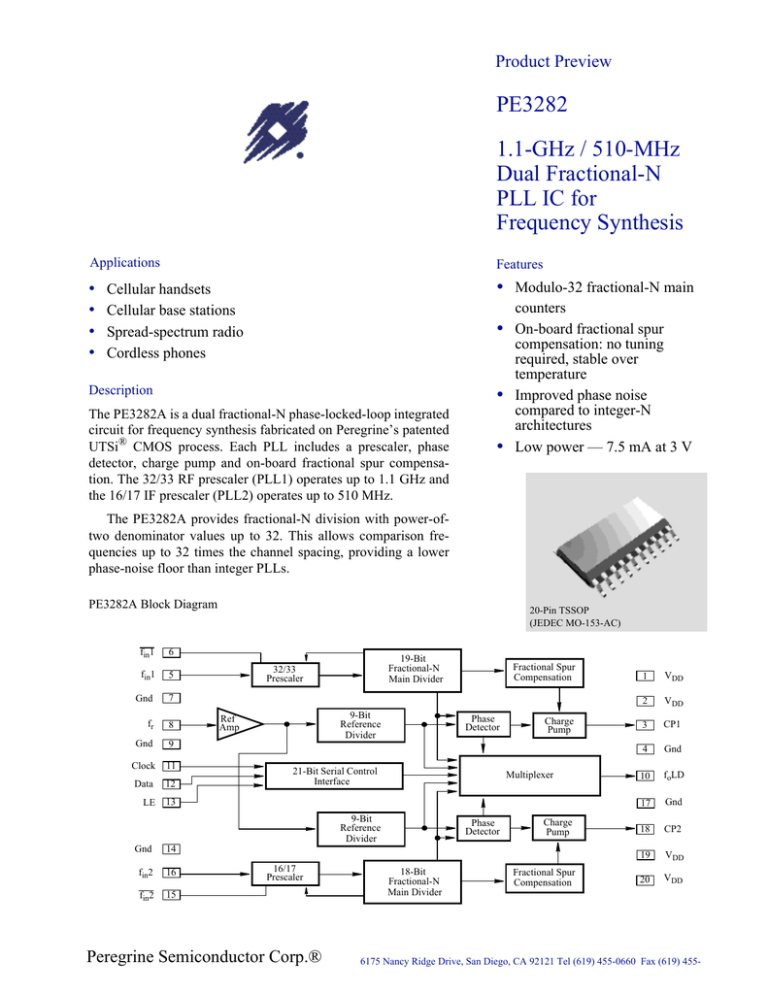

PE3282A Block Diagram

fin1

20-Pin TSSOP

(JEDEC MO-153-AC)

6

fin1

5

Gnd

7

fr

8

Gnd

9

Clock

11

Data

12

LE

13

19-Bit

Fractional-N

Main Divider

32/33

Prescaler

9-Bit

Reference

Divider

Ref

Amp

Phase

Detector

21-Bit Serial Control

Interface

14

fin2

16

fin2

15

16/17

Prescaler

Peregrine Semiconductor Corp.®

Charge

Pump

Multiplexer

9-Bit

Reference

Divider

Gnd

Fractional Spur

Compensation

Phase

Detector

18-Bit

Fractional-N

Main Divider

Charge

Pump

Fractional Spur

Compensation

1

VDD

2

VDD

3

CP1

4

Gnd

10

foLD

17

Gnd

18

CP2

19

VDD

20

VDD

6175 Nancy Ridge Drive, San Diego, CA 92121 Tel (619) 455-0660 Fax (619) 455-

Pin Configuration:

TSSOP (JEDEC MO-153-AC

VDD

1

20

VDD

VDD

2

19

VDD

CP1

3

18

CP2

Gnd

4

17

Gnd

fin1

5

16

fin2

fin1

6

15

fin2

Gnd

7

14

Gnd

fr

8

13

LE

Gnd

9

12

Data

foLD 10

11

Clock

VDD

CP1, CP2

Gnd

fin1, fin2

fin1, fin2

fr

foLD

Clock

Data

LE

Positive power supply

Charge Pump output for PLL1, PLL2

Ground

RF input for PLL1, PLL2

RF input bias bypass for PLL1, PLL2

Reference frequency input

fc and fp output (multiplexed), Lock Detect

Clock for serial data input

Data input for serial shift register

Load Enable

Characteristics

VDD = 3.0 V, -40o C < TA < 85o C, unless specified.

Symbol

Parameter

VDD

Supply voltage

IDD

Operational supply current;

PLL1 (RF) enabled

PLL2 (IF) enabled

PLL1and PLL2 enabled

Conditions

Min

Typ

2.7

Max

Unit

3.6

V

VDD = 2.7 to 3.6 V

5

2.5

7.5

mA

mA

mA

Main Divider (Including Prescaler)

fin1, fin2

Operating frequency

PLL1

PLL2

100

45

1,100

510

MHz

MHz

Pfin1,

Pfin2

Input level range

External AC coupling

-10

5

dBm

50

MHz

Reference Divider

fr

Reference frequency input

Vfr

Input sensitivity

External AC coupling (Note 1)

Drive current

VCP = VDD /2

Leakage current

0.5 < VCP < VDD - 0.5 V

0.5

VP-P

Charge Pump

ICP - Source

ICP - Sink

ICPL

-5

-70

µA

70

µA

5

nA

10

MHz

Serial Control Interface

fClock

Serial data clock frequency

Product Preview: This publication provides information on a

product that is in a formative or design stage. Specifications or features described here are design target specifications for product

development and may change in any manner without notice.

UTSi, the Peregrine logotype, Microcommunicator, and Peregrine Semiconductor Corp. are registered trademarks of Peregrine Semiconductor Corp. PE3282, and all PE product prefixes are trademarks of Peregrine Semiconductor Corp, Copyright © 1996 Peregrine Semiconductor Corp. All

rights reserved.

Document 70/00001~03

Represented by:

DRAFT COPY: For Internal Review

Revision History

Revision

Date

Change

Description

01

11/21/96

DCN#:

00031

12/6/96

12/9/96

Page 1

Page 2

Page 1

Page 1

Page 2

First page header, text, features and applications revised according to data sheet changes.

IDD Typ changed from 3 and 8 changed to 2.5 and 7.5. Also, added Note 1.

Changed 23-bit serial control interface in diagram to 21-bit.

Change at 1.1 to up to 1.1 in text. Move 20 pin box to right side of diagram.

Change Input level range to Input sensitivity

02

5-7-97

All pages

1. Change part name to PE3282A 2. Change document number to 70/00001~02.

8-7-97

All pages

(1) All pages: replace string “PE3282” with string “PE3282A” , (2) All pages: change

document # to 70/00001~03, (3) Page 2: Characteristics. Change Charge Pump output to

Icp-source = -70 uA typical, (4) Page 2: Characteristics.. Change Charge Pump outputs to

Icp-sink = 70 uA typical

DCN#00068

03

DCN#00100

Peregrine Semiconductor Corp.®

Document 70/00001~03

6175 Nancy Ridge Drive, San Diego, CA 92121 Tel (619) 455-0660 Fax (619) 455-