PLACEMENT FOR FAST AND RELIABLE THROUGH-SILICON

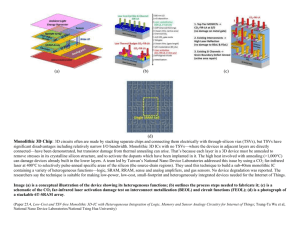

advertisement