Serial Peripheral Interface (SPI)

advertisement

Microprocessors and Microcontrollers

Serial Peripheral Interface (SPI)

EE3954

by

Maarten Uijt de Haag, Tim Bambeck

SPI.1

I/O - Communications

• Serial I/O:

I/O Pin

1

1

Microcontroller

0

1

1

1

0

1

time

• Parallel I/O:

1

I/O Pins

1

0

Microcontroller

1

1

Advantage serial:

Only need one data line and ground.

Advantage parallel:

Multiple bits are sent or received

at the same time.

1

0

1

SPI.2

Serial Communications

Asynchronous vs. Synchronous

Data Lines

Device

(A)

Data Lines

Device

(B)

Device

(A)

Device

(B)

Common

Clock Line

Notes #12

Universal Synchronous / Asynchronous

Receiver Transmitter (USART)

SPI.3

Serial Communications

Synchronous

Serial Peripheral Interface (SPI)

Inter-Integrated Circuit (SPI)

Both are part of the

Master Synchronous Serial Port (MSSP)

Pinouts on the PIC16F877

SPI.4

PIC Micro

Serial Peripheral Interface (SPI) – Four Wire

Microcontroller

(Master)

Receive Register

Microcontroller

(Slave)

SDO

SDI

SDI

SDO

SCK

SCK

Receive Register

Serial Buffer

SDI: Serial Data In

SDO: Serial Data Out

SCK: Serial Clock

SS: Slave Select

SS

Only for Slave device

SPI.5

SPI Pins Alternative Names

Microcontroller

(Master)

Microcontroller

(Slave)

MOSI

MISO

Receive Register

Serial Buffer

Receive Register

SCLK

MOSI: Master Output, Slave Input

MISO: Master Input, Slave Output

SLCK: SPI Clock

SS

Only for Slave device

SPI.6

Slave Select Purpose

SPI Master

Microcontroller

SDO

SDI

SCK

SS1

SS2

SS3

To select which peripheral device

(slave device) the

microcontroller want to talk to.

SDI

SDO

SCK

SS

SPI

Slave #1

SDI

SDO

SCK

SS

SPI

Slave #2

SDI

SDO

SCK

SS

SPI

Slave #3

SPI.7

MSSP SPI

PORTC<4>

Serial Data In

Serial Data Out

PORTC<5>

Slave Select

Master:

TRISC<5> = 0;

TRISC<3> = 0;

TRISC<4> don’t worry

Slave:

TRISC<5> = 0;

Serial Clock

TRISC<3> = 1;

TRISC<4> don’t worry

TRISA<5> = 1; // input

Set pin as Digital pin in ADCON1

PORTA<5>

PORTC<3>

SPI.8

Example

Interface with Accelerometer

PIC16F877

Peripheral Device

(3-axis accelerometers)

RE2

SDO

SDI

SCK

SPI.9

SPI Clock

Master Mode

SPI clock speeds can go up to

100MHz typically, in the 16F877,

max speed is fosc/4.

Serial Clock

SPI.10

Master Mode

Clock rate: Fosc/4 (or Tcy)

Fosc/16 (or 4*Tcy)

Fosc/64 (or 16*Tcy)

Timer2 output/2

SPI.11

SSPCON

SPI.12

SPI Configuration

SPI.13

Configuration

of Clock

SPI Configuration

CKE = Clock Phase (CPHA)

CKP = Clock Polarity (CPOL)

SPI.14

SSP Status Register

Clock Phase (CPHA)

Opposite of CKE

0

SPI.15

SSP Configuration Register

SPI.16

SSP Configuration Register

Clock Polarity (CPOL)

SPI.17

Example

Interface with Accelerometer

PIC16F877

Peripheral Device

SPI Slave

(3-axis accelerometers)

RE2

SDO

SDI

SCK

SPI.18

Example –ADXL345* Write

Idle clock = high level => CKP = 1

Bits at rising edge => CKE = 0

*Analog Devices 3-axis accelerometer = Slave Device

SPI.19

Example –ADXL345* Read

SMP = 0

*Analog Devices 3-axis accelerometer = Slave Device

SPI.20

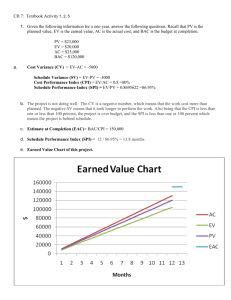

Example Configuration

0

0

0

0

0

1

0

0

0

0

Read-only bits: leave as defaults

1

0

0

0

0

0

Enable SSP

Assume: 4MHz Oscillator, peripheral device clocked at 1MHz

SPI.21

SSPCON

SPI.22

Initialization with Interrupts

C-code

TRISC5 = 0;

TRISC3 = 0;

SSPSTAT = 0b00000000;

SSPCON = 0b00110000;

SSPIE = 1;

SSPIF = 0;

PEIE = 1;

GIE = 1;

Assembly-code

bsf

movlw

movwf

bcf

bcf

bsf

bcf

bcf

movlw

movwf

STATUS, RP0

b’00000000’

SSPSTAT

TRISC,5

TRISC,3

PIE1, SSPIE

STATUS, RP0

PIR1, SSPIF

b’00110000’

SSPCON

bsf

bsf

INTCON, PEIE

INTCON, GIE

SPI.23

Over-writing ‘getch’ and ‘putch’

Wait until the SSPIF flag

is set (= 1)

char getch()

{

while(!SSPIF) continue;

}

void putch(char byte)

{

while(!SSPIF) continue;

SSPBUF = byte;

}

return SSPBUF;

Wait until the SSPIFflag

is cleared (= 0)

SPI.24

Slave Mode

SPI.25

Slave Mode

SPI.26

Advantages

•

•

•

•

•

•

•

•

•

Full duplex communication;

Higher throughput than I2C or SMBus;

Complete protocol flexibility for the bits transferred;

Not limited to 8-bit words;

Arbitrary choice of message size, content, and

purpose;

Extremely simple hardware interfacing;

Typically lower power requirements than I²C or SMBus

due to less circuitry (including pull up resistors);

No arbitration or associated failure modes;

Slaves use the master's clock, and don't need precision

oscillators.

SPI.27

Advantages

• Slaves don't need a unique address unlike I2C

• Transceivers are not needed;

• Uses only four pins on IC packages, and wires in board

layouts or connectors, much fewer than parallel

interfaces;

• At most one unique bus signal per device (chip select);

all others are shared;

• Signals are unidirectional allowing for easy Galvanic

isolation;

• Not limited to any maximum clock speed, enabling

potentially high throughput.

SPI.28

Disadvantages

• Requires more pins on IC packages than I²C, even in

the three-wire variant

• No in-band addressing; out-of-band chip select signals

are required on shared buses

• No hardware flow control by the slave (but the master

can delay the next clock edge to slow the transfer

rate)

• No hardware slave acknowledgment (the master could

be transmitting to nowhere and not know it)

• Supports only one master device

• No error-checking protocol is defined

SPI.29

Disadvantages

• Generally prone to noise spikes causing faulty

communication

• Without a formal standard, validating conformance is

not possible

• Only handles short distances compared to RS-232,

RS-485, or CAN-bus

• Many existing variations, making it difficult to find

development tools like host adapters that support

those variations

• SPI does not support hot plugging (dynamically adding

nodes).

SPI.30