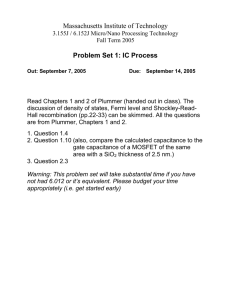

MOS Capacitances

advertisement

Announcements EE141-Fall 2007 Digital Integrated Circuits Lab 3 this week! Lab 4 next week Homework Homework #3 due Thurs. #4 due next Thurs. Lecture 7 MOS Capacitances EE141 EECS141 1 Lecture #7 1 EE141 EECS141 Lecture #7 2 2 Class Material Last lecture CMOS inverter VTC MOS switching Today’s MOS Capacitances lecture MOS capacitances Inverter delay Reading EE141 EECS141 (3.3.2, 5.4, 5.5) 3 Lecture #7 3 MOS Capacitances CGS 4 (per area) from gate across the oxide is W·L·Cox, where Cox=εox/tox CGD = CGCD + CGDO S D CGB = CGCB Distribution Lecture #7 between terminals is complex Capacitance is really distributed – To get a useful model have to lump it to the terminals CDB = Cdiff There are a number of operating regions – Way off, off, transistor linear, transistor saturated B EE141 EECS141 4 Capacitance = CGCS + CGSO = Cdiff Lecture #7 Gate Capacitance G CSB EE141 EECS141 5 5 EE141 EECS141 Lecture #7 6 6 Transistor In Cutoff Transistor In Cutoff (cont’ (cont’d) G S G S D W D W L L C OL C GB C OL C OL C GB C OL xj xj C jSB C jSB C jDB When the transistor is off, no carriers in channel to form the other side of the capacitor. – Substrate acts as the other capacitor terminal – Capacitance becomes series combination of gate oxide and depletion capacitance EE141 EECS141 When |VGS| < |VT|, total CGCB much smaller than W·L·Cox – Usually just approximate with CGCB = 0 in this region. (If VGS is “very” negative (for NMOS), depletion region shrinks and CGCB goes back to ~W·L·Cox) 7 7 Lecture #7 C jDB Transistor in Linear Region EE141 EECS141 Transistor in Saturation Region G G S S D W C OL CG L C OL C OL xj C JC CG C OL xj C JC C jSB C jDB LD C jDB LD Channel is formed and acts as the other terminal – CGCB drops to zero (shielded by channel) – Changing either voltage changes the channel charge 9 9 Lecture #7 Changing source voltage doesn’t change VGC uniformly – E.g. VGC at pinch off point still VTH Model by splitting oxide cap equally between source and drain EE141 EECS141 D W L C jSB 8 8 Lecture #7 Bottom line: CGCS ≈ 2/3·W·L·Cox EE141 EECS141 Lecture #7 10 10 Gate Capacitance Transistor in Saturation Region (cont’ (cont’d) G S D W L C OL CG C JC C jSB C OL xj C jDB LD Drain voltage no longer affects channel charge – Set by source and VDS_sat Cgate vs. VGS (with VDS = 0) If change in charge is 0, CGCD = 0 EE141 EECS141 Lecture #7 11 11 EE141 EECS141 Cgate vs. operating region Lecture #7 12 12 Gate Overlap Capacitance Gate Fringe Capacitance Polysilicon gate Fringing fields Gate oxide Source Drain xd n+ tox xd Ld n+ W L n+ n+ n+ n+ Cross section Gate-bulk overlap Cross section CO = Cox ⋅ xd Top view COV not just from metallurgic overlap – get fringing fields too Off/Lin/Sat Æ CGSO = CGDO = CO·W Typical value: ~0.2fF·W(in µm)/edge 13 Lecture #7 Diffusion Capacitance 1.0 Junction caps are nonlinear Side wall – Area cap – Cbottom = Cj·LS·W Source W – CJ is a function of junction bias ND Bottom Sidewalls xj – Perimeter cap – Csw = Cjsw·(2LS+W) SPICE model equations: Channel Substrate NA 0.7 0.6 N+ junction area N+ junction perimeter P+ junction area P+ junction perimeter 0.4 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 Node voltage (V) – Area CJ = area × CJ0 / (1+ |VDB|/φΒ – Perimeter CJ = perim × CJSW / (1 + |VDB|/φΒ)mjsw – Gate edge CJ = W × CJgate / (1 + |VDB|/φΒ)mjswg – Cge = Cjgate·W – Usually automatically included in the SPICE model Lecture #7 0.8 )mj GateEdge EE141 EECS141 0.9 0.5 Side wall LS 14 14 Lecture #7 Junction Capacitance (2) NA+ Bottom EE141 EECS141 Capacitance [arbitrary units] EE141 EECS141 13 How do we deal with nonlinear capacitance? 15 15 Linearizing the Junction Capacitance EE141 EECS141 16 16 Lecture #7 Capacitance Model Summary Replace non-linear capacitance by large-signal equivalent linear capacitance which displaces equal charge over voltage swing of interest Gate-Channel Capacitance CGC ≈ 0 CGC = Cox·W·Leff (|VGS| < |VT|) (Linear) CGC = (2/3)·Cox·W·Leff (Saturation) – 50% G to S, 50% G to D – 100% G to S Gate Overlap Capacitance CGSO = CGDO = CO·W Junction/Diffusion Capacitance Cdiff = Cj·LS·W + Cjsw·(2LS + W) + CjgW EE141 EECS141 Lecture #7 17 17 EE141 EECS141 (Always) Lecture #7 (Always) 18 18 1.8 Capacitances in 0.25 µm CMOS Process Simplified Model Capacitance models important for analysis and intuition – But often need something simpler to work with Simpler model: – Lump together as effective linear capacitance to (ac) ground – In most processes: Cg = Cd = 1.5 – 2fF·W(µm) Vin Vout Vin Vout CL EE141 EECS141 19 19 Lecture #7 Model Calibration - Capacitance EE141 EECS141 Model Calibration for Delay Can calculate Cg, Cd based on tech. parameters A – But these models are simplified too Cload Delay1 Another approach: – Tune (e.g., in spice) the linear capacitance until it makes the simplified circuit match the real circuit – Matching could be for delay, power, etc. – Make inverter fanout 4 (will see why in 2 lectures) – Adjust Cload until Delay1 = Delay2 For diffusion capacitance EE141 EECS141 – Replace inverter “A” with a diffusion capacitance load Delay2 Match 21 21 Lecture #7 4 EE141 EECS141 22 22 Lecture #7 The Miller Effect Delay Calibration 1 Delay2 Match For gate capacitance: Cload Delay1 20 20 Lecture #7 16 As Vin increases, Vout drops 64 – Once get into the transition region, gain from Vin to Vout > 1 Cgd1 ∆V Vout ∆V Vin So, Cgd experiences voltage swing larger than Vin Delay "Edge Shaper" Load ??? M1 – Which means you need to provide more charge – Makes Cgd look larger than it really is Why did we need that last inverter stage? Known as the “Miller Effect” in the analog world EE141 EECS141 Lecture #7 23 23 EE141 EECS141 Lecture #7 24 24