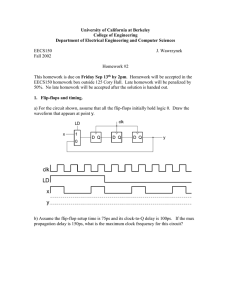

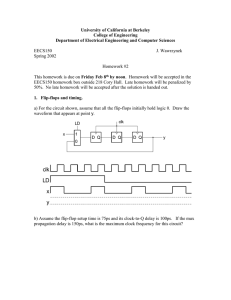

clk LD x y

University of California at Berkeley

College of Engineering

Department of Electrical Engineering and Computer Sciences

EECS150

Spring 2003

J. Wawrzynek

Homework #5

This homework is due on Thursday February 27 th

. Homework will be accepted in the

EECS150 homework box outside 125 Cory Hall. Late homework will be penalized by

50%. No late homework will be accepted after the solution is handed out.

1. Flip-flops and timing. a) For the circuit shown, assume that all the flip-flops initially hold logic 0. Draw the waveform that appears at point y .

LD clk x 1

0

D Q D Q D Q y clk

LD x y b) Assume the flip-flop setup time is 75ps and its clock-to-Q delay is 100ps. If the mux propagation delay is 150ps, what is the maximum clock frequency for this circuit?

2. Logic gate timing waveforms.

Below is shown the waveforms corresponding to a low-to-high and a high-to-low transition for an inverter. Draw approximate transition wavefoms for the other situations shown below. Assume that all transistors in all the gates and inverters are of the same strength.

Vx x t a) Vx initially is high, set a=b= high.

Vx a b x t b) Vx initially is low, set a= high , b= low

Vx a b x t c) Vx initially is low, set a=b= low.

Vx a b x t

d) Show both transitions. x

Vx t

3. Gate delay.

Consider a CMOS AND gate constructed as a NAND gate followed by an inverter.

Assume the inverter propagation delay is expressed as follows:

τ

P

=

50

+

100

⋅ f where f is the fanout of the inverter, expressed in number of transistor-gate inputs

(inverters contribute 2 to f , one input of 2-input gates contribute 2,). Assume this inverter has the same propagation delay for both low-to-high and high-to-low transistions.

The NAND gate propagation delay is expressed as:

τ

PLH

=

100

+

75

⋅

τ

PHL

=

100

+

125

⋅ f f

For the low-to-high and high-to-low transitions, respectively. Write expressions for the propagation delay of the AND gate:

τ

PLH

=

τ

PHL

=

4. Flip-flop delay.

Consider the edge-triggered flip-flop circuit shown below. Assume that all the transistors in the flip-flop circuit are of the same size. Ignore delay due to wires. The propagation delay of the tri-state buffer and the inverter, respectively, can be expressed as:

T

T S-LH

= 4 + 4F delay for tri-state buffer low to high transition

T

T S-HL

= 2 + 2F

T

INV-LH

= 2 + 2F

T

INV-HL

= 1 + F delay for tri-state buffer high to low transition delay for inverter low to high transition delay for inverter high to low transition where F is the fan-out in units of gate inputs (one n-type and one p-type transistor gate connection). The tri-state buffer delay is the same for both the in-to-out delay and the e-to-out delay. clk

D clk x

TS1 INV1

TS2 clk

TS3 INV2

TS4 clk

Q

in e' e out e in out

Tri-state

Buffer

V

V t

a) Write an expression for the clock to Q delay (T

CQ

) of the flip-flop in terms of the fan-out of the flip-flop.

b) Determine the setup time of the flip-flop (T

SU

). c) The waveforms shown in the illustration represent the low-to-high and high-tolow transitions of a single inverter driving another single inverter. Using this as your guide, in the place provided, draw a sketch of the waveforms for both lowto-high and high-to-low transitions at node x. Assume that CLK=0.

5. Gate delay and critical path.

For the circuit shown, all transistors in the circuit are of the same strength. For the inverter, tHL = tLH = 10F ns where F (fanout) is the # of transistors being driven. The degree of fanout incurred in connecting to the D input of a flipflop is the same as the degree of fanout incurred by connecting to an inverter.

Setup time for a flipflop = 13 ns

Clock-to-Q time for a flipflop = 14 + 10F ns a) Find the critical path in the schematic. b) What is the delay associated with the critical path (excluding delay associated with the FlipFlops)? c) What is the minimum clock period with which this circuit can safely be run?

6. Gate delay waveforms.

Consider the simple combinational logic circuit shown below. Inputs a and b are applied over three clock cycles as shown in the waveforms. The clock period is 10ns. a x b clk a b x

Draw the waveform for node x in the place provided. Don’t forget to account for gate delays.