Digital Electronics 1A Additional Supervision Questions Robert

advertisement

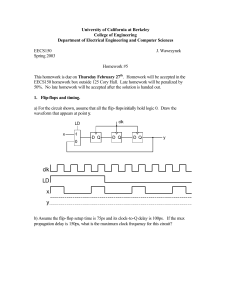

Digital Electronics 1A Additional Supervision Questions Robert Mullins 1. Inside a flip-flop and the reason for setup and hold times A schematic for a D flip-flop is shown in Figure 2. T1 and T2 below are tristate buffers, when EN=0 the output is in a tristate condition (not driven). We can build a tristate from an inverter followed by a transmission gate, as shown in Figure 1. The two components can be combined into a single gate as shown on the right. The D flip-flop is constructed from two D latches, master and slave, as discussed in your lecture notes). When the CLK is low, any value on input D will be propagated to node Z (Z will become equal to D). When the CLK goes high the current value of node Z will be latched by the first of the two latches. What delay does the setup time account for? The hold time ensures the output of the first transmission gate is held stable until the transmission gate is switched off. Figure 1: Tristate Buffer Figure 2: D flip-flop 2. The Missing Inverter Puzzle A friend asks you to build a simple piece of electronics that inverts three digital input signals. Let's call the inputs A, B, and C and outputs A', B' and C'. You go to your hardware bench and look for three inverters (the simple solution!). Unfortunately, you only find two, but discover lots of AND and OR gates. Can you still complete the task? (This problem is described in "Automated Reasoning: Introduction and Applications", Larry Wos et al, Prentice-Hall, 1984) *** Warning *** Solution on next page! 3. CMOS Logic Gates (i) Draw the truth table for the circuit shown in Figure 3. What logic function is this? (ii) Sketch a transistor-level circuit for the logic gates listed below. Remember we only ever use Ptypes to pull-up and N-types to pull-down (N-types can't pass logic 1 well and P-types can't pass logic 0 well, remember why?). For non-inverting gates we add an inverter on our output. (a) 2-input NAND gate (b) 3-input NOR gate (c) A gate whose output is ab+c Figure 3: Mystery logic gate Missing Inverter Puzzle: A possible solution 2or3 = ((A&B)+(A&C)+(B&C)) 0or1 = !(2or3) 3ones = A&B&C 1one = 0or1 & (A+B+C) 1or3 = 1one + 3ones 0or2 = !(1or3) 0ones = 0or2 & 0or1 2ones = 0or2 & 2or3 A'= 0ones + (1one & (B+C)) + (2ones & B.C) B'= … C'= … There are others approaches I believe. 4. Boolean Algebra Simplify the following expressions (where A' = not(A)) (i) F=A.B'.C'+A'.B.C'+A'B'C+A.B.C (ii) F=(X+Y).(X'+Y+Z).(X'+Y+Z') (iii) F=(A.D + A'.C).(B'.(C+B.D')) From 2011, Paper 2. Qu 1. (iv) F=(A+B'+A'.B).(A+B').A'.B (v) F=(A+B'+A'.B).C' From 2008, Paper 2. Qu 2. You could also attempt Qu. 1 from Paper 2, 2007 http://www.cl.cam.ac.uk/teaching/exams/pastpapers/y2007p2q1.pdf 5. State Machine Question Attempt Question 2, from Paper 2, 2007 http://www.cl.cam.ac.uk/teaching/exams/pastpapers/y2007p2q2.pdf 6. Design challenge Design the control logic for a vending machine (draw the state machine and derive minimised expressions for the next state functions). The machine dispenses drinks that cost 70p each and accepts fifty, twenty and ten pence pieces. A new coin is accepted on each cycle until enough money has been deposited for a drink to be dispensed and change to be returned. The outputs your FSM will generate are Dispense, Return10p, Return20p, Return30p, Return40p. I am of course happy to mark past examination questions at any point in the year.