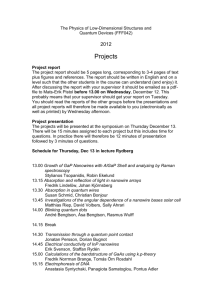

Semiconductor Nanoelectronics - JARA

advertisement

Semiconductor Nanoelectronics The main driving force for modern nanotechnology is the down scaling of semiconductor microtechnology. This is, in particular, the miniaturization of very large Silicon integration (VLSI) for ultimate performance of microprocessors. However, the approach of increasing the performance of semiconductor circuitry by down scaling of device dimensions will reach its physical limits within the next 20 years. Thus, new paths have to be explored to overcome the limits of current mainstream Si technology. This will include fundamental science on new materials, novel concepts and architectures, as well as advanced computing algorithms. The research covering these tasks of increasing complexity requires profound knowledge in Si based CMOS technology as well as expertise in semiconductor physics, material science, nanotechnology and electrical engineering. The JARA-FIT consortium offers the necessary expertise by combining scientists of physics, chemistry and engineering. In close collaboration with industry, JARA-FIT develops advanced CMOS technology, driving the approach to its physical limits. In the focus is the development of devices combining strained Si/SiGe technology, high gate dielectrics and matching gate metals. In particular, devices based on strained Si on insulator (sSOI) are in the focus of interest, since high mobility channel materials such as strained silicon yield a performance increase without scaling. The single gate sSOI technology using the “Jülich” process is currently being transferred into the industry (Figure 1). New multigate architectures such as FinFETs enable a further reduction of device dimensions. From the point of Figure 2: Development of nanowire technology view of electrostatics, silicon nanowires have attracted particular interest. They offer, in addition, the possibility to combine strained Si with a gate all around technology (Figure 2). Here, uniaxial tensile strain is shown to be beneficial for electron mobility, in particular, at low strain levels. Theoretical and experimental physics collaborate in order to predict and verify further possibilities in device improvement. Importantly, the gathered core competences in Si nano-technology for advanced CMOS devices and the indepth understanding of processes compatible to industrial production provides the basic knowledge for integration of new ideas and novel materials into future semiconductor devices (Figure 3). Sophisticated equipment for device processing and analysis is a key ingredient provided within JARA-FIT including clean room processing as well as selected highly developed analytic tools. The ion beam technology including ion implantation facilities as well as a Tandretron (Figure 4) for the analysis of strained Si nanostructures and new gate materials are outstanding examples. Along with the ongoing miniaturization of transistor dimensions allowing for ever higher packing densities within microprocessors, the power, i.e., heat management becomes an inherent problem. Thus, it is inevitable to dramatically reduce the energy consumption per switch. It appears to be possible that the heat management may limit the down scaling of standard CMOS technology. Figure 1: Electron microscopy image (TEM) of an n-type MOS short channel transistor on “Jülich” strained Silicon on Insulator fabricated at the AMD production line (Dresden) Figure 3: (a) Electron microscopy image (SEM) of a 50 nm suspended nanowire produced by reactive ion etching and underetching. (b) SEM image of a buried nanowire with a diameter of 30 nm, forming a strained channel for a gate all around Figure 4: Goniometer stage at a Tandretron ion beam line used to determine the structural properties of building blocks of sophisticated Si CMOS devices 5 Figure 5: Schematic view of a GaAs/AlGaAs core shell quantum wire with attached gate contacts for quantum information technology (left) and electron microscopy image (SEM) of a regimented array of GaAs nanowires on a GaAs (111) substrate grown by MOVPE (right) Figure 6: GaN nanowire device with two titanium gold contacts to measure the electrical transport characteristics Figure 7: Transmission-Electron-Microscopy (TEM) image of a GaN/ AlN heterostructure imbedded in a nanowire Figure 8: Three-dimensional Si-Ge quantum dot crystal fabricated by molecular beam epitaxy using templated self-assembly. The image is mounted from two electron microscopy images (SEM) and one atomic force microscopy image 6 In fact, the current trend to use multi-core processors for computing is at least partly driven by the heat management. Thus the requirement of low power consumption is one of the key elements for strategies to compete with and go beyond the current CMOS technology. Ultimately, quantum computation is considered as a convincing concept, since the integration of a relatively small number of devices already outperforms current computer technology. Within JARA-FIT the possibilities to realize quantum bits in semiconductor nanowires are explored (see article on page 9: Quantum Information). This research requires the fabrication of well defined quantum wires, mastering the device technology. Both, top-down as well as bottom-up approaches are studied using either advanced lithography to define and cut out nanostructures from a two-dimensional layer sequence or self-assembly on a structured template in order to position nanostructures on a surface. Controlled growth of quantum wires is achieved by molecular beam epitaxy (MBE) as well as by metalorganic vapor phase epitaxy (MOVPE) (Figure 5). Catalyst- free self-assembly of Ga(In)N quantum wires on Si and of Ga(In)As wires on GaAs substrates are in the focus of interest. The possibility to grow nanowires in the Al-Ga-In-N material system on Si and SiO2 coated substrates offers remarkable routes to integrate the compound semiconductor devices with new functionality into Si circuitry (Figure 6). The formation of hetero- and core shell structures within semiconductor quantum wires (Figure 7), moreover, allows the formation of quantum structures with critical dimensions of a few nanometers. These structures can be used, e.g., to integrate single photon sources for applications in quantum cryptography. Moreover, nanowires will be fabricated within the Al-Ga-In-Sb materials system. InSb is a semiconductor with an extraordinary small effective mass for electrons and with a very small band gap. In combination with AlGaSb, this materials system allows a huge variety of band alignments and, thus, is ideally suited for fundamental studies of quantum effects in nanostructures. The bottom-up approach, i.e. the growth of these nanostructures, gives control of the interfaces and surface passivation on the atomic level provided that the precise analysis of the surface and interface states is possible. To overcome the limitations of statistically distributed nucleation of nanowires on surfaces, various paths to control the nucleation by modifying the surface chemically and morphologically are investigated. This approach of self-assembly on structured templates offers exciting routes to create new artificial materials, like, e.g., regimented arrays of nanowires (Figure 5) or three-dimensional quantum dot crystals (Figure 8). Within these artificial crystals, the electronic states of neighboring dots will couple giving rise to a new bandstructure. The study of these artificial materials, in particular, their structural, electronic, photonic and magnetic properties will lead to new fundamental insights, which might also be valuable for information technology. The defined positioning of quantum dots and wires on templates is, moreover, a promising route to electrically address individual quantum structures in a controlled manner. The experimental studies on semiconductor nanostructures are accompanied by detailed theoretical analysis. Quantum confinement and many-body effects are explored using nanoelectronic systems relevant for applications. The central goal is the development of appropriate models, which can be implemented as simulation tools for the calculation of electronic transport properties up to the THz regime. The physical challenge is a quantum mechanical description of the Coulomb interaction and the thermodynamical nonequilibrium properties (e.g. due to applied voltages) on the same footing. For an adequate numerical simulation, we employ a combination of diagonalization techniques in Fock space and a nonequilibrium Green‘s function approach.