4.5 Biasing in MOS Amplifier Circuits • Biasing: establishing an

advertisement

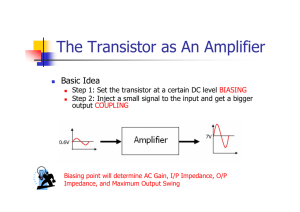

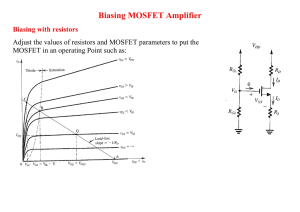

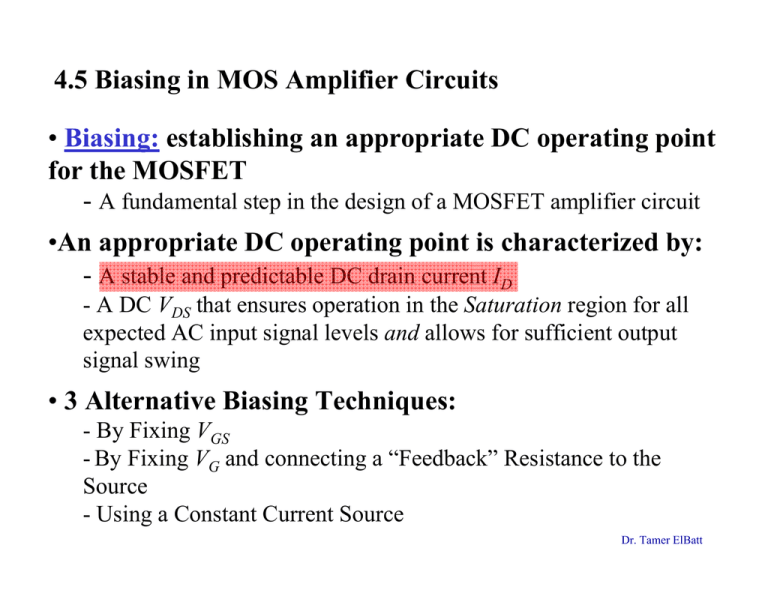

4.5 Biasing in MOS Amplifier Circuits • Biasing: establishing an appropriate DC operating point for the MOSFET - A fundamental step in the design of a MOSFET amplifier circuit •An appropriate DC operating point is characterized by: - A stable and predictable DC drain current ID - A DC VDS that ensures operation in the Saturation region for all expected AC input signal levels and allows for sufficient output signal swing • 3 Alternative Biasing Techniques: - By Fixing VGS - By Fixing VG and connecting a “Feedback” Resistance to the Source - Using a Constant Current Source Dr. Tamer ElBatt 1. Biasing by Fixing VGS Substantial Difference [ W 1 (VGS − Vt ) 2 • Simplest approach to get desired I D = µ nCox L 2 • But …. ] • NOT a good approach to bias MOSFET since Vt , Cox , W/L vary widely among devices of supposedly the same type Biasing by Fixing VGS is *OT a favorable approach Microelectronic Circuits - Fifth Edition Sedra/Smith Dr. Tamer ElBatt 2 2. Biasing by Fixing VG and Connecting a “Feedback” Resistance to the Source • How? - Fix the DC voltage VG and connect a resistance to the source as shown • Hence, VG = VGS + RS ID • Rs provides a negative feedback that stabilizes the value of the bias current ID - When ID increases, VGS has to decrease (to keep VG constant) which eventually decreases ID - When ID decreases, VGS has to increase (to keep VG constant) which eventually increases ID RS: degeneration resistance that provides negative feedback action to stabilize ID Dr. Tamer ElBatt Graphical Illustration Small Difference • The intersection of the straight line with the iD-vGS characteristics curve provides the coordinates (ID and VGS) of the bias point • Notice that the variability in ID, using this biasing approach, is much smaller Microelectronic Circuits - Fifth Edition Sedra/Smith Dr. Tamer ElBatt 4 Possible Practical Implementations • Utilizes one power supply VDD and derives VG through a voltage divider (RG1, RG2) • The coupling capacitor, CC1, in the figure below blocks DC and allows us to couple vsig to the amplifier input without disrupting the MOSFET DC bias point - CC1 should be large to have very low impedance (~SC) at freq. of interest Dr. Tamer ElBatt Possible Practical Implementations cont. • When 2 power supplies are available, a simpler bias arrangement can be utilized • RG establishes a DC ground at the gate and presents a high input resistance to a signal source that may be connected to the gate through a coupling capacitor Dr. Tamer ElBatt Example 4.9: Design the shown circuit to establish a DC current ID = 0.5 mA and a drop across RD and RS of 5V each. The MOSFET has Vt = 1 V and k’nW/L = 1 mA/V2. VDD = +15 V. Calculate the percentage change in the value of ID obtained when the MOSFET is replaced with another unit having the same k’nW/L but Vt = 1.5 V. Microelectronic Circuits - Fifth Edition Sedra/Smith Dr. Tamer ElBatt 7 3. Biasing Using a Constant-Current Source • The most effective scheme for biasing a MOSFET amplifier • RG establishes a DC ground at the gate and presents a high input resistance to a signal source that may be connected to the gate through a coupling capacitor • RD establishes an appropriate DC voltage at the drain to allow for the required output signal swing while ensuring saturation region operation Microelectronic Circuits - Fifth Edition Sedra/Smith Dr. Tamer ElBatt 8 3. Biasing Using a Constant-Current Source cont. • The shown circuit is one way to implement a constant current source • Q1 operates in the saturation region 1 ' W I D1 = k n (VGS − Vt ) 2 2 L • Since IG = 0, ID1 = IREF where the current through R is considered to be the reference current and is denoted IREF • *otice that Q2 has the same VGS as Q1 - Thus, if we assume that Q2 is in saturation, its drain current will be, I = I D2 1 W = k n' (VGS − Vt ) 2 2 L 2 I = I REF (W / L) 2 (W / L)1 The shown circuit is called “Current Mirror” Dr. Tamer ElBatt