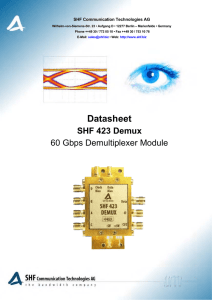

Datasheet - SHF Communication Technologies AG

advertisement

SHF Communication Technologies AG Wilhelm-von-Siemens-Str. 23D • 12277 Berlin • Germany Phone ++49 30 / 772 05 10 • Fax ++49 30 / 753 10 78 E-Mail: sales@shf.de • Web: http://www.shf.de Datasheet SHF 431B 55 Gbps D-type Flip Flop (DFF) Description The SHF 431B is a D-type flip-flop (DFF) module capable of broadband operation up to 55 Gbps. AC-coupled and 50 Ω terminated data and clock inputs ensure proper line termination and uncomplicated application. Optimum bias point for the data input can be set using the data bias connector. Features • • • • Broadband operation up to 55 Gbps Differential output, 250 mVpp single ended output swing Low power consumption single ended operation (data and clock input) Applications • • OC-768/STM-256 applications Broadband test and measurement equipment Option • Option bias adjust (BA): Module comes along with a wall power supply. One potentiometers to allow data bias to be adjusted without the need for additional power supplies. SHF reserves the right to change specifications and design without notice - SHF 431B DFF Revision 001 - 16/May/2008 Page 2/6 Specifications Parameter Symbol Unit Min Typ Max Minimum input data rate 1 Rin,min Gbps Maximum input data rate Rin,max Gbps 50 Din mVpp 300 1000 GHz 5 50 CLKin mVpp 500 1000 S11 dB 5 mV 250 Conditions Performance Data input voltage Clock input frequency Clock input voltage Input return loss Single ended output swing Rise/Fall time tr/tf RMS jitter Output return loss S22 Data/Clock bias adjust 5 500mVpp clock signal 55 500mVpp clock signal Eye Height Eye Amplitude, into 50 Ω load ps 9 20%/80% fs 400 600 dB 5 V -5 -2.5 0 -4.5 -5 -5.5 Operating conditions Power supply VEE V Supply current IEE mA 100 Power consumption Td mW 500 Operating temperature Top °C Dimensions 10 @ VEE = -5V 50 59x40x18 mm 1) The theoretical limit is DC, practical limit depends on slew rate of clock signal. Block Diagram V (1.85mm) female Data V (1.85mm) female Clock Y V (1.85mm) female Y V (1.85mm) female DFF Voltage Regulator VEE = -5V SHF reserves the right to change specifications and design without notice - SHF 431B DFF Revision 001 - 16/May/2008 Page 3/6 Sensitivity and Clock Phase Margin Measurements 31 The measurements below have been performed using a SHF 12100A BPG (PRBS 2 -1, Vamplitude = 400 mV), a SHF 11100A Error Analyzer and an Agilent 86100B DCA with Precision Time Base Module (86107A) and 70 GHz Sampling Head (86118A) to determine the eye height and jitter contribution of the input signal. In case of the sensitivity measurement the input signal has been reduced until a BER limit of 10-9 was achieved. For the CPM measurement the phase of the clock signal was varied until the BER reached the 10-9 limit. Typical Sensitivity Measurement 140 Eye Height [mV] 120 100 80 60 40 20 0 40 43 50 55 Bitrate [Gbps] Typical Clock Phase Margin Measurement Clock Phase Margin [deg] 300 250 200 150 100 50 0 40 43 50 55 Bitrate [Gbps] SHF reserves the right to change specifications and design without notice - SHF 431B DFF Revision 001 - 16/May/2008 Page 4/6 Output waveforms 31 The measurements below have been performed using a SHF 12100A BPG (PRBS 2 -1, Vamplitude = 400 mV) and an Agilent 86100B DCA with Precision Time Base Module (86107A) and 70 GHz Sampling Head (86118A). The output of the DFF module has been connected to the DCA input with a 0.5 m microwave cable assembly. Y @ 40 Gbps Y! @ 40 Gbps Y @ 43 Gbps Y! @ 43 Gbps Y @ 50 Gbps Y! @ 50 Gbps SHF reserves the right to change specifications and design without notice - SHF 431B DFF Revision 001 - 16/May/2008 Page 5/6 Y @ 55 Gbps Y! @ 55 Gbps Outline Drawing Data Bias 11.2 2 7.2 15.2 -5V GND 4x Ø 2. 7 11.3 Clock 7.2 28 9.05 34 38 Y 32 10 Y DFF 10 SHF 431 B Data 9.05 18 40 11.2 9.05 11.3 5 11.3 Port Connector Data V-Connector Clock V-Connector Y V-Connector Y V-Connector SHF reserves the right to change specifications and design without notice - SHF 431B DFF Revision 001 - 16/May/2008 Page 6/6