CMOS Static NAND Gate

advertisement

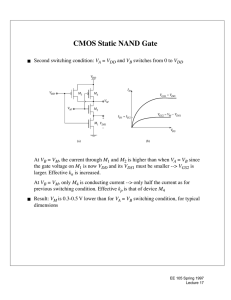

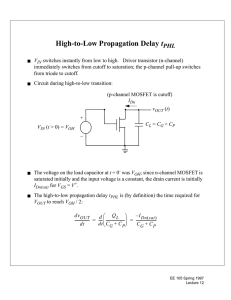

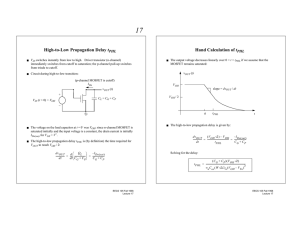

18 CMOS Static NAND Gate n Second switching condition: VA = VDD and VB switches from 0 to VDD VDD VDD M3 ID M4 VGS1 = VDD VM VM M2 + VGS2 = VM − VDS1 ID1 = ID2 M1 VDS1 _ VDS (a) (b) At VB = VM, the current through M1 and M2 is higher than when VA = VB since the gate voltage on M1 is now VDD and its VDS1 must be smaller --> VGS2 is larger. Effective kn is increased. At VB = VM, only M4 is conducting current --> only half the current as for previous switching condition. Effective kp is that of device M4 n Result: VM is 0.3-0.5 V lower than for VA = VB switching condition, for typical dimensions EECS 105 Fall 1998 Lecture 18 NAND Gate Transfer Functions n SPICE is useful to solve for the transfer functions under the various switching conditions (see Ex. 5.7). Note that the backgate effect means that the curves when VA switches and when VB switches are not identical. VOUT (V) Transfer Functions 5.0 4.0 B SWITCHES A SWITCHES A & B SWITCH 3.0 2.0 1.0 0.0 0.0 n 1.0 2.0 3.0 4.0 5.0 VIN (V) Results: setting kn = 2 kp results in VM approximately VDD/2. EECS 105 Fall 1998 Lecture 18 CMOS NAND Gate Transient Analysis n Worst-case situation for low-to-high transition: only one of the p-channel transistors is switching (say M4): kp 2 – I Dp = – I D4 = ----- ( V DD + V Tp ) 2 n n For high-to-low transition, consider M1 and M2 in series with effective length at 2Ln (worst-case since current is lowest with VA = VB) kn 2 2 I Dn = I D = I D2 = µ n C ox [ W n ⁄ 2 ( 2L n ) ] ( V DD – V Tn ) = ----- ( V DD – V Tn ) 1 4 For equal propagation delays, we require IDn = -IDp k k ----n- = ----p- --> kn = 2kp 4 2 The factor of 2 mobility difference between the p and n channels indicates that (W/L)n = (W/L)p (2 input NAND gate) n For an M-input NAND gate, we find that (W/L)n = (M/2) (W/L)p Note: NOR gates suffer from a factor of 2M between the n- and p-channel ratios which makes them unattractive for large fan-in gates EECS 105 Fall 1998 Lecture 18 Transistor Sizing (Example) VDD B A C D Y A D (W/L)0 B C GND Logic function Y= D+[A*(B+C)] EECS 105 Fall 1998 Lecture 18 CMOS Dynamic Logic n Static NOR gate VDD A M4 B M3 Q A M1 B M2 CL Idea: n-channel and p-channel devices separately perform the same logic function. replace p-channels with a resistor --> Q = A+B replace n-channels with a resistor --> Q = AB ... two functions are identical by DeMorgan’s Theorem n Let n-channels perform the logic and get rid of the pull-up devices (or vice versa) EECS 105 Fall 1998 Lecture 18 n-Channel CMOS Dynamic Logic clock signal φ(t) charges up load capacitance through MP (P = precharge) when it transitions from high to low; ME (E = evaluate) is cutoff and prevents any discharge path of CL through logic function transistors. n clock signal goes high --> MP is cutoff, ME conducts --> CL discharges if one of the logic transistors has a high input. n VDD φ φ A B MP C M CL + VOUT VDD − evaluate evaluate precharge 0 Logic Function φ ME (a) n t (b) Payoffs: 1. large fan-in NOR gates without huge p-channel load devices (also, avoids backgate effect on loads) 2. tends to be fast due to smaller load capacitances n Drawback: 1. clock is essential to refresh logic level stored on CL, which complicates the design EECS 105 Fall 1998 Lecture 18 n-Channel Dynamic Logic Propagation Delays n Consider “tPLH” to be the time required to pre-charge the output node Precharge Circuit (tPLH) φ=0 VDD MP VOUT (t = 0) = 0 V CL A B φ=0 n M ME (cutoff) Charging current kp 2 – I Dp = ----- ( V DD + V Tp ) 2 EECS 105 Fall 1998 Lecture 18 n-Channel Dynamic Logic Propagation Delays n Consider “tPHL” to be the worst-case time to evaluate the logical function after clock goes high. Evaluate Circuit (tPHL) (only one input high) φ=5V VDD MP (cutoff) VOUT (t = 0) = 0 V CL 5V 0V φ=5V n 0V ME Discharging current: assume (W/L)E = (W/L)A = ... (W/L)M and note that the transistors are in series -->effective value is kn / 2 kn 2 I D = µ n C ox ----- ( V DD – V Tn ) 4 n EECS 105 Fall 1998 Lecture 18 Boolean Functions in Dynamic Logic n Examples: VDD φ VDD φ MP ME Q A A B C D B C Q φ φ ME (a) n MP (b) (a) n-channel dynamic logic Q = ( A + B )C n (b) p-channel dynamic logic The output is “pre-discharged” to zero by MP and is only charged if there is a path through the logic transistors when the clock goes low and ME conducts. Q = AB + C + D EECS 105 Fall 1998 Lecture 18 CMOS Transmission Gates n Need: “gate” signals by having a series switch that can be shorted or opencircuited. C C IN OUT OUT IN C C (a) n (b) Why n-channel and p-channel in parallel? Only one device (say, n-channel): can’t pass an input voltage > VDD - VTn, since device will enter the cutoff region . G G 5V S D 5V B 0V (a) charge-up 5 V − VTn 0V D S 0V 0 V − VTp B 5V (b) discharge EECS 105 Fall 1998 Lecture 18 Pass Transistor Logic n Advantages: reduced transistor count and higher speed compared with static CMOS n Disadvantage: reduced noise margins B B A B B B OUT OUT A B (a) (b) Switching Network (c) EECS 105 Fall 1998 Lecture 18