High-to-Low Propagation Delay t

advertisement

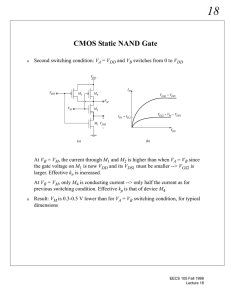

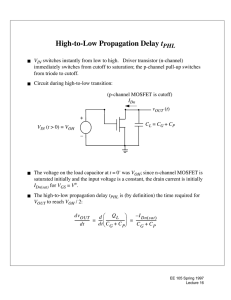

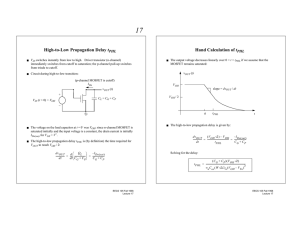

High-to-Low Propagation Delay tPHL ■ VIN switches instantly from low to high. Driver transistor (n-channel) immediately switches from cutoff to saturation; the p-channel pull-up switches from triode to cutoff. ■ Circuit during high-to-low transition: (p-channel MOSFET is cutoff) IDn vOUT (t) + CL = C G + CP VIN (t > 0) = VOH _ ■ ■ The voltage on the load capacitor at t = 0- was VOH; since n-channel MOSFET is saturated initially and the input voltage is a constant, the drain current is initially IDn(sat) for VGS = V+. The high-to-low propagation delay tPHL is (by definition) the time required for VOUT to reach VOH / 2: – I Dn ( sat ) dv OUT d QL ----------------- = ----- --------------------- = ----------------------dt C G + C P dt CG + C P EE 105 Spring 1997 Lecture 12 Hand Calculation of tPHL ■ The output voltage decreases linearly over 0 < t < tPHL if we assume that the MOSFET remains saturated: vOUT (t) VOH slope = dvOUT / dt VOH / 2 0 ■ tPHL t The high-to-low propagation delay is given by: dv OUT ( V OH ⁄ 2 ) – V OH – I Dn ( sat ) ----------------- = ----------------------------------------- = ----------------------dt t PHL CG + C P Solving for the delay: ( C G + C P ) ( V OH ⁄ 2 ) t PHL = ---------------------------------------------------------------------------2 µ n C ox ( W ⁄ 2L ) n ( V OH – V Tn ) EE 105 Spring 1997 Lecture 12 Graphical Interpretation ■ The n-channel driver remains saturated throughout the first half of the transition from high-to-low... ID VOUT t = 0+ VIN = VOH t = tPHL VOH t = 0− VIN = 0V VOH 2 0 0 VOH 2 VOH (a) VOUT 0 0 t tPHL (b) note that the characteristics above are not for a square-law MOSFET, which would enter the triode region for VOUT < VOH - VTn; the error is not large enough to matter for hand calculations in any case EE 105 Spring 1997 Lecture 12 Low-to-High Propagation Delay tPLH ■ For the low-to-high transition, the n-channel device is cutoff and the p-channel MOSFET is initially saturated and supplying - IDp(sat) to charge up the gate and parasitic capacitances. VDD VSGp + _ VIN = 0 V ■ - IDp Therefore, ( C G + C P ) ( V OH ⁄ 2 ) t PLH = ----------------------------------------------------------------------------2 µ p C ox ( W ⁄ 2L ) p ( V OH + V Tp ) In order to have identical propagation delays, the width-to-length ratio of the pchannel pull-up must be twice that of the n-channel driver, in order to compensate for the lower hole mobility in the channel. EE 105 Spring 1997 Lecture 12 Power Dissipation ■ Energy from power supply needed to charge up the capacitor: E charge = ■ ∫ + + + 2 V i(t)dt = V Q = ( V ) ( C G + C P ) Energy stored in the capacitor: + 2 1 E store = --- ( C G + C P ) ( V ) 2 ■ Energy lost in p-channel MOSFET during charging: + 2 1 E diss = E charge + E store = --- ( C G + C P ) ( V ) 2 During discharge, the n-channel MOSFET driver dissipates an identical amount of energy. If the charge/discharge cycle is repeated f times/second, where f is the clock frequency, the dynamic power dissipation is: + 2 P = ( 2E diss ) ⋅ f = ( C G + C P ) ( V ) f In practice, many gates don’t change state every clock cycle, which lowers the power dissipation ■ Additional source of dissipation: power flow from V+ to ground when both transistors are saturated. Can be significant, but hard to estimate by hand. Typical number: 25% of dynamic power dissipation. EE 105 Spring 1997 Lecture 12 Power (cont.) ■ Practical numbers: CL = 50 fF, f = 200 MHz, V+ = 3 V, Ngates = 5 x 105 P = 45 W ! (note that the real average depends on the average number switching per clock cycle) Comparing Technologies -- the power-delay product * Logic families are often compared by considering the product of the dynamic power dissipation and the propagation delay: + + 2 ( C L + C p ) ( V ⁄ 2 ) PDP = Pt P ≅ ( C L + C p ) ( V ) f --------------------------------------------- 1--- k ( V + – V ) 2 Tn 2 N where V+ has been substituted for VOH to achieve a more universal result. * For V+ >> VTn, 2 + (CL + C p) V f PDP ≅ --------------------------------------kN EE 105 Spring 1997 Lecture 12 CMOS Static Logic Gates ■ “Static” -- logic levels remain valid so long as power is supplied ■ NOR and NAND gates VDD M4 A M3 B + M2 VOUT _ M1 B A (a) VDD M3 A M4 A B + B M2 VOUT _ M1 (b) EE 105 Spring 1997 Lecture 12 CMOS NAND Gate ■ Qualitative description Find transfer curve for case where VA = VB and both transition from 0 to 5 V ■ Transistors M1 and M2 are in series and have the same current; however, they do not have the same gate-source bias VDD VM M3 M4 ID VM VM VGS1 = VM M2 + M1 VDS1 VGS2 = VM − VDS1 ID1 = ID2 − VDS (a) (b) EE 105 Spring 1997 Lecture 12 MOSFETs in Series ■ Transistors M1 and M2 are “in series” with the same gate voltage, for the case where the inputs are tied together (A = B) VOUT M1 VA = VB M2 ground drain current is the same through each device ... what is the effective value of kP? EE 105 Spring 1997 Lecture 12 MOSFETs in Series (Cont.) ■ At VA = VB = VM, the cross section through M1 - M2 is: ,, ,, VM ,, ,, source VM gate gate M1 M2 n+ L1 L2 (a) ,, ,, drain VM ,, source VM gate gate M1 M2 L1 L2 ,, drain (b) ■ Transistor M1 is in triode and M2 is saturated. From the cross section, the drain of M1/ source of M2 can be eliminated without affecting anything --> the two MOSFETs can be merged into a composite transistor with L1 + L2 = 2 Ln ■ Solving for VM for the case where VA = VB (note that the two p-channel devices are in parallel and have an effective width of W3 + W4 = 2 Wp 2k p kp V Tn + 2 ----- ( V DD + V Tp ) V Tn + ------------ ( V DD + V Tp ) kn ⁄ 2 kn V M = ------------------------------------------------------------------ = --------------------------------------------------------------2k p kp 1 + -----------1 + 2 ----kn ⁄ 2 kn where kn = µnCox (Wn/Ln) and kp = µpCox (Wp/Lp) We could optimize VM = VDD/2, but there is another switching condition to consider EE 105 Spring 1997 Lecture 12 CMOS Static NAND Gate ■ Second switching condition: VA = VDD and VB switches from 0 to VDD VDD VDD M3 ID M4 VGS1 = VDD VM VM M2 + VGS2 = VM − VDS1 ID1 = ID2 M1 VDS1 _ VDS (a) (b) At VB = VM, the current through M1 and M2 is higher than when VA = VB since the gate voltage on M1 is now VDD and its VDS1 must be smaller --> VGS2 is larger. Effective kn is increased. At VB = VM, only M4 is conducting current --> only half the current as for previous switching condition. Effective kp is that of device M4 ■ Result: VM is 0.3-0.5 V lower than for VA = VB switching condition, for typical dimensions EE 105 Spring 1997 Lecture 12 NAND Gate Transfer Functions ■ SPICE is useful to solve for the transfer functions under the various switching conditions (see Ex. 5.7). Note that the backgate effect means that the curves when VA switches and when VB switches are not identical. VOUT (V) Transfer Functions 5.0 4.0 B SWITCHES A SWITCHES A & B SWITCH 3.0 2.0 1.0 0.0 0.0 ■ 1.0 2.0 3.0 4.0 5.0 VIN (V) Results: setting kn = 2 kp results in VM approximately VDD/2. EE 105 Spring 1997 Lecture 12 CMOS NAND Gate Transient Analysis ■ Worst-case situation for low-to-high transition: only one of the p-channel transistors is switching (say M4): kp 2 – I Dp = – I D4 = ----- ( V DD + V Tp ) 2 ■ ■ For high-to-low transition, consider M1 and M2 in series with effective length at 2Ln (worst-case since current is lowest with VA = VB) kn 2 2 I Dn = I D = I D2 = µ n C ox [ W n ⁄ 2 ( 2L n ) ] ( V DD – V Tn ) = ----- ( V DD – V Tn ) 1 4 For equal propagation delays, we require IDn = -IDp kn kp ----- = ----- --> kn = 2kp 4 2 The factor of 2 mobility difference between the p and n channels indicates that (W/L)n = (W/L)p (2 input NAND gate) ■ For an M-input NAND gate, we find that (W/L)n = (M/2) (W/L)p Note: NOR gates suffer from a factor of 2M between the n- and p-channel ratios which makes them unattractive for large fan-in gates EE 105 Spring 1997 Lecture 12 EE 105 Spring 1997 Lecture 12

![6.012 Microelectronic Devices and Circuits [ ]](http://s2.studylib.net/store/data/013591838_1-336ca0e62c7ed423de1069d825a1e4e1-300x300.png)