Solution - University of California, Berkeley

advertisement

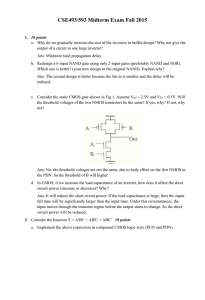

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on October 20, 2006 by Karl Skucha (kskucha@eecs.berkeley.edu) Borivoje Nikolic Homework #6 EECS 141 Problem 1 – CMOS Analysis 1A Implement the logic function X =((A’+B’)(C’+D’+E’)+F’)G’ using complementary CMOS. Size the devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 4 and PMOS W/L = 8. i = Lmin = 0.25um. Methodology: Given an inverter with NMOS size 4 (resistance Rnu/4) and PMOS size 8 (resistance Rpu/8), we need to size the network such as the worst case resistance is equivalent to the above resistances. The Rnu and Rpu are Req’s of a NMOS and PMOS of W/L = 1, respectively. Considering the NMOS network, we see that worst case occurs when either G, FAB, or FCDE are 1. Hence all these paths need to have a Req = Rnu/4. Size of G is trivial; it is 4. Now lets size FCDE. Since this is 4 transistors in series, lets make them all the same size and get the equation 4*Rnu/s = Rnu/4. This leads s = 16, hence the size of all of these is 16. Now lets consider FAB. Since we already sized F, we need to now size A and B such that Req =Rnu/4. Our equation is Rnu/16 + 2Rnu/s = Rnu/4. We find that s is equal to 32/3. Pull-down (W/L) : n Sizeof( A, B ) = 16 Sizeof (C, D, E ) = 24 Sizeof( F ) = 8 Sizeof( G ) = 4 Pull-up (W/L) : or or or or 32/3 16 16 4 p Sizeof( G ) = 16 or 24 Sizeof( F ) = 16 or 12 Sizeof( A, B, C, D, E ) = 32 or 24 We see that the alternate solutions are better since the total size of the transistors is smaller, and hence smaller overall logical effort. 1B Which input pattern(s) would give the worst and best equivalent HL or LH delay Using the sizing from part a, find combination of inputs that would maximize (worst) or minimize (best) resistance. For worst case analysis, for pull-down, want to charge up as many internal capacitances as possible; for pull-up, we want to discharge as many internal capacitances as possible. Pull-down Best G, F, A, B, C, D, E: 0 → 1 Worst B, E: 0; F, A, C, D: 1; G: 0 → 1 With B, E, and G equal to zero the pull down path will be off and the pull-up network will charge up all internal capacitances because F, A, C, and D are on in the pull-down network. Once G transitions, all the charge stored on the output and internal nodes will have to discharge through one transistors. Pull-up G, F, A, B, C, D, E: 1 → 0 B, E: 0; F, A, C, D: 1; G: 1 → Similar reasoning here; with in the pull-down network on, discharges all internal nodes zero; once G switches, the pull-up network must charge up all internal nodes both in the pull-up networks, and pulldown networks. There could be a lot of variations on the interpretation of “worse case,” but since we have sized all transistors for equal resistance, we are left with finding the worst case capacitance. 1C Verify part b with SPICE (using g25.mod). * hw6 prob 1c .lib '/home/ff/ee141/MODELS/g25.mod' TT .param low=0 .param high=2.5 VDD dd 0 high VA A 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low 6.2n low 6.3n high VB B 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low VC C 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low 6.2n low 6.3n high VD D 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low 6.2n low 6.3n high VE E 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low VF F 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low 6.2n low 6.3n high VG G 0 PWL 0 low 2n low 2.1n high 4.1n high 4.2n low 8.2n low 8.3n high 12.3n high 12.4n low M0 11 G dd dd pmos L=250E-9 W=6E-6 M4 8 B 11 dd pmos L=250E-9 W=6E-6 M5 8 A 11 dd pmos L=250E-9 W=6E-6 M6 15 F dd dd pmos L=250E-9 W=3E-6 M1 15 E 8 dd pmos L=250E-9 W=6E-6 M2 15 D 8 dd pmos L=250E-9 W=6E-6 M3 15 C 8 dd pmos L=250E-9 W=6E-6 M7 14 E 0 0 nmos L=250E-9 W=4E-6 M8 3 D 14 0 nmos L=250E-9 W=4E-6 M9 9 B 0 0 nmos L=250E-9 W=2.66E-6 M10 10 C 3 0 nmos L=250E-9 W=4E-6 M11 10 A 9 0 nmos L=250E-9 W=2.66E-6 M12 15 G 0 0 nmos L=250E-9 W=1E-6 M13 15 F 10 0 nmos L=250E-9 W=4E-6 .options nomod post=2 .tran 100p 15n .END Pull-down Pull-up Best: 100ps 62.2ps Pull-down Pull-up Best Worst: 323ps 473ps Note the lack of symmetry; our sizing above for symmetry in the worst case doesn’t account for the fact that in the worst case, we’re charging/discharging internal node capacitance. 1D Suppose all NMOS devices are (W/L)n and PMOS devices are (W/L)p. Does your implementation of X yield the lowest output capacitance. If so, why; if not, rearrange your implementation so it has the lowest output capacitance. Explain. Depending on how your schematic looks you might have to rearrange it. The goal is to have the minimum number of transistors, from either the pull-up or pull-down networks, attached to the output node X. This minimizes the number of drain capacitances. In the schematic above, move G in the pull-up network from the top of the series connection, to the output, reducing the number of transistors attached to X from 6 to 3. Our minimum output capacitance is hence the drain capacitance of 3 transistors. Problem 2 – Another CMOS 2A What is the logic function of circuits A and B in the figure below? Both logic functions implement the XNOR: Circuit A is the dual network; circuit B is not a dual network. Circuit B is a valid static gate because the pull-up input combinations AA’ and BB’ are never active (i.e. deleting the connection in the pull-up network does not break the gate’s functionality). One advantage of Circuit B is that it doesn’t have a common node to all devices in the PMOS; such a node has more capacitance. This may result in slightly lower pull-up delay. 2B Sketch the layout (using stick diagrams) of both gates in minimum area (i.e. fewest diffusion breaks). Compare/contrast the two circuit sketches; Show work for Euler paths. Both gates can be implemented in layout with zero diffusion breaks. The Euler path for Circuit A is BA’AB’; Circuit B’s Euler path is BA’B’A (note you have to swap the inputs on the right branch of the pull-down network; otherwise you’d need a diffusion break. Problem 3 – VTC and Propagation Delay Comparison of Odd Inverters A “Psuedo NMOS” inverter implementation is shown in Figure A, in which the load is a PMOS transistor with a fixed VGS. Figure B shows a saturated inverter used in NMOS technology. 3A Find VOH, VOL, and VM for the two inverters using the unified model. Fig. A Fig. B Vdd=2.5V W/L=1u/0.5u 0.5u/0.5u Vout Vin W/L=1.5u/0.5u 2u/0.5u Use the following parameters: NMOS: VT0=0.5V, kp=18uA/V2, γ=0.5V1/2, λ=0.06V-1 2ΦF = -0.6V PMOS: VT0=0.5V, kp=5uA/V2, γ=0.5V1/2, λ=0.1V-1 2ΦF = 0.6V 3B Find the propagation delay assuming a 100fF capacitance attached to the output. Ignore other capacitances. 3C List the advantages and disadvantages of using inverters in Fig A and Fig B as opposed to a CMOS inverter. Consider all effects we have learned so far. • Delay o Overall delay is higher than CMOS of similar size. o Huge mismatch in high to low versus low to high, especially in inverter B. • Swing o Inverter A does not go to ground. o Inverter B has terrible swing; from .37V to 1.76V is very bad. The 1.76V VOH is especially bad since it will keep a CMOS inverter (if attached to the output) consuming static power (since its PMOS will be on). • Noise Margins o Noise Margins are reduced, especially in inverter B. • Power o Inverter A consumes static power at Vout=VOL o Inverter B consumes static power at Vout=VOL • Input Capacitance o Compared to the CMOS inverter, these have a lower input capacitance for similar sizing (since only one connection for Vin). This is probably the only advantage. Problem 4 – Wire Trivia What happens to the RC delay of a metal wire over a silicon layer if the following situations occur. Explain your answer, especially if you choose (e). I. Wire width is doubled: (a) Increases by a factor of 2 (b) Decreases by a factor of 2 (c) Decreases by a factor of 4 (d) Remains unchanged (e) None of the above. E Explanation: If wire width doubles, resistance goes down by a factor of 2 while capacitance goes up by a factor less than 2. This is because the fringe capacitance less than doubles, and hence the total capacitance does not double as well. Delay is reduced by a factor between 1 and 2. II. Wire length is halved: (a) Increases by a factor of 2 (b) Decreases by a factor of 2 (c) Decreases by a factor of 4 (d) Remains unchanged (e) None of the above C Explanation: Resistance halves and capacitance halves, so delay reduces by 4. III. Wire height is doubled: (a) Increases by a factor of 2 (b) Decreases by a factor of 2 (c) Decreases by a factor of 4 (d) Remains unchanged (e) None of the above. E Explanation: Resistance is halved but the capacitance less than doubles. It increases a bit because the fringe capacitance goes up. Our delay is reduced by a factor between 1 and 2. IV. The oxide thickness between the metal wire and the substrate is doubled: (a) Increases by a factor of 2 (b) Decreases by a factor of 2 (c) Decreases by a factor of 4 (d) Remains unchanged (e) None of the above E Explanation: The resistance is unchanged while the total capacitance decreases by a factor less than 2 because the parallel plate capacitance is halved while the fringe capacitance does not change much. Our delay is reduced by a factor between 1 and 2. V. Another wire is placed next to the original wire and is grounded. (a) Increases (b) Decreases (c) Remains unchanged (d) None of the above ☺ A Explanation: If we place another wire close to the original wire, we gain a coupling capacitance (between the wires) while we lose one factor of fringe capacitance. Since the wire is close, the coupling capacitance dominates and our total capacitance hence goes up. Our delay increases. VI. Another wire is placed next to the original wire and is driven by the same gate as the original wire. (a) Increases (b) Decreases (c) Remains unchanged (d) This is impossible! B Explanation: Since the 2 wires remain at the same voltage, we have no coupling capacitance and we effectively lose one factor of fringe capacitance from the total capacitance. Therefore, our delay decreases.