VLalamDefense_STC_SOPC.ppt

advertisement

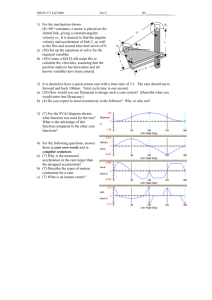

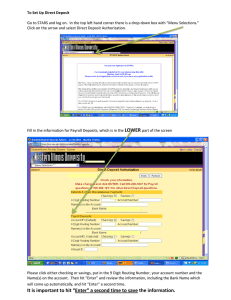

System-On-a-Programmable-Chip (SOPC) Implementation of the Silicon Track Card (STC) Thesis Defense By Arvindh-kumar Lalam Department of Electrical and Computer Engineering Florida A&M University – Florida State University College of Engineering Outline DZERO Experiment Silicon Track Card (STC) SOPC Implementation and Validation Content Addressable Memory (CAM) Hit-Filter Implementation using a CAM Results and Conclusions FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Proton Anti-proton Collision Study the properties of known particles Eg. ‘top’ quark Look for the unknown FAMU-FSU College of Engineering Department of Electrical and Computer Engineering DZERO (D0) Experiment The DZERO Experiment is conducted in Tevatron Collider, at Fermi National Acceleration Laboratory proton & anti-proton are made to collide at high velocities in the TeVatron collider The beams cross every 132 ns The TeVatron Collider FAMU-FSU College of Engineering Department of Electrical and Computer Engineering D0 Detector Silicon Tracker Fiber Tracker Silicon Tracker (SMT) Contains Silicon charge collectors - “strips” Fiber Tracker (CFT) Identifies trajectory information - “tracks” FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Particle tracks Cross-section of Fiber Tracker (CFT) FAMU-FSU College of Engineering Department of Electrical and Computer Engineering D0 Trigger Trigger Detector Level 1 CAL FPS/ CPS L1 CAL L1 CFT Level2 L2 Cal L2 Ps CFT L2 CFT SMT L2 STT Muon FPD L1 Muon L2 Global Level 3 L1CFT SMT preprocess SMT data find clusters L2 Muon L1 FPD associate clusters with L1CTT tracks fit trajectories L1 Framework L2CFT FAMU-FSU College of Engineering Department of Electrical and Computer Engineering L3 The Level_2 STT L1CFT FRC SMT STC preprocess SMT data find clusters centroids (roads) associate clusters with L1CTT tracks (finds hits) fit trajectories TFC L2CFT FAMU-FSU College of Engineering Department of Electrical and Computer Engineering L3 D0 Trigger - STC CFT H Layer 2 mm road CFT A Layer hits “road” : Track information translated for the STC “clusters” : Groups of strips “centroid”: Centroid of a cluster centroids SMT Layers “Si” strips “hit” : A centroid that falls in a road FAMU-FSU College of Engineering Department of Electrical and Computer Engineering STC - Functionality Reformats received “strip” data Finds “Clusters” and their “centroids” Identifies “hits” Stores intermediate data for debugging Implements a contention scheme Several STCs function simultaneously Operates at PCI 33 MHz FAMU-FSU College of Engineering Department of Electrical and Computer Engineering STC - Main Data Path Control Lines Main Control Control Logic Data Lines Control Lines SMT Data Strip Reader Downloaded Parameters Centroid Finder Handshake Signals Roads from FRC Hit Filter L3 Buffers To L3 FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hits Control Logic and Channels Control and Feedback Signals .... 7... 10 To rest of L2STT Channel 0 (STC0) Channel 1 (STC1) . . . . . . Channel 7 (STC7) Control Logic SMT Data (strip information) Control Logic designed at BU acts as an interface Each Control Logic controls 8 Channels (STCs) STC receives SMT data directly from SMT “commom data bus” is used to download hits FAMU-FSU College of Engineering Department of Electrical and Computer Engineering System-On-a-Programmable-Chip (SOPC) Discrete PCB components? SOPC Altera APEX II EP2A90 7M gates: 1.5Mbits SRAM Xylinx Virtex E XC2V10000 10M gates: 3.4 Mbits SRAM Altera APEX 20KE EP20K600EBC652-1X Accommodates 1 STC FAMU-FSU College of Engineering Department of Electrical and Computer Engineering SOPC - Advantages The circuit can be fit into a single device Occupies smaller area on the board Board-design interconnects are less complex Internal propagation delays are predictable FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Computer Aided Design Tools Entry and Functional Simulations: Quartus II, Active HDL 4.2 Entry in VHDL/Schematics Synthesis: Quartus II, Synopsys FPGA Express Simulation and Configuration: Quartus II FAMU-FSU College of Engineering Department of Electrical and Computer Engineering SOPC Implementation of STC Prototype Testing Board Control Logic BU Silicon Track Card FAMU-FSU COE Used Test memory space to store test vectors of SMT data FAMU-FSU College of Engineering Department of Electrical and Computer Engineering SOPC Implementation - Hit download FAMU-FSU College of Engineering Department of Electrical and Computer Engineering SOPC Implementation - Result Channel Hits STC0 7 STC1 2 Trailers 1 1 Hit-words 8 2 Contention is successfully resolved FAMU-FSU College of Engineering Department of Electrical and Computer Engineering STC - Resources Device Family FLEX (CPLD) Memory bits Pins EPF10K100EB 4,340 (83%) C356-1 10,532 (21%) 257 (94%) EPF10K200EG 2,941 (29%) C599-1 79,424 (80%) 466 (99%) EFF10K200SF C484-1 10,692 (10%) 292 (79%) Chip Total APEX (SOPC) Logic Elements 1,860 (18%) 10,361 96,612 829 EP20K600EBC 6,744 (27%) 105,828 (33%) 262 (53%) 652-1X FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Content Addressable Memory(CAM) A memory like RAM and FIFO Takes data as input and provides the location Output can be “encoded” or “unencoded” A “found” signal is used to signal presence of data 1 - 0 - 0 - 1 001 - 010 - 011 - 100 Data 3 Address Data 00 01 10 11 100 111 001 000 Found 1 10 - X - X - 00 Encoded Address 2 4 x 3 CAM with Encoded Output FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Don’t cares Don’t-cares can be used to represent multiple digital words A don’t-care (d) represents both ‘1’ and ‘0’ CAMs that accommodate don’t-cares are called Ternary CAMs Eg: APEX CAM Data represented in the CAM Address (binary) decimal 00 1 0001 0001 01 2, 3 0010 0011 001d 10 4, 5, 6, 7 01dd 11 0, 4, 8, 12 0100 0101 0110 0111 0000 0100 1000 1100 binary FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Equivalent Word dd00 APEX CAM Memory blocks of Altera’s APEX chip can be used as a Ternary CAM The data can be stored in two ways During power-up (using an .mif file) During run-time 1 - 0 - 1 1100 - 1001 - 0100 Data 4 Address Data 00 01 10 11 0001 001d 01dd dd00 Found 1 11 - X - 10, 11 Encoded Address 2 FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Previous Hit Filter Receives roads and centroids Internally stores roads Uses ‘hit-match’ modules to find if a centroid falls in the roads When a centroid falls in a road, it is a hit Each ‘hit-match’ generates a bit ‘1’ for hit lower - address centroid upper - address Road Word 21…11 Upper Address 10 ... 0 Lower Address FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Previous Hit Filter – Block Diagram road word road select 22 6 centroid Comparator Module 11 46 “hit-match” modules in parallel comparator word Hit- hit Format 46 (Encoder) 32 Contains 46 ‘hit-match’ modules Each of the centroids is checked in all roads The locations of ‘1’s are encoded to generate a hit-word Hit-format, designed in VHDL, uses Finite State Machine Hit-format module sequentially searches for hits. FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit Filter – CAM-only model Uses memory blocks instead of a combinational circuit (comparator) Set of all the words existing between the road boundaries is called a “road-set” Each road-set can be minimized to 12 words by using don’t cares “road-sets” of each road are stored in the memory FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Minimized Road-Set Actual road-set Minimized road-set 1 0000001 0000001 2 0000010 0000011 0000100 0000111 000001d 3 1000 0000001 4 0001000 0001111 0001ddd 5 0010000 0011111 001dddd 6 0100000 0111111 01ddddd 7 1000000 1011111 10ddddd 8 1100000 1101111 110dddd 9 1110000 1110111 1110ddd 10 1111000 1111011 11110dd . . 00001dd 1000 1111110 11 12 1111100 1111101 1111111 FAMU-FSU College of Engineering Department of Electrical and Computer Engineering 111110d 1111110 CAM-only model – Implementation Road-set word road 22 Road-set Generator found 11 Control signals CAM location 10 centroid 11 FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit create hit 32 CAM-only Model - Functionality Storing roads The road-set is minimized by using the “don’t cares” The minimized road-set is stored in an APEX CAM The CAM needs 50 clock cycles to store each road-set Checking for hits Each of the centroids is given as input to the CAM If the centroid is found in the road-set, CAM returns all the encoded locations. CAM takes only two clock cycles to find the location of first hit FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit Filter – With New Encoder Uses previous comparator block and a new “hit-word generator” block The locations of ‘1’s in the comparator word are encoded using a CAM FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit Filter – Implementation road word road select 22 6 centroid Comparator Module 11 46 “hit-match” modules in parallel comparator word Hit-Word hit Generator 46 (Encoder) FAMU-FSU College of Engineering Department of Electrical and Computer Engineering 32 CAM as Encoder 1 0001 - 0000 - 1001 Data 4 x 4 Encoder Map 4 Address Data 00 01 10 11 ddddddddd111 dddddd111ddd ddd111dddddd 111ddddddddd 0 - 1 Found 1 00 - X- 00, 11 Encoded Address 2 3 2 1 0 0 d d d 1 1 d d 1 d 2 d 1 d d 3 1 d d d FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit Filter Encoder Map 45 44 43 ................................33 32 31 30 29 28 26...............................3 2 1 0 d d d d d 1 1 d d 1 d d . . d d d d d d . . . . . . . . . . . . d d d d d d d d d d d d d d d d d d d d d d d d . d . . . . . . . . . d d d d d d . . . . . . . . . . . . . . . . . . . . . d d . . d d . . . . . d d . . . . . . . . . . . . . . . . 31 x 31 CAM 30...0 30 - - - 0 3 . . . d d d . d . . d . d d . . . . d . . . . . . . . . . . . d d . . . . . d d d d d d . . . . . . d d d d d . . . . . d d d d d d . . . . . . d d d d d d . . . . . d d d d d 1 d d . . d d d d d 1 d d d . . d d d d d d d d d d d d . d . . . . . . . 14 - - - 0 d . . . . . . d d d d d d d 1 d d d d . . d d d d d . d d 1 d d d d d . . d d d d d d d d d . . d d d d d d d d . . d d d d d d d d . . . . . d 1 d d d . d . d . . . . . . . . . . . 1 . d . d . d d . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . d . d . . . d 1 14 - - - 0 32 30 29 d d 31 28 26 25....................... 4 d . d . d . 43 ................................ 33 15 x 15 Encoder Map d d d 44 31 x 31 Encoder Map d d d 45 46 x 46 Encoder Map 2 1 0 30 - - - 0 . 15 x 15 CAM . 14...0 . 1 . . . . . . . . . . d . d . d . . . . . . . . . d d d . d d . . d d d d d 1 d . . . . . d d d d d d d d . . d d d d d d d . . . . . d d d d d d d d . . d d d d d FAMU-FSU College of Engineering Department of Electrical and Computer Engineering . Hit-Word Generator HIT Control Signals 32 HIT GENERATOR CAM 31x31 6 CAM 15x15 31 15 5 Comparator Word 46 FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit Filter Results Number of clock cycles required for storing road information 6 roads (consecutive) 6 roads (distributed) 46 roads Sequential search (contains comparator) 6 46 46 CAM only 270 * 310 * 2070* 6 46 46 With CAM block in hitword generator (contains comparator) * This depends on the upper and lower words of the road. The quoted figures correspond to the worst possible case. FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Hit Filter Results Number of clock cycles required for finding hits 6 roads (consecutive) 6 roads (distributed) 46 roads Sequential search (contains comparator) 32 150 232 CAM only 10 10 50 10 10 50 With CAM block in hitword generator (contains comparator) FAMU-FSU College of Engineering Department of Electrical and Computer Engineering STC Results Event 1 : SMT data for a simple event Event 2 : SMT data for a complex event STC 6 consecutive roads Event1 Event2 15.0s 46 roads Event1 16.48s 6 distributed roads Event2 Event1 76.03s 11.636s Event2 Previous 4.878s Upgraded 4.03s 6.909s 5.242s 19.06s 4.03s 6.909s % decrease in time taken 17% 54% 68% 75% 65% 87% FAMU-FSU College of Engineering Department of Electrical and Computer Engineering 51.78s Conclusions SOPC implementation was successfully verified The upgraded STC shows an improvement of upto 87% FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Future Work The number of roads Hit-Filter can accommodate can be increased FAMU-FSU College of Engineering Department of Electrical and Computer Engineering Acknowledgements National Science Foundation and the US Department of Energy. Boston University Florida State University – Physics Faculty: Adams, Prosper, Wahl Postdocs: Tentindo-Repond Florida A&M University – Florida State University COE Faculty: Heintz, Narain, Popkov Engineers: Earle, Hazen Students: Kevin, Zabi Faculty: Perry Students: Lolage, Meyers, Roper, Saunders Altera, Aldec, Synopsys FAMU-FSU College of Engineering Department of Electrical and Computer Engineering