Computer Architecture - For Section T1 & T2

advertisement

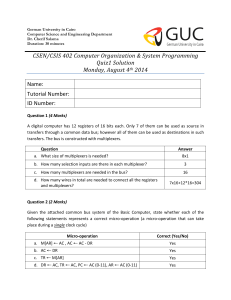

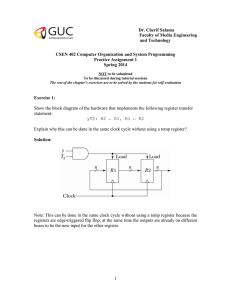

Paper Code: ETCS-305 Subject: Computer Architecture ASSIGNMENT I 1) Draw the block diagram for the hardware implementation of the following statement. x+yz: AR ← AR + BR where AR & BR are two n-bit registers and x, y & z are control variables. Include logic gate for control function. 2) Starting from an initial value of R= 11011101, determine the sequence of binary values in R after a logic shift-left, followed by a circular shift-right, followed by a logical shift-right and a circular shift-left. 3) What is wrong with the following statements? a) xT: AR ← AR, AR ← 0 b) yT: R1 ← R2, R1 ← R3 c) zT: PC ← AR, PC ← PC + 1 4) A digital computer with a common bus system for 16 registers of 32 bits each. The bus is constructed with multiplexers. a) How many selection inputs are there in each multiplexer? b) What size of multiplexer is needed? c) How many multiplexers are there in the bus? 5) The following transfer statements specify a memory. Explain the memory operation in each case. a) R2 ← M[AR] b) M[AR] ← R3 c) R5 ← M[R5] 6) Starting from an initial value of R=11011101, determine the sequence of binary values in R after a logical shift left, followed a circular shift right, followed by arithmetic shift left, followed by a logical shift right, followed by a circular shift left, followed by an arithmetic shift left. Note: Last date of submission of assignment is 30th August, 2013 by 0815 hours