Practice Assignment 1 Solution - Faculty of Media Engineering and

advertisement

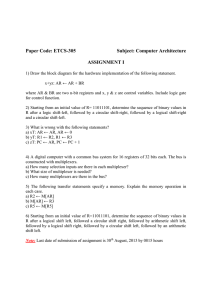

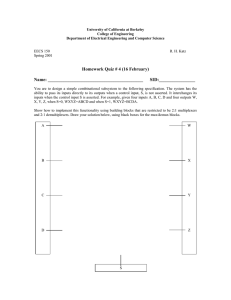

Dr. Cherif Salama Faculty of Media Engineering and Technology CSEN 402 Computer Organization and System Programming Practice Assignment 1 Spring 2014 NOT to be submitted To be discussed during tutorial sessions The rest of the chapter’s exercises are to be solved by the students for self-evaluation Exercise 1: Show the block diagram of the hardware that implements the following register transfer statement: yT2: R2 ← R1, R1 ← R2 Explain why this can be done in the same clock cycle without using a temp register? Solution: Note: This can be done in the same clock cycle without using a temp register because the registers are edge-triggered flip flop; at the same time the outputs are already on different buses to be the new input for the other register. 1 Exercise 2: The outputs of four registers R0, R1, R2 and R3, are connected through 4-to-1-line multiplexers to the inputs of a fifth register R5, each register is 8 bits long. The required transfers are dictated by four timing variables T0 through T3 as follows: T0: T1: T2: T3: R5←R0 R5←R1 R5←R2 R5←R3 The timing variables are mutually exclusive, which means that only one variable is equal to 1 at any given time, while the other three are equal to 0. Draw a block diagram showing the hardware implementation of the register transfers. Include the connections necessary from the four timing variables to the selection inputs of the multiplexers and to the load input of register R5. Solution: The truth table for the outputs: T0 0 1 0 0 0 T1 0 0 1 0 0 T2 0 0 0 1 0 T3 0 0 0 0 1 S1 x 0 0 1 1 S0 x 0 1 0 1 Load 0 1 1 1 1 Use the “sum of product” technique to get the logic expressions for the selection lines and the load signal: S1 = T2 + T3 S0 = T1 + T3 Load = T0 + T1 + T2 + T3 2 Exercise 3: A digital computer has a common bus system for 16 registers of 32 bits each. The bus is constructed with multiplexers. a. b. c. How many selection inputs are there in each multiplexer? What size of multiplexers is needed? How many multiplexers are the in the bus? Solution: a. 4 selection lines to select one of 16 registers. b. 16 × 1 multiplexers. c. 32 multiplexers, one for each bit of the registers. Exercise 4: Draw the block diagram for the hardware that implements the following statements: x + yz: AR ← AR + BR where AR and BR are two n-bit registers and x, y, and z are control variables. 3 Solution: 4