Verilog HDL Pertemuan 9 Matakuliah H0362/Very Large Scale Integrated Circuits

advertisement

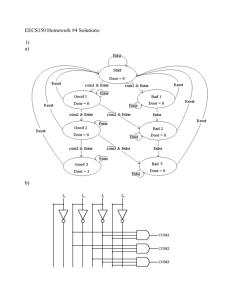

Matakuliah Tahun Versi : H0362/Very Large Scale Integrated Circuits : 2005 : versi/01 Pertemuan 9 Verilog HDL 1 Learning Outcomes Pada Akhir pertemuan ini, diharapkan mahasiswa akan dapat merumuskan statemen dalam bahasa pemrograman Verilog atas suatu rangkaian gerbang logik sederhana. 2 Basic Concepts A hardware description language (HDL) allows us to specify the components that make up A digital system using words and symbols instead of having to use a pictorial representation like a block or logic diagram. 3 Basic Concepts Architectural features Timing & Dataflow Behavioral Verification Data storage & movement State machine specification RTL Verification Synthesis Example of a VLSI design flow Verification Logic design Breakdown into netlist of gates Use netlist to create logic network Simulation Circuits Simulation Physical Design Cell-based design Custom if needed Layout of mask Final check Tape Out To manufacturing 4 Structural Gate Level Modeling Rangkaian digital: a b c d G1 W1 G3 G2 f W2 Persamaan logik: f = NOT(a . b + c . d) Verilog HDL: module AOI4 (f, a, b, c, d) ; input a, b, c, d ; output f ; wire w1, w2 ; and G1 (W1, a, b) and G2 (f, W1, c, d) nor G3 (f, W1, W2) endmodule 5 Structural Gate Level Modeling Rangkaian digital: in_0 in_1 s_out c_out Persamaan logik: s_out = in_0 in_1 c_out = in_0 . in_1 Verilog HDL: module Example (s_out, c_out, in_0, in_1) ; input in_0, in_1 ; output s_out, c_out ; xor (s_out, in_0, in_1) ; and (c_out, in_0, in_1) ; endmodule 6 Structural Gate Level Modeling Basics of writing Verilog descriptions Identifier: name of module Value set: 0, 1, x, z Gate Primitives: and, nand, or, nor, xor, xnor, not, buf, bufif0, bufif1, notif0, notif1 Comment Lines: // Comments are useful for documenting code Ports: input, output, inout, reg, wire Gate Delays: 7 Structural gate Level Modeling MUX menggunakan tri-state primitive: s p0 p1 2:1 0 1 s p0 mux_out bufif0 s mux_out p1 bufif1 Verilog HDL: module 2_1_mux (out, p0, p1, s) ; input p0, p1, s ; output out ; bufif0 (mux_out, p0, s) ; bufif1 (mux_out, p1, s) ; endmodule Persamaan logik: out = p0 . s + p1 . s 8 Switch Level Modeling Switch-level primitives 0 ctrl 1 x 0 z 0 L L 1 z 1 H H x z z z x z x z x z 0 ctrl 1 x 0 0 z L L 1 1 z H H x z x z z z x z x z data nmos out data ctrl data out pmos data ctrl z z 9 Design Hierarchies F=A.B A B F=A+B A fet_nand2 a b c d g1 g3 g2 B fet_nor2 out fet_and4 Membentuk model gerbang NAND 4 input (NAND4) 10 Design Hierarchies module fet_nand4 (out, a, b, c, d) ; input a, b, c, d ; output out ; supply1 vdd ; wire out_nor, out_nand1, out_nand2 ; fet_nand2 g1 (out_nand1, a, b), g2 (out_nand2, c, d) ; fet_nor2 g3 (out, out_nand1, out_nand2) ; endmodule 11 RTL Modeling RTL (Register Transfer Level) RTL concentrates on specifying the movement of Data among hardware sections. time 15 20 10 0 5 module clock ; reg clk ; //The next statement starts the clock with a value of 0 at t= 0 initial clk = 1’b0 //When there is only statement in the block, no grouping is required always #5 clk = ~clk ; initial #500 $finish ; // End of the simulation 12 endmodule RESUME • • • • • Basic Concepts. Structural Gate LevelModeling. Switch Level Modeling. Design Hierarchies. RTL Modeling. 13