Week 7 lecture 2

advertisement

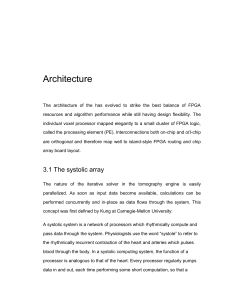

CS150 Week 7, lecture 2 Covers: 1) 2) 3) 4) 5) 1) Memory First look at timing Signals for reading from and writing to RAM Definition of timing parameters Debouncing Memory Memory Subsystem Data-path 4 Hex display (ADDR) 4 4 Hex display (DATA) Hex keypad SRAM 16X4 Counter __ EN Inside DRAM 0000 0001 DEC 1110 1111 __ CS WE … Word lines (from decoder) _ dj dj Control bit lines I/O DATA(ADDR)i 2) First look at timing Assume CS=1, Slow operation Address 1 __ 0 READ/WE 1 0 DATA 1 0 Output from RAM ? Input to RAM What to do here? 3) Signals for reading from and writing to RAM WRITE= CS WE Sense Amp ___ READ= CS WE 4) Definition of timing parameters tA tRC tCX tCO tOHA tCOT Address __ CS __ WE Data READ CYCLE Access time address data. Read cycle. Chip select output active (non-tristate). Minimum time. Chip select output valid. Maximum time. Output hold from address change. Chip deselect tri-state. 1 0 1 0 1 0 1 0 tX tOHA tCO tA tCOT WRITE CYCLE Setup time. Address stable to write pulse time(strobe). Write pulse minimum time (CS AND WE). Data setup – data must be stable this long before end of WRITE pulse (CS AND WE). Data hold – data must be stable this long after end of WRITE pulse. Write cycle. Address to address minimum time. Write recovery – end of write pulse to next address. Need to keep address line stable for this long. Write enable to tri-state output – changing from read to write. End of write to output valid. tAW TWP TDS TDH TWC TWT TWOT TWO Address __ CS __ WE Data 1 0 1 0 1 0 1 0 TWOT tDH TDS tAW tWP __ ___ Datapath needs (Katz example): INC_ADDR, CS, WE, Latch data, Enable buffer Goal: FSM to sequence inputs GO ________ STATE00 STATE00 SHR RSI __ Why use CS at all? 5) Debouncing (6.6.1, 6.6.2) S Q R _ Q S Q R _ Q Bounces: Attempt at drawing a spring: