®

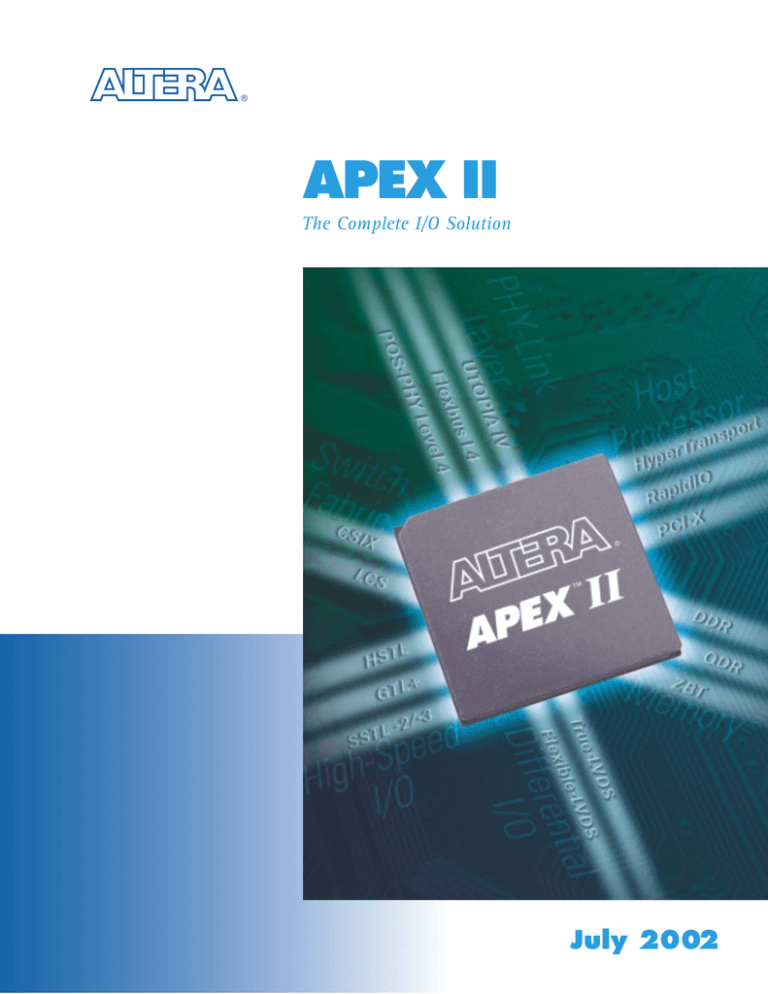

APEX II

The Complete I/O Solution

July 2002

Altera introduces the APEX™ II device family: highperformance, high-bandwidth programmable logic

devices (PLDs) targeted towards emerging network

communications applications and protocols. APEX II

devices support protocols such as the UTOPIA IV,

RapidIO™, CSIX, and POS-PHY Level 4 protocols,

making them the ideal solution for complex systems.

The APEX II device family features 1-gigabits per

second (Gbps) dedicated True-LVDS™ circuitry, phaselocked loops (PLLs), embedded system blocks (ESBs),

content-addressable memory (CAM), and enhanced

all-layer-copper interconnects.

Advanced High-Performance LVDS

■ 36 1-Gbps True-LVDS input and 36 1-Gbps True-LVDS

output channels

■ Up to 88 624-megabits per second (Mbps)

Flexible-LVDSTM input channels and 88 624-Mbps

Flexible-LVDS output channels

■ LVDS/LVPECL/PCML/HyperTransport™ I/O support

Supported I/O Protocols

Enhanced Architecture

■ RapidIO

■ 4 Kbits of memory per ESB

■ POS-PHY L4

■ Dual-port+ RAM in ESBs with

■ Flexbus

■ PCI-X

■ UTOPIA IV

■ CSIX

■ LCS

■ Zero-bus turnaround (ZBT),

double-data rate (DDR),

and quad-data rate (QDR)

memory interface support

bidirectional read/write ports

■ Eight PLL output taps

■ Six high-speed registers per

I/O element

The Complete I/O Solution

The high-density Altera® APEX II

device family offers advanced I/O

features to support a total systemon-a-programmable-chip (SOPC)

solution. APEX II FPGAs are based

on a 0.15-/0.13-µm all-layer-copper interconnect

technology to address the increasing performance and

bandwidth requirements of communication applications.

These devices offer versatility and flexibility for highperformance SOPC applications.

that can drive eight different global clock nets and/or

circuit signals for comprehensive clock management

and synthesis needs. On the following page, Table 1

describes some of the highlights of APEX II devices,

and Table 2 shows the wide range of features and

packages available.

I/O Standard Support for

High-Bandwidth Applications

The APEX II device densities range from 16,640 logic

elements (LEs) to 67,200 LEs. Based on state-of-the-art

SRAM process technology, the APEX II device family

supports a wide range of high-speed I/O standards such

as LVDS, PCML, LVPECL, HyperTransport, HSTL, and

SSTL, enabling high-speed I/O data transfers. With

True-LVDS circuitry, APEX II devices can achieve data

transfer rates of up to 1 Gbps per channel, and are

fully 64-bit, 66-MHz PCI and PCI-X compliant.

APEX II devices feature four general-purpose PLLs

APEX II devices have dedicated support for cutting-edge

I/O standards such as the HSTL, SSTL, LVPECL, PCML,

HyperTransport, CTT, GTL+, PCI-X, AGP, LVTTL, LVCMOS,

and LVDS standards—with performance up to 1 Gbps.

These I/O standards allow the APEX II device to

interface with other on-board devices in highbandwidth applications (as shown in Figure 1). APEX

II devices also feature the MultiVolt™ I/O interface,

allowing them to interface with devices using different

voltage levels, including 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

Table 3 details the support APEX II devices offer for

advanced I/O standard applications.

Figure 1. APEX II Interface Support

True-LVDS Solution

Processor

■ 1 Gbps per channel

Host Processor Interface

■ RapidIO

■ HyperTransport

■ LVDS, LVPECL, PCML, and

■ PCI-X

HyperTransport I/O

■ 36 input and 36 output channels

PLD

Memory Interface

Clock-Data

Synchronization

Memory

■ ZBT, DDR, and QDR SRAM

■ Single-data rate (SDR) and

PLD

DDR SDRAM

Flexible-LVDS Solution

■ 624 Mbps per channel

■ LVDS, LVPECL and Hyper-

Transport I/O

■ 88 input and 88 output

channels

ASSP

PHY-Link Layer Interface

Switch Fabric Interface

■ UTOPIA L1, L2, L3, and L4

■ CSIX

■ POS-PHY L2, L3, and L4

■ LCS

■ Flexbus L3 and L4

Altera Corporation

3

Table 1. APEX II Highlights

Feature

Benefit

1-Gbps True-LVDS solution

Provides 36 input and 36 output high-speed channels for high-performance applications. Supports

LVDS, LVPECL, PCML, and HyperTransport

624-Mbps Flexible-LVDS solution

Up to 88 input and 88 output channels for high-bandwidth needs. Supports LVDS, LVPECL, and

HyperTransport standards

Clock-data synchronization (CDS)

Allows up to 36 independent data channels to interface with one APEX II device

Six registers per I/O element (IOE)

Provides support for high-speed external memory interfaces such as ZBT-, DDR-, and QDR-based

memory devices

Enhanced PLLs

Supports ClockLock™, ClockBoost™, and ClockShift™ circuitry for flexible clock synthesis and clock

management with eight output taps and two off-chip outputs

Advanced ESBs

Implements dual-port RAM with bidirectional read/write ports, first-in first-out (FIFO) buffers, ROM,

and CAM. 4 Kbits of memory per ESB

PCI and PCI-X compliance

Meets all specifications of 64-bit 66-MHz PCI and PCI-X

SignalTap® II logic analysis

Improves verification of chip functionality

Density up to 67,200 logic elements

Addresses system-level needs for a high-density device

MultiVolt I/O operation

Ideal for mixed voltage systems

FineLine BGA™ packaging

Area-optimized, 1.0-mm ball pitch provides high pin count

Vertical migration

Addresses changing device density without the need to re-spin the board

Table 2. APEX II Device Overview

Feature

Maximum system gates

EP2A15

EP2A25

EP2A40

EP2A70

1,900,000

2,750,000

3,000,000

5,250,000

Typical gates

600,000

900,000

1,500,000

3,000,000

Logic elements (LEs)

16,640

24,320

38,400

67,200

104

152

160

280

4

4

4

4

Maximum RAM bits

425,984

622,592

655,360

1,146,880

True-LVDS channels

(transmit/receive)

36/36

36/36

36/36

36/36

Flexible-LVDS channels

(transmit/receive)

56/56

56/56

88/88

88/88

Maximum user I/O pins

492

540

735

1,060

724-Pin BGA

672-Pin

FineLine BGA

724-Pin BGA and

672-Pin

FineLine BGA

724-Pin BGA

672- and 1,020-Pin

FineLine BGA

724-Pin BGA

1,508-Pin

FineLine BGA

ESBs

General-purpose PLLs

Available packages

Table 3. APEX II Protocol Support for Advanced I/O Applications

Application

RapidIO

HyperTransport

Data Bus Width (Bits)

I/O Standard

Device Throughput (Gbps)

8, 16

LVDS

32.0

2, 4, 8, 16

LVDS

51.2

CSIX

32

HSTL Class I

32.0

UTOPIA IV

32

LVDS

10.0

POS-PHY Level 4

16

LVDS

10.0

PCI

64

LVTTL

4.2

4

Altera Corporation

High-Performance Differential

I/O Support

APEX II devices support multiple high-speed differential

I/O standards including True-LVDS and Flexible-LVDS

solutions, LVPECL, PCML, and HyperTransport. Differential

signaling techniques facilitate high data transfer rates,

reduce electromagnetic interference, and simplify printed

circuit board design.

Flexible-LVDS Solution

The Flexible-LVDS feature uses ESBs for SERDES functions,

enabling data transfers of up to 624 Mbps in each

Flexible-LVDS channel. APEX II devices support up to

88 receiver and 88 transmitter channels. Flexible-LVDS

channels support LVDS, HyperTransport I/O, and

LVPECL inputs, and LVDS and HyperTransport outputs.

Clock-Data Synchronization

True-LVDS Solution

The True-LVDS solution uses dedicated circuitry to

perform high-speed data serialization/deserialization

(SERDES). Each True-LVDS channel supports data

transfer rates of up to 1 Gbps, as shown in Figure 2.

The APEX II devices feature up to 36 receiver channels

and 36 transmitter channels, as well as two independent

LVDS clock domains. Each channel supports LVPECL,

PCML, and HyperTransport as well as an independent

clock multiplication feature. True-LVDS clock-data

synchronization (CDS) can correct fixed multi-bit-period

skew between different LVDS receiver channels,

synchronizing them to a single clock input.

APEX II devices offers dedicated CDS circuitry to

compensate for fixed clock-to-data skew. CDS provides

designers the flexibility of synchronizing data from up

to 36 independent high-speed sources of varying trace

lengths and skews, as shown in Figure 3. Synchronizing

the clock and data channels on each high-speed

True-LVDS channel independently significantly

simplifies board design and helps designers fully utilize

the high-speed I/O capabilities of APEX II devices.

Figure 3. APEX II Clock-Data Synchronization

Enhances

Chip-to-Chip

Performance

Clock

Figure 2. 1-Gbps True-LVDS Solution in APEX II Devices

Data

Data

Clock

Data

Clock

Clock

High-Speed External Memory

Interfaces

The IOE in APEX II devices supports emerging highspeed memory interfaces such as ZBT, DDR and QDR

SRAMs, and SDR and DDR SDRAMs. Table 4 details the

APEX II support for external memory. Each IOE consists

of two input registers, two output registers, and two

output-enable registers that facilitate these advanced

memory access standards.

In addition to the APEX II IOE, Altera also provides

APEX II optimized intellectual property (IP) MegaCore®

functions to implement memory controllers that control

Altera Corporation

5

and CAM.

Table 4. External Memory Interface Support

Memory Type

SRAM

DRAM

Memory

I/O Standard

ZBT SRAM

LVTTL

DDR SRAM

HSTL

QDR SRAM

HSTL

SDR SDRAM*

LVTTL

DDR SDRAM

SSTL

*SDRAM is synchronous DRAM

the data access to and from external memory devices.

Please refer to the IP MegaStore™ site at

http://www.altera.com/IPmegastore for a list of available

controllers for different types of memory devices.

Breakthrough Performance with

All-Layer-Copper Interconnect

APEX II devices are built on state-of-the-art all-layercopper interconnect technology. Copper has lower

resistance and better electromigration characteristics

than aluminum. Copper interconnect delays are 70%

lower than aluminum, translating to core performance

improvements, and copper is more scalable than

aluminum, resulting in smaller die sizes.

Advanced Phase-Locked Loops

APEX II devices include four embedded generalpurpose PLLs with enhanced ClockLock, ClockBoost,

and ClockShift circuitry. These devices also feature

four dedicated LVDS PLLs for high-performance I/O

applications. ClockLock circuitry reduces clock delay

and skew within the device. ClockBoost circuitry

provides clock frequency multiplication and division,

minimizing the number of external clocks needed in

the design. ClockShift circuitry provides a programmable

clock delay and phase shift capability for aligning

clock edges.

Each PLL has two output taps with a maximum of

eight output taps per device that can independently

feed eight global clock lines internal to the device.

Each APEX II device also has two external clock

output pins fed directly from two separate PLLs.

Enhanced Embedded System Blocks

APEX II devices feature up to 270 ESBs for a total of

1.1 megabit (220 bits) (Mbits) of memory. Each ESB

accommodates 4 Kbits of memory that be configured

to various data widths: 256x16, 512x8, 1,024x4,

2,048x2, or 4,096x1 bits. The 4-Kbit ESBs can be split

into two 2-Kbit blocks, effectively doubling the

number of ESBs. APEX II ESBs support bidirectional

read and write ports based on two independent clocks,

synchronous or asynchronous RAM operation, and

high-speed first-in first-out (FIFO) buffers. The ESBs

can also be configured as high-performance CAM to

be used in high-speed search applications. Multiple

ESBs can be combined to create deeper, wider RAM

6

Altera Corporation

Quartus II Development Tool

& IP Simplify Design

The Altera Quartus™ II development

tool allows designers to process

multi-million gate designs. The

Quartus II software supports systemlevel solutions, integrates seamlessly with standard

revision control software, and allows designers to

implement advanced features such as LVDS, CAM, and

PLLs into their device designs. Using the Quartus II

software, designers can easily integrate complex IP

cores into their designs.

As shown in Table 5, the Quartus II software offers a

variety of features to aid the system designer, making

it the ideal platform for multi-million-gate designs.

Table 5. Quartus II Highlights

Feature

Benefit

LogicLock™ incremental

design capability

Allows for incremental optimization of a design

SignalTap embedded logic

analyzer

Reduces verification time by enabling designers to see

internal signal values while the system is running at speed

PowerFit™ fitting technology

Optimizes designs based on user's timing specifications and

meets design requirements with minimal user effort

NativeLink™ integration

Allows for seamless integration with third-party tools

Internet awareness

Provides up-to-the-minute information and file exchanges,

software updates, and support services through the Internet

Contact Altera Today

The APEX II device family provides the ideal solution

for your SOPC design needs. Visit the Altera web site

today to learn more about the APEX II device family and

its complete I/O solution at http://www.altera.com.

Altera Corporation

7

®

The Programmable Solutions Company ®

Altera Offices

Altera Corporation

101 Innovation Drive

San Jose, CA 95134

USA

Telephone: (408) 544-7000

http://www.altera.com

Altera European Headquarters

Holmers Farm Way

High Wycombe

Buckinghamshire

HP12 4XF

United Kingdom

Telephone: (44) 1 494 602 000

Altera Japan Ltd.

Shinjuku i-Land Tower 32F

5-1, Nishi-Shinjuku, 6-Chome

Shinjuku-ku, Tokyo 163-1332

Japan

Telephone: (81) 3 3340 9480

http://www.altera.com/japan

Altera International Ltd.

2102 Tower 6

The Gateway, Harbour City

9 Canton Road

Tsimshatsui Kowloon

Hong Kong

Telephone: (852) 2945 7000

Copyright © 2002 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and

logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries.

HyperTransport is a trademark of HyperTrabsport Consortium. RapidIO is a trademark of the RapidIO Trade Asspciation. All other product or service names are the property of their

respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

GB-APEX11-2.0