1

advertisement

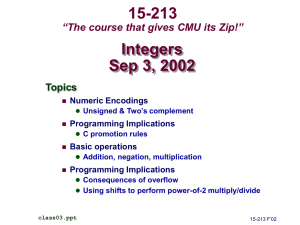

1 11.1 Shift-Add Multiplication Figure 11.1 Multiplication of 4-bit numbers in dot notation. 2 Example shift-add multiplication: Works basically like you do "long-hand" multiplication except that you (1) add partial products together as you get them, and (2) shift running total to the right after it is recalculated. This eliminates need to add digits of the partial product to nothing. It also ensures same column of digits are always added. Digits shifted to the right of these columns are simply carried down. 3 • Recurrence equation describing above process z ( j 1) ( z ( j ) y j x 2 k )2 1 with z (0) 0 and z (k) z add Shift right 4 Shift-add example: 10100011 Figure 11.2 Step-by-step multiplication examples for 4-digit unsigned binary and decimal numbers. 5 Signed integer multiplication • Signed-magnitude numbers can be multiplied by using the shift-add algorithm discussed above, and deriving the sign of the products as XOR of the two input sign bits. • In the last multiplication step, we must subtract, rather than add, the partial product yk-1x. e.g., x (1011)2’s-compl = -8x +2x+x = -5x 6 Example: Two’s-complement multiplication Figure 11.3 Step-by-step multiplication examples for 4-digit 2’s-complement numbers. 7 11.2 Hardware Multipliers Figure 11.4 Hardware multiplier based on the shift-add algorithm. 8 Figure 11.5 Shifting incorporated in the connections to the partial product register rather than as a separate phase. 9 Fast hardware multiplication • Full-tree multiplier • Array muplier HA: half adder, FA: full adder, MA: modified full adder 10 Figure 11.6 Schematic diagrams for full-tree and partial-tree multipliers. 11 Figure 11.7 Array multiplier for 4-bit unsigned operands. 12 13 14 8-bit array multiplier (unsiged) 15 16 Figure 11.9 Division of an 8-bit number by a 4-bit number in dot notation. 17 • Recurrence equation describing above process z ( j ) 2 z ( j 1) y k j x 2 k with z (0) z and z (k) 2 k s shift subtract 18 Unsigned operands, z: 2k-bit, x: k-bit 1 1 Figure 11.10 Step-by-step division examples for 8/4-digit unsigned binary integers and decimal fractional numbers. 19 Unsigned operands, z: k-bit, x: k-bit Figure 11.11 Step-by-step division examples for 4/4-digit unsigned binary integers and fractional numbers. 20 Dividing signed number: (1) Convert operands to into unsigned values, perform unsigned division (2) At then end, adjust signs for y (quotient) and s (remainder) 21 11.5 Hardware Dividers k cycle for 2k/k division Figure 11.12 Hardware divider based on the shift-subtract algorithm 22 Figure 11.13 Shifting incorporated in the connections to the partial remainder register rather than as a separate phase. 23 Figure 11.14 Array divider for 8/4-bit unsigned integers. 24 Array Divider (unsigned) 25 Conditional Subtractor • q=0 – co = majority ( r, d, ci ) ; – s=r // identity • q=1 – co = majority ( r, d, ci ) ; – s = r XOR d XOR ci // subtraction 26 11.6Programmed Division Figure 11.15 Register usage for programmed division superimposed on the block diagram for a hardware divider. 27