Document 14359196

advertisement

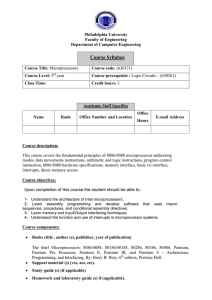

University of Houston Engineering Technology College of Technology ELET 3405: Microcomputer Architecture Required Course Class/laboratory schedule: Tue -­‐Thu: 10-­‐11 am COURSE CATALOG DESCRIPTION ELET 3405: Microcomputer Architecture Cr. 3. (3-­‐0). Architecture and operation of microprocessor-­‐based systems including basic hardware, software, and interfaces. PREREQUISITES ELET 2300: Introduction to C++ Programming and ELET 2303: Digital Systems TEXTBOOKS/REQUIRED MATERIALS Intel Microprocessors 8086/8088, 80186, 80286, 80386, and 80486: Architecture, Programming, and Interfacing, 8th ed., by Barry B. Brey COURSE LEARNING OUTCOMES AND PERFORMANCE CRITERIA By the end of the course, students will: • Learn the main components of a modern microprocessor • Learn the principles of microcomputer programming and the underlying cooperation of hardware and software • Implement and present a project in assembly language Grading policy: 1. Four Quizzes: 75% of final grade 2. Four homework sets: solutions will be posted and discussed in class but will not be graded. 3. Four lab assignments: 15% of final grade 4: Final project presentation (small groups of 3-­‐4 students): 10% of final grade PROGRAM OUTCOMES COVERED BY THE COURSE This course addresses outcomes: a, b, c, f, g, h, i, j, k TAC-­‐ABET CRITERION 3 OUTCOMES: h, i, j, and k: You are encouraged to become an active member of professional societies (national, regional, and local chapters) related to your chosen profession. As a member, you will normally receive trade, magazine, journal, and newsletter subscriptions thereby allowing you to maintain, in general, a connection with your profession. Whenever applicable, outside speakers will be invited to discuss relevant developments and events that relate to lifelong learning, quality, timeliness, continuous improvement, global issues, and societal and environmental concerns. This practice represents a Prepared by G. Zouridakis Spring 2010 University of Houston Engineering Technology College of Technology means for keeping technically current and aware of changes and challenges in all aspects of your profession. TOPICS COVERED UNIT I. INTRODUCTION TO THE INTEL MICROPROCESSORS A. The Evolution of the 16-­‐bit Microprocessor B. Basic 8086 and 8088 Architecture C. Memory and the 8086 and 8088 D. The Programming Model E. Data Formats F. The Instruction Set G. Assigned Problems UNIT II. ADDRESSING MODES A. Data-­‐Addressing Modes B. Register Addressing C. Immediate Addressing D. Direct Data Addressing E. Base-­‐Plus-­‐Index Addressing F. Register Relative Addressing G. Base Relative-­‐Plus-­‐Index Addressing H. Program Memory-­‐Addressing Modes I. Stack Memory Addressing J. Assigned Problems UNIT III. DATA MOVEMENT INSTRUCTIONS A. MOV Revisited B. PUSH/POP C. Load-­‐Effective Address D. String Data Transfers E. Miscellaneous Data Transfer Instructions F. Segment Overide Prefix G. Assigned Problems UNIT IV. ARITHMETIC AND LOGIC INSTRUCTIONS A. Addition, Subtraction, and Comparison B. Multiplication and Division C. BCD and ASCII Arithmetic D. Basic Logic Instructions E. Shifts and Rotates F. String Comparisons Prepared by G. Zouridakis Spring 2010 University of Houston Engineering Technology College of Technology G. Assigned Problems Unit V. PROGRAM CONTROL INSTRUCTIONS A. The Jump Group B. Subroutines C. Interrupts D. Machine Control Instructions E. Sample Programs F. Assigned Problems UNIT VI. 8086/8088 HARDWARE SPECIFICATIONS A. Pinouts and the Pin Functions B. Clock Generator C. Bus Buffering and Latching D. Bus Timing E. READY and the Wait State F. Minimum Mode versus Maximum Mode G. Assigned Problems UNIT VII. MEMORY INTERFACE A. Memory Devices B. Address Decoding C. 8088 Memory Interface D. 8086 Memory Interface E. Dynamic RAM Controllers F. Assigned Problems UNIT VIII. BASIC I/O INTERFACE A. Basic I/O Interface B. I/O Port Address Decoding C. The 8255A Programmable Peripheral Interface D. The 8279 Programmable Keyboard/Display Interface E. The 8254 Programmable Interval Timer F. The 8251A Programmable Communications Interface G. Assigned Problems Successful completion of this course fulfills the technical content curricular requirements for the degree plan in Computer Engineering Technology CETE. Tentative Schedule Laboratories: • Lab Zero -­‐ Introduction to MS-­‐DOS/Command Window • Lab One -­‐ Debug, Registers and Real-­‐Mode Addressing • Lab Two -­‐ Debug, Assembly and Memory Addressing Prepared by G. Zouridakis Spring 2010 University of Houston Engineering Technology College of Technology • Lab Three-­‐ Data Movement Instructions • Lab Four -­‐ Basic Math Instructions • Lab Five -­‐ Multiplication and Division Instructions • Lab Six -­‐ Jump and Loop Instructions • Lab Seven -­‐ Software Interrupts • Lab Eight -­‐ Software Interrupts II • Lab Nine -­‐ Final Project (MASM) Prepared by G. Zouridakis Spring 2010