Document 13561417

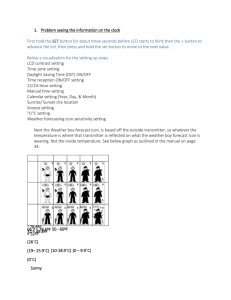

advertisement