Research Journal of Applied Sciences, Engineering and Technology 4(1): 27-32,... ISSN: 2040-7467 ©Maxwell Scientific Organization, 2012

advertisement

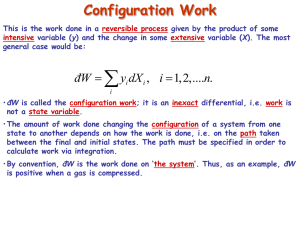

Research Journal of Applied Sciences, Engineering and Technology 4(1): 27-32, 2012 ISSN: 2040-7467 ©Maxwell Scientific Organization, 2012 Submitted: August 26, 2011 Accepted: September 30, 2011 Published: January 01, 2012 Delay Reduction in Optimized Reversible Multiplier Circuit 1 1 Mohammad Assarian, 2Majid Haghparast and 3Keivan Navi Department of Computer Engineering, Dezful Branch, Islamic Azad University, Dezful, Iran 2 Department of Computer Engineering, Shahre-Rey Branch, Islamic Azad University, Tehran, Iran 3 Faculty of Electrical and Computer Engineering, Shahid Beheshti University, Tehran, Iran Abstract: In this study a novel reversible multiplier is presented. Reversible logic can play a significant role in computer domain. This logic can be applied in quantum computing, optical computing processing, DNA computing, and nanotechnology. One condition for reversibility of a computable model is that the number of input equate with the output. Reversible multiplier circuits are the circuits used frequently in computer system. For this reason, optimization in one reversible multiplier circuit can reduce its volume of hardware on one hand and increases the speed in a reversible system on the other hand. One of the important parameters that optimize a reversible circuit is reduction of delays in performance of the circuit. This paper investigates the performance characteristics of the gates, the circuits and methods of optimizing the performance of reversible multiplier circuits. Results showed that reduction of the reversible circuit layers has lead to improved performance due to the reduction of the propagation delay between input and output period. All the designs are in the nanometric scales. Key words: Circuit delay, critical path, nanotechnology, reversible logic circuit, reversible logic gate, reversible multiplier C INTRODUCTION According to Moore's law every 18 months to two years, the number of transistors on the chip will double. Researchers concluded that in coming years as technological limitations to reach Moore's Law. Because increasing the number of transistors on the chip closer distance, the heat generated by the internal energy loss, damage will be parts (Haghparast et al., 2009). A gate (circuit) is reversible if and only if the inputs can be detected from the observed outputs, and the outputs can be detected from the inputs. In this case KTLn2 joules of energy loss can be prevented (Landauer, 1961). This loss of energy is per bit of information goes to waste. A circuit is reversible if and only if the input vector can be uniquely recovered from the output vector. Consequently, a reversible logic gate or circuit has to have equal number of inputs and outputs. Such gates or circuits allow the reproduction of the inputs from observed outputs and we can determine the inputs from the outputs (Perkowski et al., 2001; Perkowski and Kerntopf, 2001; Kernto pf etal., 2004). The important parameters which play a major role in the design of an optimized reversible logic circuit are: C C C C Number of garbage outputs (Gout): Garbage outputs are some outputs that are not used for further computations in the circuit. Number of Gates (NOG): The number of reversible gates used to realize the function. Quantum Cost (QC): The Quantum Cost (QC) of a reversible circuit is defined as the number of 1×1 or 2×2 reversible quantum or logic gates that are needed to realize the circuit. Total logical calculations (circuit cost): One of the main factors of a circuit is its hardware complexity. One of the important components in computer is reversible circuit multiplier. This study tries to improve the reversible multiplier design with nanometeric dimensions. Designed circuit with low power consumption in nanotechnology can be used for next generation computers. This logic has applications in various research areas such as quantum computing, optical computing processing, DNA computing, and nanotechnology. In the logical circuits, as the circuit layers decrease, the response time and delay time also decreases. The delay in one circuit will be equal to the size of its critical path. The latter is the longest path between the input and output. This study designs a circuit, by changing the circuit structure which would have a better performance than other circuits. Number of constant inputs (Gin): The inputs that are added to an n×k function to make it reversible are called constant inputs. Corresponding Author: Majid Haghparast, Department of Computer Engineering, Shahre-Rey Branch, Islamic Azad University, Tehran, Iran 27 Res. J. Appl. Sci. Eng. Technol., 4(1): 27-32, 2012 A FG B A B C P=A Q=A B Fig. 1: Feynman gate TG B C A B C D Q=B R = AB C Fig. 2: Toffoli gate A B C NG Q = AB C R = AC B Fig. 5: New gate P =A A P =A TSG P=A Q = AC B R = (AC B) D S = (AC B).C (AB D) Fig. 6: TSG gate P=A FRG A B C D Q = AB AC R = AC AB HNG P=A Q= B R= A B C S = ( A B).C AB D Fig. 3: Fredkin gate Fig. 7: HNG gate A B C P=A PG which is also a 3×3 reversible gate is shown in Fig. 5 (Khan, 2002). Some of the 4×4 reversible gates are presented below: The TSG gate is shown in Fig. 6 (Haghparast and Navi, 2008a). This gate has QC of 13. HNG gate is also show in Fig. 7 (Haghparast and Navi, 2008b). This gate has QC of 6. If the input quantity D is zero, the gate will operate like Full adder. This is used in addition and multiplication circuits. One of the main factors of a circuit is its hardware complexity which is known as Total Logical Calculation: Q= A B R = AB C Fig. 4: Peres gate BACKGROUND The reversible logic gates are studied. The most important of which is Feynman gate (FG), also known as controlled-not gate (CNOT). This is a 2×2 reversible gate (Feynman, 1985) that is shown in Fig. 1. Under circumstances where the control input A is 1, the Q will have negative quantity B, otherwise the positive quantity will be B. Since fan-out is not allowed in reversible logic circuits, the Feynman gate is used as the fan-out gate to copy a signal. The QC of this gate is one. Some of the reversible 3×3 gates can be expressed as follows: The Toffoli gate (TG) which is recognized as controlled controlled-NOT (CCNOT) is shown in Fig. 2 (Toffoli, 1980).If C equals to zero the output R will be A.B. If the control input C is 1, then the R will be (A.B)’. The QC of this gate is five, i.e., it is implemented using five quantum 2×2 gates. Fredkin gate (FRG) is a control permutation gate which is shown in Fig. 3 (Fredkin and Toffoli, 1982). This is used to make D flip-flop and shift register (Dhaka et al., 2009). This gate has QC of 5. Peres Gate (PG) which is also known as New Toffoli Gate can be implemented by one FG and one TG as shown in Fig.4 (Peres, 1985). If the C input in the Peres gate is considered as zero, it can be used as a half adder. Though it seems more complex than the Toffoli gate, its QC is 4 which is less than QC of a Toffoli gate. The New gate " = A two input EX-OR gate calculation $ = A two input AND gate calculation * = A NOT calculation T = Total logical calculation Total logical calculation is the count of the XOR, AND, PG has two XORs and one AND in the output expressions. Therefore: T (PG) = 2"+ 1$ It is to be noted that in reversible logic we can use Feynman gate for making fan-out. Thus, if we have two equal output expressions (or part of the output expressions), then we can copy it with Feynman. In this situation, the logical complexity is just one XOR more than the expression. For example, for TSG we need 1XOR+ 1AND+3NOT to produce (A'C'r B'). Then we make two copies of (A'C'r B') using two Feynman gates. Thus we can state that the total logical calculation for TSG is: 28 Res. J. Appl. Sci. Eng. Technol., 4(1): 27-32, 2012 Table 1: Comparative experimental results of different reversible multiplier circuits No. of garbage Total quantum Reversible multiplier No. of gates outputs cost Our proposed design 28 28 137 (HNG, PG, TG) (Haghparast et al., 2009) 28 28 137 (HNG, PG, TG) (Haghparast et al., 2009) 28+24FG = 52 52 137 (HNG, PG, FG) (Haghparast et al., 2008) 28+24FG = 52 52 140 (HNG, PG, FG) (Shams et al., 2008) 28+24FG = 52 56 244 (MKG, PG, FG) (Thapliyal and Srinivas, 2006) 29+24FG = 53 58 273 (TSG, FRG, FG) (Thapliyal et al., 2005) 40+24FG = 64 56 236 (NG, PG, FRG, FG) (Banerjee and Pathak, 2009) 56 26 144 (PG, PPGC) (Zhou et al., 2010) 44 49 137 (HNG, PG, FG) No. of constant inputs 28 Total logical calculation 71"+36$ Delay 6 28 71"+36$ 7 52 104"+36$ 7 52 104"+36$ 7 56 104"+52$+36* 7 58 122"+103$+71* 7 55 92"+100$+68* 7 28 266" 7 28 92"+34$ 10 gates where HNG gates are used as Full adder and Peres gates as half adder. The mentioned reversible multiplier is made up of HNG, PG and FG gates which are based on parameters shown in Table 1 and are calculated as follows: C C Fig. 8: Partial products in a 4×4 multiplication T (TSG) = (1" +1$ +3*) + (2") (for copy) + (1") (for last XOR of the R-expression) + (2" + 2$) (for last part of Sexpression) = 6" + 3$ + 3* C C Therefore, C T(FG) = " T(TG) = " + $, T(FRG) = 2" + 4$ + 2* T(NG) = 2" + 2$ + 3* T(HNG) = 5" + 2$ Number of constant inputs (Gin): Gin (Fig. 9)+ Gin (Fig. 10)= (16 Gin(PG)+24 Gin(FG)) + (4 Gin (PG)+8 Gin (HNG)) = (16 *1+24 *1) + (4 *1+8 *1) = 52 Number of garbage outputs (Gout): Gout (Fig. 9) + Gout (Fig. 10) = (16 Gout (PG) +24 Gout (FG)) + (4Gout (PG) +8 Gout (HNG)) = (16*2+0) + (4*1+8*2) =52 Number of gates (NOG): (16PG+24FG) + (4PG+8HNG) = 52 Quantum cost (QC): QC (Fig. 9) + QC (Fig. 10) = (16 QC (PG) +24 QC (FG)) + (4 QC (PG) +8 QC (HNG)) = (16 *4+24 *1) + (4 *4+8 *6) =152 Total logical calculations (circuit cost): T (Fig. 9) + T (Fig. 10) = (16 T (PG) + 24 T (FG)) + (4 T (PG) + 8T (HNG)) = (16 (2"+ 1$) +24 ") + (4 (2"+ 1$) + 8 (5" + 2$)) = 104" + 36$ Our proposed reversible multiplier circuit and their assessment: Our proposed reversible multiplier has two main parts. It is depicted in Fig. 11 and 12. First the partial products which act horizontally are made by Peres gates and Toffoli gates, which are shown in Fig. 11. The Fig. 11 circuit has 7 Peres gates and 9 Toffoli gates. Then we have summation network which is shown in Fig. 12. The Fig. 12 circuit has 8 HNG gates and 4 Peres gates where HNG gates are used as Full Adder and Peres gates are used has Half Adder. In this design only the structure of the circuit is changed but the number of gates have not been altered. As the layers of a circuit are less, its critical path (longest input to output path) is shorter. The shorter Investigating the optimized reversible multiplier circuit: The operation of the 4×4 multiplier is depicted in Fig. 8 which consists of 16 partial product bits of the form of xiyi. The reversible 4*4 multiplier has two main parts. First the partial products which act horizontally are made by Peres gates and Feynman gates, which are shown in Fig. 9 (Shams et al., 2008). The Fig. 9 circuit has 16 Peres gates and 24 Feynman gates where Feynman gates are used as fan-out. Then we have a reversible summation network which is shown in Fig. 10 (Haghparast et al., 2009). The Fig. 10 circuit has 8 HNG gates and 4 Peres 29 Res. J. Appl. Sci. Eng. Technol., 4(1): 27-32, 2012 y3 FG 0 y2 FG FG 0 PG PG 0 PG x3y0 g25 g24 FG FG 0 0 PG PG FG x2y 1 g 19 g18 x2 FG x2y 0 g17 g16 FG FG 0 FG 0 PG FG x3 FG x3y1 g27 g26 x 2y2 g21 g20 0 PG FG x 3y 2 g29 g28 FG x2y3 g23 g22 PG FG FG 0 0 FG x3y3 g31 g30 y0 FG y1 FG FG 0 FG x1 0 PG PG PG PG x1y3 g15 g14 x1 y2 g13g 12 x1y1 g 11 g10 x 1y 0 g9 g8 0 0 FG FG FG 0 x0 0 PG PG PG PG x 0y3 g 7 g 6 x0 y2 g 5 g 4 x0y1 g3 g2 x 0y0 g1 g0 Fig. 9: Reversible partial products generation circuit (Shams et al., 2008) 0 x 2y 3 x 3y 2 0 x 3y 1 x2y 2 0 x 1y 2 x 2y 1 HNG g10g 9 HNG PG g8 g7 g6 HNG g19 g18 P6 0 x0y3 x3y 0 0 x 0y 2 x2y0 0 x 1y 0 x 0y1 x 0y 0 PG HNG g5 0 x3y3 P7 x1y 3 0 g4 g3 0 0 0 HNG HNG HNG g 17 g16 P5 g15 g14 HNG g2 g1 P3 g0 0 x1y 1 PG g13 g12 P4 PG g11 P2 P1 P0 Fig. 10: Reversible multiplier circuit – summation network (Haghparast et al., 2009) the path, the propagation delay is shorter and the response time is proportionally shorter. The critical path is shown in Fig. 10 and 12 by doted lines. As it is demonstrated in Fig. 10 the number of layers is 7 but in Fig. 12 this number is 6. The suggest delay in our proposed design is reduced. Consequently, according to Table 1, the proposed circuit has lower delay than the other circuits. This makes our propose circuit as one which is comparatively much better than similar one because of reducing the delay period in the input to output path. The gates which are used in our proposed reversible multiplier circuit are HNG, PG and TG gates. The count of the main parameters of our proposed reversible multiplier is as follows: C C C C C Number of constant inputs (Gin): Gin (Fig. 11) + Gin (Fig. 12) = (7 Gin(PG)+9 Gin(TG)) + (4 30 Gin(PG)+8 Gin (HNG)) = (7 *1+9 *1) + (4 *1+8 *1) =28 Number of garbage outputs (Gout): Gout (Fig. 11) + Gout (Fig. 12) = (7 Gout (PG) +9 Gout (TG)) + (4Gout (PG) +8 Gout (HNG)) = (8+0) + (4*1+8*2) = 28 Number of gates (NOG): (7PG+9TG) + (4PG+8HNG) = Quantum cost (QC): QC (Fig. 11) + QC (Fig. 12) = (7 QC (PG) +9 QC (TG)) + (4 QC (PG) +8 QC (HNG)) = (7 *4+9 *5) + (4 *4+8 *6) =137 Quantum cost (QC): QC (Fig. 11) + QC (Fig. 12) = (7 QC (PG) +9 QC (TG)) + (4 QC (PG) +8 QC (HNG)) = (7 *4+9 *5) + (4 *4+8 *6) =137 Total logical calculations (circuit cost): T (Fig. 11) + T (Fig. 12) = (7 T (PG) + 9 T (TG)) + (4 T (PG) + 8T (HNG)) = (7 (2"+ 1$) +9 (" + $)) + (4 (2"+ 1$) + 8 (5" + 2$)) = 71" + 36$ = 28 Res. J. Appl. Sci. Eng. Technol., 4(1): 27-32, 2012 y3 y2 0 y1 0 PG x0 0 TG x0 y3 G y0 0 TG TG x 0y 2 x 0y 1 x 0y 0 0 0 0 x1 0 PG TG x1 y3 G TG TG x 1y 2 x 1y 1 x 1y 0 0 0 0 x2 0 PG TG x2 y3 G TG TG x 2y 2 x 2y 1 x 2y 0 0 0 0 x3 0 PG x3 y3 G TG P G PG x 3y 2 G G PG x 3y 0 G x 3y 1 G Fig. 11: Reversible partial products generation circuit 0 x1 y2 x2y1 x3 y0 0 x1 y1 x2y 0 0 x 3y1 x2y2 PG 0 x 2y 3 x3 y2 0 HNG HNG 0 PG g4 0 x0y 3 0 0 x 0y2 HNG HNG HNG HNG g 19 g18 P 7 P6 x1 y3 0 0 x 3y3 HNG g0 g 2 g1 g6 g 5 g 8 g7 PG HNG g3 g1 7 g 16 P5 g1 5 g14 P4 x 0y0 g 13 g1 2 P3 0 x 1y0 x0y1 PG g1 1 g1 0 P2 g9 P1 P0 Fig. 12: Our proposed reversible summation network The proposed reversible circuit can be used for the design of complicated nanotechnology application. All the designs are in the nanometric scales. CONCLUSION This study has presented an optimal reversible multiplier circuit which has the design configuration and feature to reduce the circuit delay time. It can be placed as a better reversible multiplier in the computational circuits. It can be said that the proposed reversible multiplier has a faster performance speed than similar reversible circuits. REFERENCES Banerjee, A. and A. Pathak, 2009. An Analysis of Reversible Multiplier Circuits, Retrieved from: http://arxiv.org/abs/0907.3357v1. 31 Res. J. Appl. Sci. Eng. Technol., 4(1): 27-32, 2012 Peres, A., 1985. Reversible logic and quantum computers. Phy. Rev., 32: 3266-3276. Perkowski, M. and P. Kerntopf, 2001, Reversible logic, Invited Tutorial, Proc. Euro-Micro, Warsaw, Poland. Perkowski, M., A. Al-Rabadi, P. Kerntopf, A. Buller, M.Chrzanowska-Jeske, A. Mishchenko, M.A. Khan, A. Coppola, S. Yanushkevich, V. Shmerko and L.Jozwiak, 2001. A general decomposition for reversible logic. Proceeding RM, Starkville, pp: 119-138. Shams, M., M. Haghparast and K. Navi, 2008. Novel reversible multiplier circuit in nanotechnology. World Appl. Sci. J., 3(5): 806-810. Thapliyal, H. and M.B. Srinivas, 2006. Novel reversible multiplier architecture using reversible TSG gate, IEEE Internatinal Conference Computer System Applications, pp: 100-103. Thapliyal, H., M.B. Srinivas and H.R. Arabnia, 2005, AReversible Version of 4×4 Bit Array Multiplier with Minimum Gates and Garbage Outputs, Int. Conf. Embedded System, Applications (ESA’05), Las Vegas, USA, pp: 106 114. Toffoli, T., 1980. Reversible computing. Tech Memo MIT/LCS/TM-151. MIT Lab for Computer Science. Zhou, R., Y. Shi, J. Cao and H. Wang, 2010. Comment on design of a novel reversible multiplier circuit using HNG gate in nanotechnology. World App. Sci. J., 10(2): 161-165. Dhaka, N.M., L.N. Jamal and H.M.H. Babu, 2009. Efficient reversible montgomery multiplier and its application to hardware cryptography. J. Comp. Sci., 5(1): 49-56. Feynman, R., 1985. Quantum mechanical computers. Optics News, 11: 11-20. Fredkin, E. and T. Toffoli, 1982. Conservative logic. Int. J. Theor. Phys., 21: 219-253. Haghparast, M. and K. Navi, 2008a. A novel fault tolerant reversible gate for nanotechnology based systems. Am. J. Appl. Sci., 5(5): 519-523. Haghparast, M. and K. Navi, 2008b. A novel reversible BCD adder for nanotechnology based systems. Am. J. Appl., Sci., 5(3): 282-288. Haghparast, M., S.J. Jassbi, K. Navi and O. Hashemipour, 2008. Design of a novel reversible multiplier circuit using HNG gate in nanotechnology. World Appl. Sci. J., 3(6): 974-978. Haghparast, M., M. Mohammad, K. Navi and M. Eshghi, 2009. Optimized reversible multiplier circuit. J.Circuits Syst. Comp., 18(2): 311-323. Khan, M.H.A., 2002. Design of Full Adder with Reversible Gates, Int. Conf. Computer and Information Technology, Dhaka, Bangladesh, pp: 515-519. Kerntopf, P., M.A. Perkowski and M.H.A. Khan, 2004, On universality of general reversible multiple valued logic gates, IEEE Proc. 34th Int. Symp. Multiple Valued Logic (ISMVL’04), pp: 68-73. Landauer, R., 1961. Irreversibility and heat generation in the computing process. IBM J. Res. Dev., 5: 183-191. 32