Achieving Power and Area Reduction by Redesigning Existing Memory IC Shefali Sharma

advertisement

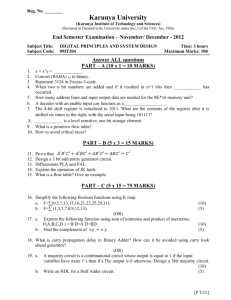

International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 7 - May 2014 Achieving Power and Area Reduction by Redesigning Existing Memory IC Shefali Sharma#1, Bipan Kaushal*2 # M.E. student, Assistant Professor Deptt. of Electronics and Communication PEC University of Technology Chandigarh, India Abstract—With increase in complexity and shrinking technology below 100 nm, reducing power consumption and over all power management on chip are the key challenges. Multi-bit flip-flop is an effective method for clock power consumption reduction proven by the researchers. By sharing the inverters in the flipflops, the total number of inverters can be reduced in a multi-bit flip-flop. So, here, in this paper we have redesigned the internal circuitry of an IC which is an important memory element in digital systems, using 4-bit and 8-bit flip flop. Experimental results show that our approach is very efficient in reducing its area and power consumption, and hence will be very useful in modern vlsi circuit designs. Keywords— sub-micron, drive strength, master slave, multi bit flip flop, merger. I. INTRODUCTION Earlier, the two main things- increasing the speed and reducing the area of digital systems have been the main focus points of the digital system designers. But now, with the evolution of portable systems and advanced deep Sub-Micron fabrication technologies, power dissipation has become another critical design factor. As the low power design reduces cooling cost and thus increases the reliability especially for high density systems. Also, the lower power consumption requirement continues to increase significantly because the components have become smaller, require more functionality and battery-powered.[2] For VLSI chips flip-flop is a basic and important building circuit. [4]If larger multi-bit flip-flops are used in place of smaller single bit flip-flops, device variations in the corresponding circuit can be effectively reduced. Multi bit flip flop is a cluster of many single-bit flip-flops i.e. they share the drive strength. So, the use of multi-bit flip-flops can reduce clock circuitry and power consumption as well. II. MULTI-BIT FLIP FLOP Given below is the schematic of the technique of merger of two 1-bit flip-flops into one 2-bit flip-flop (fig. 1). ISSN: 2231-5381 Fig. 1 Method of merging two 1-bit flip-flops into one 2-bit flip-flop. So, we can see that common clock is being provided to the multi bit flip flop circuit. Hence, by merging single-bit flip- http://www.ijettjournal.org Page 340 International Journal of Engineering Trends and Technology (IJETT) – Volume X Issue Y- Month 2013 flops into one multi-bit flip-flop, the duplication of inverters can be avoided. So, by using this concept we designed 4-bit and 8-bit D flip flops. Here is the block diagram of 4-bit flip flop. Fig 5. Output Waveform. III. CONVENTIONAL IC 4731B Fig. 2 Block Diagram showing 4-bit D flip flop. The output waveform for the 4-bit D flip flop is as given below: The 4731B is a CMOS quad 64-bit shift register. It contains four identical 64-bit shift registers on one chip. So, here we are taking one of the 64-bit registers. It has a serial input, a clock input and a serial output from the last flip flop. This is the only output that is externally accessible. All flip flops are master-slave flip flops. Master slave flip flop is also called pulse triggered flip flop. Master flip flop is triggered when clock=1 and slave flip flop is triggered when clock =0 and slave copies the master. The information from inputs is transferred to master flip-flop at positive/leading edge of the clock pulse and slave flip-flop remains disabled. A negative/trailing edge information is transferred at the output of slave and master remain disabled. The output of master-slave flip-flop changes only at the end of clock pulse and race around condition never occurs. The slave just copies the master. Since output of the master slave changes only after arrival of complete pulse, that is why it is also called pulse triggered flip flop. Fig 3. Simulation result of 4-bit flip flop. The block Diagram for 8-bit D flip flop is generated using Xilinx software. Fig 4. Block Diagram showing 8-bit D flip flop. Here are the simulation results for multi bit flip flop. ISSN: 2231-5381 http://www.ijettjournal.org Fig.6 Block Diagram of IC 4731B. Page 341 International Journal of Engineering Trends and Technology (IJETT) – Volume X Issue Y- Month 2013 The cadence generated internal diagram of 4731B is as given: flop we are able to reduce the total power consumption of the circuit and hence is very advantageous. Fig. 7 Internal Circuitry of 4731B. IV. PROPOSED DESIGN USING 4 BIT D-FLIP-FLOP: Instead of using conventional D flip flops. In this section, we will introduce how to design a shift register using multi-bit flip-flop. Since we want to replace the single bit flip-flops with multi-bit flip-flop that must have identical clock conditions and similar type of logic levels to set or reset the flip flops. Fig. 9 Cadence generated internal circuitry. The output waveform is as shown: Fig. 10 Output waveform. V. DESIGN USING 8-BIT D FLIP-FLOP: Fig. 8 Block Diagram using 4-bit D flip flops. We employed the concept of multi bit flip flop in designing a shift register used in this digital system. By using multibit flip ISSN: 2231-5381 Extending the concept further we used 8-bit master slave D flip flops, we are able to further reduce the power consumption of the circuit. So, the block diagram is as shown: http://www.ijettjournal.org Page 342 International Journal of Engineering Trends and Technology (IJETT) – Volume X Issue Y- Month 2013 From the power analysis table it is clear that by employing 4bit D flip flop and 8-bit D flip flop there is a reduction of 10.28% and 11.43% in the total power respectively. Also, there is significant reduction in area as well. With 4-bit D flip flop and 8-bit D flip flop the total area on IC is reduced by 12.66% and 14.13% respectively. Hence it is clear that our approach is very efficient in area and power reduction. VIII. Fig. 8 Internal circuitry using 8-bit D flip flops. CONCLUSION We implemented the concept of 4-bit and 8-bit D flip flop in redesigning the constituent stages of an integrated circuit with which we are able to effectively reduce the area and power consumption of the circuit. The Simulated waveforms of the resultant circuit are the same as that of the original integrated circuit. We carried out the implementation using cadence and Xilinx software. The schematic and waveforms are given in the paper. This basic concept of multi bit flip flop can be extended to the design of other sequential circuits in future. VI. POWER AND AREA ANALYSIS REFERENCES TABLE I POWER ANALYSIS S. No. 1. 2. 3. IC 4731B Using 1-bit D flip flop 4-bit D flip flop 8-bit D flip flop [1] Leakage Power(nW) 457.389 Dynamic Power(nW) 273430.625 Total Power(nW) 273888.014 441.674 245270.016 245711.690 439.852 242136.964 242576.816 TABLE II AREA ANALYSIS [2] [3] [4] Area [5] 1. IC 4731B Using 1-bit D flip flop 12688 [6] 2. 4-bit D flip flop 11082 [7] 3. 8-bit D flip flop 10895 [8] S. No. [9] VII. RESULTS AND DISCUSSIONS We wrote the vhdl code for the IC and simulated it in cadence. The results obtained are as shown in the tables above. So, the analysis of the results shows that we are successful in achieving power and area reduction in the redesigned structures with the use of the concept of multibit flip flop. ISSN: 2231-5381 [10] U. Soma Naidu , K.Venkateswarlu,” A Novel Approach POWER OPTIMIZED MULTI-BIT FLIP-FLOPS USING GATED DRIVER TREE” in International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 2, Issue 6, June 2013. Ya-Ting Shyu, Jai-Ming Lin, Chun-Po Huang, Cheng-Wu Lin, YingZu Lin, and Soon-Jyh Chang “Effective and Efficient Approach for Power Reduction by Using Multi-Bit Flip-Flops”IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS. Jhen-Hong He1, Li-Wei Huang2, Jui-Hung Hung3, Yu-Cheng Lin4, Guo-syuan Liou5,Tsai-Ming Hsieh “Clock Network Power Saving Using Multi-Bit Flip-Flops in Multiple Voltage Island Design” in Proceedings of the 2nd International Conference on Computer Science and Electronics Engineering (ICCSEE 2013). Shefali Sharma, Bipan Kaushal, “Shift register design using 2-bit flipflops” in proceedings of International Conference on “Recent Advances in Engineering and Computational Sciences” (RAECS-2014). L. Chen, A. Hung, H.-M. Chen, E. Y.-W. Tsai, S.-H. Chen, M.-H. Ku, and C.-C.Chen, “Using multi-bit flip-flop for clock power saving by Design Compiler,” in Proc. Synopsys User Group (SNUG), 2010. S.-H. Wang, Y.-Y. Liang, T.-Y. Kuo, and W.-K. Mak, “Power driven flip-flop merging and relocation,” in Proc. ISPD, pp. 107– 114, 2011. CMOS analog circuit design, Phillip E. Allen, Douglas R. Holberg, Oxford University Press. J. M. Rabaey, A. Chandrakasan, and B. Nikolic, 2003, Digital Integrated Circuits: A Design Perspective, 2nd ed. Upper Saddle River, NJ: Prentice-Hall. Y. Kretchmer, 2001, “Using multi-bit register inference to save area and power,” EE Times Asia. Ashna v r, Dr.M Jagadeeswari, “A Low Power Multi-Bit Flip-Flop Design for Counter Measure Circuit in Cryptographic Applications” in IRACST - International Journal of Computer Science and Information Technology & Security (IJCSITS), ISSN: 2249-9555 Vol. 3, No.2, April 2013. http://www.ijettjournal.org Page 343