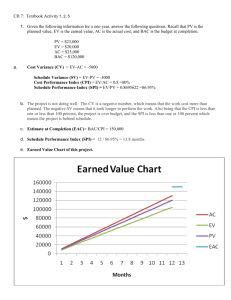

AD9364 Register Map Reference Manual UG-672

advertisement