1 Below is the logic for the flip flop. Note... E

advertisement

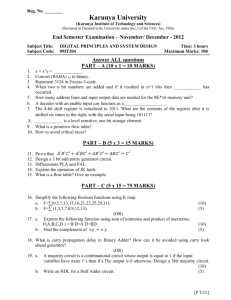

1 ECE 433: JK Flip-Flop Design Abstract—This report describes the process, from start to finish, of building a JK flip-flop. It includes the digital logic associated with the flip flop and the physical implementation as well. Also included are some simulation results of the design itself including rise and fall times varying with load capacitances. T Below is the logic for the flip flop. Note that for this truth table, E = 1, S = 0, and R = 0. J K Q Qnext I. INTRODUCTION he JK flip flop is an essential building block of digital logic. It is a device that can store a single piece of information known as a bit. The JK flip flop was chosen for this project because it is a more versatile flip flop when compared to the D- and T-types. Both the D- and T-type flip flops can be simulated by the JK flip flop by simple manipulation of the inputs J and K. For example, if one ties together the J and K inputs, a T flip flop will result. The flip flop in this design has several inputs: J, K, Set (S), Reset (R), Enable (E), and a Clock (CLK). The J and K inputs are used to manipulate the outputs Q and ~Q. The Set and Reset inputs are used to declare a particular output of set or reset regardless of the states of J and K. The Enable input is used to make the flip flop respond to its inputs. When Enable is logic 1, the flip flop behaves normally to its inputs, when it is logic 0, it will not respond. Logic 1 represents VDD = 5 V while logic 0 represents 0 V. The flip flop used in this design is a master-slave configuration. Each flip flop has complementary clock signals making one active while the other is not. The state of the flip flop, Q, is updated on the falling edge of the clock signal. The basic components that comprise this flip flop are inverters, nand gates, and nor gates. The design of this flip flop uses a process of 0.3 µm. The length for all transistors in this design was 0.6 µm. The width for all transistors, for simplicity, was to 3.0 µm. 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 When E = 0, the flip flop is no longer active, so that truth table is omitted. If S = 1, Qnext = 1 or if R = 1, Qnext = 1 regardless of the other inputs so those truth tables were omitted as well. The Set and Reset inputs cannot both be logic 1 simultaneously. If Set and Reset both equal logic 1, then output states are undetermined. The truth tables for the individual components of the flip flop are below. Inverter gate: Three-Input NAND gate: IN OUT A B C OUT 0 1 0 0 0 1 1 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 II. LOGIC The flip flop’s logic table was manipulated to include a set, reset, and enable option. Karnaugh maps were used to minimize the number of gates to include these options. The set and reset inputs basically override the J and K inputs. The enable input basically enabled the clock signal to pass through to the flip flop for it to operate correctly, hence enable. Two-Input NAND gate: Two-Input NOR gate: A B OUT A B OUT 0 0 1 0 0 1 0 1 1 0 1 0 1 0 1 1 0 0 1 1 0 1 1 0 2 III. SCHEMATICS & LAYOUT Twenty-one gates, in total, were used in this design of a JK flip flop. There were 8 inverters, 2 nor gates, 9 two-input nand gates, and 2 three-input nand gates. Since there are several schematics associated with the components and the flip flop itself, they have been appended to the end of this report. See Appendix A for the screen captures of the schematics used for the JK flip flop and of each of the components. The layouts for the individual components have been omitted from this report. For a screenshot of the layout for the entire flip flop, see Appendix B. The padframe including the pin names can also be found in Appendix B. IV. SIMULATION The output waveforms along with the test schematic for the flip flop can be found in Appendix C. The waveform matches the expected truth table for a general JK flip flop. The flip flop was simulated with the software used to create it. Three different graphs were generated with the results. Rise time, fall time, and total delay were plotted against a load capacitance from 1 pF to 5 pF. The results seem reasonable considering the times increased as load capacitance increased. The waveforms illustrating the rise and fall times can be found in Appendix D. Below are the graphs showing the collected data. V. CONCLUSION After many hours of design and troubleshooting, the JK flip flop worked correctly. It was interesting to experience the basic process of building a microchip from beginning to end (with the exception of the fabrication). 3 VI. APPENDICES (A – D) Appendix A: JK Flip Flop Schematic: Inverter Gate Schematic: Three-input NAND Gate Schematic: 4 Two-input NOR Gate Schematic: Appendix B: JK Flip Flop Layout: Two-input NAND Gate Schematic: 5 Padframe with Pin Labels (top side is this design): Appendix C: Test Schematic for JK Flip Flop: 6 Waveform of Output of JK Flip Flop: 7 Appendix D: Rise Time Waveform (increasing load capacitance): Fall Time Waveform (increasing load capacitance):