I. Objective:

advertisement

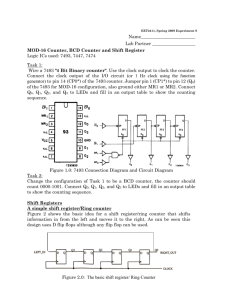

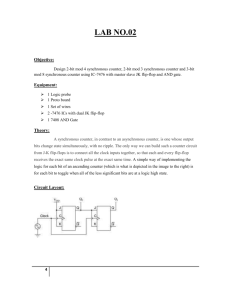

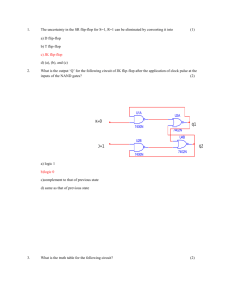

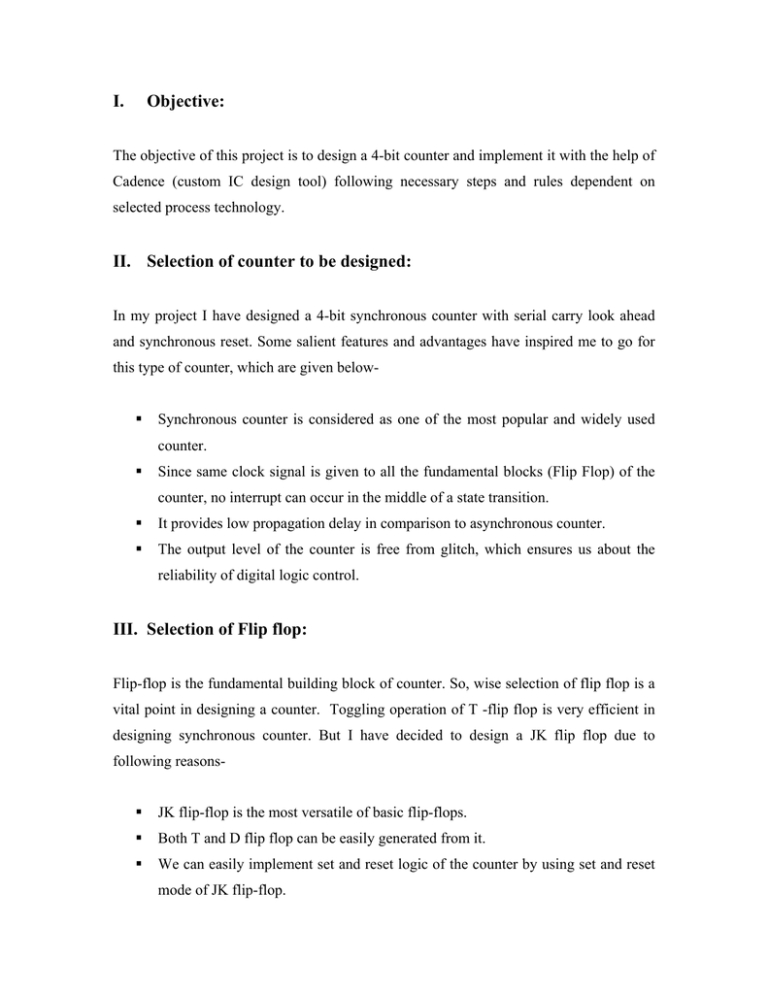

I. Objective: The objective of this project is to design a 4-bit counter and implement it with the help of Cadence (custom IC design tool) following necessary steps and rules dependent on selected process technology. II. Selection of counter to be designed: In my project I have designed a 4-bit synchronous counter with serial carry look ahead and synchronous reset. Some salient features and advantages have inspired me to go for this type of counter, which are given belowSynchronous counter is considered as one of the most popular and widely used counter. Since same clock signal is given to all the fundamental blocks (Flip Flop) of the counter, no interrupt can occur in the middle of a state transition. It provides low propagation delay in comparison to asynchronous counter. The output level of the counter is free from glitch, which ensures us about the reliability of digital logic control. III. Selection of Flip flop: Flip-flop is the fundamental building block of counter. So, wise selection of flip flop is a vital point in designing a counter. Toggling operation of T -flip flop is very efficient in designing synchronous counter. But I have decided to design a JK flip flop due to following reasonsJK flip-flop is the most versatile of basic flip-flops. Both T and D flip flop can be easily generated from it. We can easily implement set and reset logic of the counter by using set and reset mode of JK flip-flop. IV. Design Steps: Cadence is one of the most popular, efficient and commercial custom IC design tool. There are some sequential steps that we have to follow strictly for fruitful IC design. These steps are mentioned belowDesign Specification Schematic Capture Create Symbol Simulation Layout DRC- Design rule Check Extraction LVS - Layout vs Schematic Check Post layout Simulation Figure 1: Flowchart of design steps 2 V. JK Filp Flop: Master salve edge triggered flip flop is more preferable in IC design due to its reliable output. The characteristics table of JK flip-flop is: Table 1: Truth table of JK flip flop J K Qn+1 0 0 Qn 0 1 0 1 0 1 1 1 Qn’ Schematic: Figure 2: Schematic diagram of JK flip flop Master-slave cross couple NAND gate method is used in designing negative edge triggered JK flip flop. The status of output stage (Q and Q’) depends on the latched data of master stage just before the negative going edge of the clock signal. Before the next negative edge of the clock, the input of J and K has no effect on the output stage. This reduces the effect of noise signal. 3 AMI-0.6 micron process is used in drawing the schematic of all basic gates like inverter, AND, OR and NAND. Same W/L ratio (3/0.6) is used for both pmos and nmos. This selection has made little bit variation between rise time and fall time. But this variation is negligible in case of digital circuit in comparison to the effect produced by load capacitance. To implement synchronous reset logic 1 AND gate, 1 OR gate and 1 inverter are used at the beginning of the circuit. When the reset pin will be high, it will force the flip flop to go to reset mode. Symbol: The customized symbol of the JK flip flop is given below: Figure 3: Symbol of JK flip flop with synchronous reset Layout: Figure 4: Layout of JK flip flop 4 VI. 4 Bit Synchronous Counter: The truth table for 4 bit up counter is: Table 2: Truth table of 4 bit synchronous up counter. States Count D C B A 0 0 0 0 0 0 0 0 1 1 0 0 1 0 2 0 0 1 1 3 0 1 0 0 4 0 1 0 1 5 0 1 1 0 6 0 1 1 1 7 1 0 0 0 8 1 0 0 1 9 1 0 1 0 10 1 0 1 1 11 1 1 0 0 12 1 1 0 1 13 1 1 1 0 14 1 1 1 1 15 According to the truth table, it can be noted that A must change state with every input clock pulse. This can be easily implemented by using a T flip-flop. But even with JK flipflops, all we need to do here is to connect both the J and K inputs of this flip-flop to logic 1 in order to get the correct activity. B must change state only when output A is a logic 1, 5 but not when A is a logic 0. So, if we connect output A to the J and K inputs of flip-flop B, we will see output B behaving correctly. Again, C must change state only when both A and B are logic 1. We can't use only output B as the control for flip-flop C; that will allow C to change state when the counter is in state 2, causing it to switch directly from a count of 2 to a count of 7, and again from a count of 10 to a count of 15 — not a good way to count. Therefore we will need a two-input AND gate at the inputs to flip-flop C. The state of D will change only when the logic level of A, B and C are high. So we can use same method for D flip flop. An additional pin for serial carry look ahead is implemented for cascading purpose. Sometimes we may need to construct a 8bit synchronous counter by using two 4 bit counter. Then we will need the serial carry bit generated from previous counter. Schematic: Figure 5: Schematic diagram of 4 bit synchronous counter 6 Simulated waveform from schematic at 200MHz clock frequency: Figure 6: Simulated wave shape from schematic Layout: The layout of the counter has been tried to make as small as possible using few interconnection. Four flip flops are placed at four corners and 3 and gates are placed in the middle. I have used up to metal2 layer for interconnection. The layout would have been more compact if I would use metal3 layer. The final size of the layout is 114.45 µm by 83 µm, which can be considered as a usual size of a 4bit counter. 7 Figure 7: Cadence layout of 4 bit counter Extracted Layout: Figure 8: Extracted layout of 4 bit counter 8 Simulated waveform from extracted layout at 1MHz clock frequency: Figure 9: Waveform of counter at 1 MHz clock. Simulated waveform from extracted layout at 1MHz clock frequency with Reset: Figure 10: Waveform of counter at 1 MHz clock with reset operation. 9 VII. Some Extreme Cases: Simulated waveform from extracted layout at 200MHz clock frequency: Figure 11: Waveform of counter at 200 MHz clock Simulated waveform from extracted layout at 10MHz clock frequency with 4pF load: Figure 12: Waveform of counter at 10 MHz clock with 4pf load capacitance 10 VIII. Measurement of Rise Time, Fall Time and Propagation Delay: 30%~70% method is used to measure the rise time and fall time. On the other hand 50%~50% method is used in case of measuring propagation delay. At first these parameters are measured with out load, which represent the effect of parasitic capacitance. Afterward, same capacitive load is applied to the output node of each flip flop to analyze the loading effect. Measured data at different clock frequencies: Table 3: Rise time, fall time and delay at different output nodes. Rise Time (ps) fclock (MHz) A B C Fall Time (ps) D A B C Delay (ps) D A B C D 1 329.41 221.22 190.29 197.69 220.72 157.27 133.91 136.95 631.71 522.66 489.98 495.63 10 323.83 217.49 189.45 196.48 217.96 155.65 132.94 134.57 628.58 522.96 489.23 495.61 50 329.48 218.41 189.13 195.65 225.56 155.08 132.89 134.21 631.74 522.64 489.97 495.29 100 324.49 218.44 189.33 195.67 218.83 154.93 133.04 134.73 628.55 523.03 488.86 495.68 Measured data at different capacitive loads with 10MHz clock frequency: Table 4: Rise time, fall time and delay at different output nodes in loaded condition.. Rise Time (ns) Fall Time (ns) Delay (ns) Cload (pF) A B C D A B C D A B C D 1 3.16 3.06 3.03 3.05 3.42 3.34 3.32 3.31 4.84 4.7 4.69 4.72 2 5.85 5.72 5.73 5.75 6.57 6.46 6.51 6.51 8.92 8.79 8.76 8.77 3 8.53 8.41 8.37 8.42 9.76 9.69 9.68 9.67 12.95 12.81 12.81 12.83 4 11.21 11.06 11.03 11.02 12.95 12.88 12.86 12.86 16.97 16.83 16.81 16.85 Above tables show the loading effect on the output node of the counter. There is negligible variation in rise time, fall time and propagation delay, if we increase the clock 11 frequency at no load condition. But there is almost linear increment of these values with the increase of capacitive load. Following figures show the variation of rise time, fall time and propagation delay with frequency at no load condition: Rise Time without Load 350 300 A Time (ps) 250 B 200 C 150 D 100 50 0 1 10 50 100 Clock Frequency (MHz) Figure 13: Variation of rise time with frequency Fall Time without Load 250 Time (ps) 200 A 150 B C 100 D 50 0 1 10 50 100 Clock Frequency (MHz) Figure 14: Variation of fall time with frequency 12 Propagation Delay without Load 700 600 Time (ps) 500 A 400 B 300 C D 200 100 0 1 10 50 100 Clock Frequency (MHz) Figure 15: Variation of propagation delay with frequency Following figures show the variation of rise time, fall time and propagation delay with load capacitance at 10MHz clock frequency: Rise Time with Load 12 Time (ns) 10 8 A B 6 C 4 D 2 0 1 2 3 4 Load Capacitance (pF) Figure 16: Variation of rise time with load capacitance. 13 Fall Time without Load 14 12 Time (ns) 10 A 8 B 6 C D 4 2 0 1 2 3 4 Load Capacitance (pF) Figure 17: Variation of fall time with load capacitance. Propagation Delay with Load 18 16 Time (ns) 14 12 A 10 B 8 C 6 D 4 2 0 1 2 3 4 Load Capacitance (pF) Figure 18: Variation of propagation delay with load capacitance. Though there are slight variations in rise time fall time and propagation delay among four output nodes, they show exactly same behavior at loaded condition. So, parasitic capacitance has negligible effect in comparison to load capacitance. 14 IX. Application: Counter can be considered as a heart of different digital and analog circuit. There are vast applications of counter in the field of electronics. Only few of them are mentioned belowSome times we need different clock frequencies for the operation of different parts of a large circuit. In that case counter can be efficiently used as a frequency divider. From a 4 bit synchronous counter we can get four different frequencies with a multiple of two. Digital counter acts as a key part in the implementation of time dependent digital logic control circuit. Coffee vending machine, microwave oven etc.- are some very good example of such kind of circuits 15