AN-1220 APPLICATION NOTE

advertisement

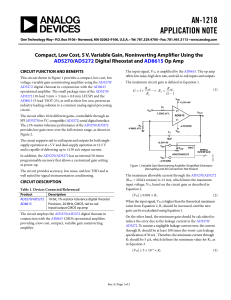

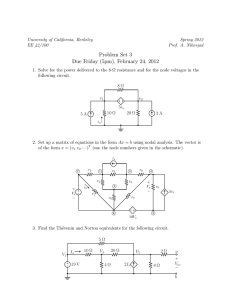

AN-1220 APPLICATION NOTE One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Compact, Low Cost, 5 V, Variable Gain, Inverting Amplifier Using the AD5270/AD5272 Digital Rheostat and AD8615 Op Amp CIRCUIT FUNCTION AND BENEFITS VDD +2.5V/+5V R3 3.32kΩ ±1% This circuit shown in Figure 1 provides a compact, low cost, low voltage, variable gain inverting amplifier using the AD5270/ AD5272 digital rheostat in conjunction with the AD8615 operational amplifier. The small package sizes of the AD5270/ AD5272 (10-lead 3 mm × 3 mm × 0.8 mm LFCSP) and the AD8615 (5-lead TSOT-23), as well as their low cost, present an industry leading solution to a common analog signal processing circuit. V+ AD8615 AD8615 VIN R2 4.99kΩ ±1% In addition, the AD5270/AD5272 has an internal 50-times programmable memory that allows a customized gain setting at power-up. The circuit provides accuracy, low noise, and low THD and is well suited for signal instrumentation conditioning. CIRCUIT DESCRIPTION Table 1. Devices Connected/Referenced Product AD5270/AD5272 AD8615 Description 10-bit, 1% resistor tolerance digital rheostat Precision, 20 MHz, CMOS, rail-to-rail input/output CMOS op amp The circuit employs the AD5270/AD5272 digital rheostat in conjunction with the AD8615 CMOS operational amplifier, providing a low cost, variable gain inverting amplifier. 10pF RAW 20kΩ AD5270/AD5272 VSS –2.5V/GND SERIAL INTERFACE 09138-001 VDD Figure 1. Variable Gain Inverting Amplifier (Simplified Schematic: Decoupling and All Connections Not Shown) The maximum allowable current through the AD5270/AD5272 (RAW = 20 kΩ version) is ±3 mA, which limits the maximum input voltage, VIN, based on the circuit gain as described in Equation 2. |VIN| ≤ 0.003 × R2 (2) When the input signal, VIN, is higher than the theoretical maximum value from Equation 2, increase R2, and the new gain can be recalculated using Equation 1. On the other hand, calculate the minimum gain to reduce the error due to the leakage current in the AD5270/AD5272. To assume a negligible leakage current error, the current through R2 must be at least 100 times the worst-case leakage specification of 50 nA. Therefore, the minimum current through R2 must be 5 µA, which defines the minimum value for R2, as in Equation 3. |VIN| ≥ 5 × 10−6 × R2 The maximum circuit gain is defined in Equation 1. RAW R → R2 = AW R2 G VSS +2.5V/+5V The input signal, VIN, is amplified by the AD8615, which is connected to the inverting mode. The op amp offers low noise, high slew rate, and rail-to-rail inputs and outputs. G =– –2.5V/GND C1 The circuit offers 1024 different gains, controllable through an SPI (AD5270) or I2C-compatible (AD5272) serial digital interface. The ±1% resistor tolerance performance of the AD5270/AD5272 provides low gain error over the full resistor range, as shown in Figure 2. The circuit supports rail-to-rail inputs and outputs for both singlesupply operation at +5 V and dual-supply operation at ±2.5 V and is capable of delivering up to ±150 mA output current. VOUT V– (1) Rev. A | Page 1 of 3 (3) AN-1220 Application Note When the circuit input is an ac signal, the parasitic capacitances of the digital potentiometer can cause undesirable oscillation in the output. This can be avoided, however, by connecting a small capacitor, C1, between the inverter input and its output. A value of 10 pF was used for the gain and phase plots shown in Figure 4. 10k 10 100 210 GAIN, RAW = 20kΩ 0 200 10 GAIN, RAW = 10kΩ 1 R2 MIN 0.1 100 1k 09138-002 10 PHASE, RAW = 10kΩ 600 (4) R2 where D is the code loaded in the digital potentiometer. 3 2 2 0 –1 –1 ERROR (%) 0 –3 –3 –4 200 400 600 800 CODE (Decimal) –4 1023 140 200k The AD5270/AD5272 have a 50-times programmable memory, which allows presetting the output voltage in a specific value at power-up. The AD5271/AD5274 (8-bits with 50-times programmable powerup memory) are both ±1% tolerance digital rheostats that are suitable for this application if 10-bit resolution is not required. 09138-003 –2 100k COMMON VARIATIONS GAIN –2 10k Excellent layout, grounding, and decoupling techniques must be used to achieve the desired performance from the circuits discussed in this note (see Tutorial MT-031, Grounding Data Converters and Solving the Mystery of “AGND” and “DGND” and Tutorial MT-101, Decoupling Techniques). As a minimum, use a 4-layer PCB with one ground plane layer, one power plane layer, and two signal layers. 1 GAIN ERROR (%) 1k FREQUENCY (Hz) (1024 – D ) × RAW 1024 1 150 Figure 4. Gain and Phase vs. Frequency for the AC Input Signal (Vertical Scale Compressed to Show All Gain Curves) The circuit gain equation is 3 170 160 GAIN, RAW = 100Ω –60 The ±1% internal resistor tolerance of the AD5270/AD5272 ensures a low gain error, as shown in Figure 3. 0 180 –20 –50 Figure 2. R2 Value Range vs. Minimum Input Signal 190 PHASE, RAW = 10kΩ PHASE, RAW = 100kΩ –40 1 INPUT VOLTAGE (mV) G=– –10 –30 0.01 0.1 GAIN 220 20 R2 MAX GAIN (dBV) RESISTANCE (Ω) 1k PHASE (Degrees) 100k 09138-004 Figure 2 shows the possible R2 value range based on the input voltage to the op amp, assuming these conditions. The same basic circuit shown in Figure 1 can be adapted to operate on a 30 V supply using higher voltage devices as described in the CN-0113 Circuit Note. Figure 3. Gain and Gain Error vs. Decimal Code Rev. A | Page 2 of 3 Application Note AN-1220 LEARN MORE Data Sheets and Evaluation Boards MT-031 Tutorial, Grounding Data Converters and Solving the Mystery of "AGND" and "DGND," Analog Devices. AD5270 Data Sheet MT-032 Tutorial, Ideal Voltage Feedback (VFB) Op Amp, Analog Devices. AD5270 Evaluation Board MT-087 Tutorial, Voltage References, Analog Devices. MT-091 Tutorial, Digital Potentiometers, Analog Devices. MT-101 Tutorial, Decoupling Techniques, Analog Devices. AD5272 Data Sheet AD5272 Evaluation Board AD5271 Data Sheet AD5274 Data Sheet AD8615 Data Sheet REVISION HISTORY 4/13—Rev. 0 to Rev. A Document Title Changed from CN-0168 to AN-1220....... Universal 7/10—Revision 0: Initial Version ©2010–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09051-0-5/13(A) Rev. A | Page 3 of 3