AD8556-EVALZ/AD8556CP-EBZ User Guide UG-896

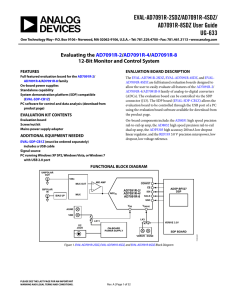

advertisement

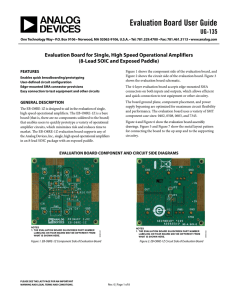

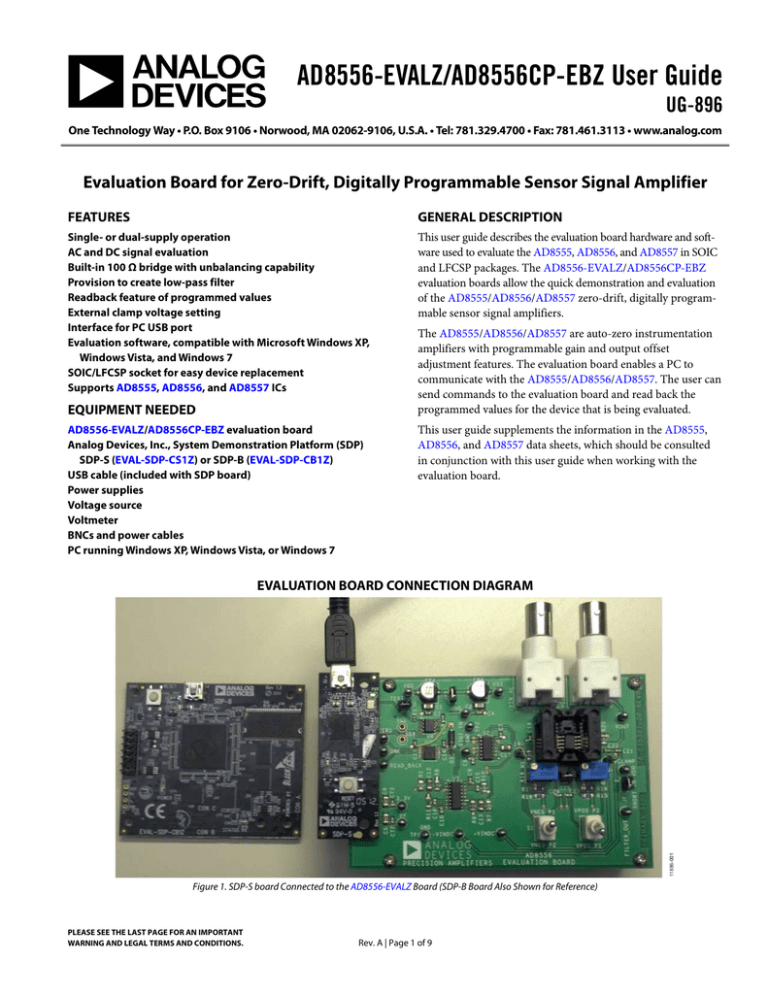

AD8556-EVALZ/AD8556CP-EBZ User Guide UG-896 One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Evaluation Board for Zero-Drift, Digitally Programmable Sensor Signal Amplifier FEATURES GENERAL DESCRIPTION Single- or dual-supply operation AC and DC signal evaluation Built-in 100 Ω bridge with unbalancing capability Provision to create low-pass filter Readback feature of programmed values External clamp voltage setting Interface for PC USB port Evaluation software, compatible with Microsoft Windows XP, Windows Vista, and Windows 7 SOIC/LFCSP socket for easy device replacement Supports AD8555, AD8556, and AD8557 ICs This user guide describes the evaluation board hardware and software used to evaluate the AD8555, AD8556, and AD8557 in SOIC and LFCSP packages. The AD8556-EVALZ/AD8556CP-EBZ evaluation boards allow the quick demonstration and evaluation of the AD8555/AD8556/AD8557 zero-drift, digitally programmable sensor signal amplifiers. EQUIPMENT NEEDED AD8556-EVALZ/AD8556CP-EBZ evaluation board Analog Devices, Inc., System Demonstration Platform (SDP) SDP-S (EVAL-SDP-CS1Z) or SDP-B (EVAL-SDP-CB1Z) USB cable (included with SDP board) Power supplies Voltage source Voltmeter BNCs and power cables PC running Windows XP, Windows Vista, or Windows 7 The AD8555/AD8556/AD8557 are auto-zero instrumentation amplifiers with programmable gain and output offset adjustment features. The evaluation board enables a PC to communicate with the AD8555/AD8556/AD8557. The user can send commands to the evaluation board and read back the programmed values for the device that is being evaluated. This user guide supplements the information in the AD8555, AD8556, and AD8557 data sheets, which should be consulted in conjunction with this user guide when working with the evaluation board. 11886-001 EVALUATION BOARD CONNECTION DIAGRAM Figure 1. SDP-S board Connected to the AD8556-EVALZ Board (SDP-B Board Also Shown for Reference) PLEASE SEE THE LAST PAGE FOR AN IMPORTANT WARNING AND LEGAL TERMS AND CONDITIONS. Rev. A | Page 1 of 9 UG-896 AD8556-EVALZ/AD8556CP-EBZ User Guide TABLE OF CONTENTS Features .............................................................................................. 1 Adjusting for 0 V Differential Input ...........................................3 Equipment Needed ........................................................................... 1 Quick Initial Hardware Setup and Output Verification ...........4 General Description ......................................................................... 1 Software ..............................................................................................5 Evaluation Board Connection Diagram ........................................ 1 Installation......................................................................................5 Revision History ............................................................................... 2 Removing the Evaluation Software .............................................5 Hardware Description ...................................................................... 3 Running the Software ...................................................................5 System Requirements ................................................................... 3 Typical AC Setup and Response ..................................................6 Communicating with the Evaluation Board............................... 3 Output Clamp Feature ..................................................................7 Hardware Requirements .............................................................. 3 Evaluation Board Schematics...........................................................8 REVISION HISTORY 11/15—Rev. 0 to Rev. A Updated Layout ................................................................... Universal Added AD8556CP-EBZ ..................................................... Universal Added Equipment Needed Section ................................................ 1 Changes to General Description Section ...................................... 1 Changes to Quick Initial Hardware Setup and Output Verification Section and Figure 2 ................................................... 4 Added Figure 12................................................................................ 8 Deleted Ordering Guide Section .................................................... 9 10/13—Revision 0: Initial Version Rev. A | Page 2 of 9 AD8556-EVALZ/AD8556CP-EBZ User Guide UG-896 HARDWARE DESCRIPTION The AD8556-EVALZ/AD8556CP-EBZ evaluation boards are designed for maximum configuration flexibility. An ac signal can be applied to +VIN ac, and the output can be monitored from VOUT ac. DC signals can be differentially applied between +VIN dc and −VIN dc, and the results can be monitored using a voltmeter at VOUT. Users can view the filter output signal at the FILT/DIGOUT pin. The board also allows swapping of the polarity of the inputs using the VNEG P1 and VPOS P1 switches. COMMUNICATING WITH THE EVALUATION BOARD Four resistors (R1A, R1B, R2A, and R2B) simulate a 100 Ω bridge configuration. The bridge can be unbalanced using the provided trim potentiometers (P1 and P2). The top and bottom of the bridge are connected to VDD and VSS, respectively. The following equipment is required: Pulse shaping is performed on this board before applying the data to the AD8556-EVALZ data input pin. The pulse widths are set for 5 μs, representing the low level (0 V), and 80 μs, representing the high level (>2.4 V). This adjustment is made using Resistor RT0 and Resistor RT1. The trim potentiometers are glued to their fixed positions. The evaluation board connects to the Analog Devices SDP-B or SDP-S board, which connects to the USB port of a PC. Ensure that the evaluation software provided on the CD is installed before connecting the SDP board and the evaluation board. HARDWARE REQUIREMENTS ADJUSTING FOR 0 V DIFFERENTIAL INPUT Prior to initial hardware setup and output verification, complete the following to adjust for differential input offset: Supply current can be monitored by using a resistor in place of R7. Clamp voltage can be applied externally to a level or can be set easily to VDD by placing a jumper from VCLAMP to VDD. The SOIC/LFCSP socket is soldered for easy programming and removal of the device. Pin 1 is the pin located in the upper lefthand corner of the socket close to R7. Make sure that the device is placed in the socket properly. See Figure 11 for the evaluation board schematic. 1. 2. SYSTEM REQUIREMENTS 7. 8. The evaluation kit has the following system requirements: Power supplies Voltage source Voltmeter BNCs and power cables SDP board with USB mini-B cable 3. 4. 5. 6. Analog Devices, Inc., SDP-B or SDP-S system demonstration platform (SDP) controller board (available for purchase separately at www.analog.com/SDP) PC with available USB 2.0 port Microsoft® Windows® operating system with administrator access Rev. A | Page 3 of 9 Connect the positive input (high) of a voltmeter to −VIN dc. Connect the negative input (low) of the voltmeter to GND of the power supply. Monitor the output (VOUT dc) voltmeter. Adjust trim Potentiometer P1 to be close to 0 V (−0.1 mV). Connect the positive input (high) of a voltmeter to +VIN dc. Connect the negative input (low) of the voltmeter to GND of the power supply. Monitor the output (VOUT dc) voltmeter. Adjust trim Potentiometer P2 to be close to 0 V (0.1 mV). UG-896 AD8556-EVALZ/AD8556CP-EBZ User Guide 4. QUICK INITIAL HARDWARE SETUP AND OUTPUT VERIFICATION For an initial hardware setup and output verification, follow these steps: 2. 3. 5. Connect the evaluation board to the SDP board, which connects to the USB port of your PC system using a USB mini-B cable. Position manual switches to VPOS P2 and VNEG P2. Jumper the VCLAMP connector pin to the VDD connector pin. When this procedure is complete, the output is 70 mV, with the board in this configuration consuming approximately 4 mA. STEP 5 APPLY +2.5V APPLY GND APPLY –2.5V VDD GND VSS AD8555/ AD8556/ AD8557 STEP 1 CONNECT SDP VOUT STEP 4 MONITOR VOUT SOIC/LFCSP VCLAMP STEP 3 CONNECT VCLAMP TO VDD AD8556 EVALUATION BOARD –VIN DC +VIN DC STEP 4 CONNECT VIN VNEG VPOS FILT OUT STEP 2 THESE SWITCHES SET INPUT POLARITY AS NEEDED Figure 2. Evaluation Board Block Diagram Rev. A | Page 4 of 9 11886-011 1. Apply 10 mV dc signal between the +VIN dc and −VIN dc connectors, and monitor the VOUT dc output using a voltmeter. Place an AD8555/AD8556/AD8557 device in the SOIC/LFCSP socket, connect the VCLAMP pin to the VDD pin, and apply dc power to the board using an external power supply (±2.5 V). AD8556-EVALZ/AD8556CP-EBZ User Guide UG-896 SOFTWARE INSTALLATION RUNNING THE SOFTWARE To install the evaluation software on the PC, To run the evaluation software application: 1. 1. 2. 3. Insert the CD-ROM into the CD drive on your PC. After a few moments, a message for the installation appears. Double-click setup.exe. (For Windows® 7 onwards, rightclick and select Install as a system administrator.) Follow the instructions until the software installation is complete. The evaluation software is developed in LabVIEW®. The software requires a LabVIEW® runtime engine and USB drivers for the SDP (both included in install). Install the software with administrator access, before plugging in the SDP board. The install detects if the SDP board has been installed previously. 2. 3. 4. The default install location is C:\Program Files (x86)\Analog Devices\AD855x. For the most current data sheet, visit www.analog.com/AD8555, www.analog.com/AD8556 or www.analog.com/AD8557. REMOVING THE EVALUATION SOFTWARE 5. 6. To remove the evaluation software modules, Go to Start > Settings > Control Panel. Double-click Add/Remove Programs and select AD855x Evaluation Software. 11886-002 1. 2. After the SDP board is plugged intothe PC via the USB cable and into the AD8556-EVALZ/AD8556CP-EBZ evaluation board via the P1 socket, run the evaluation software. From the Start menu, click AD855x Eval, and then click AD855xEVAL. The graphical user interface (GUI) opens. Select the product for which you have samples and the connector used, and then click Start. Set the appropriate gain and offset values, and then click Simulate. Monitor the output as the offset is changed to verify communication. Program the gain between 70 and 1280 and the offset between 0 V and 5 V. Click Simulate to load these values into the AD8556-EVALZ/AD8556CP-EBZ and monitor the output. The output is input × gain and responds to the specified configuration. After the AD8556-EVALZ/AD8556CP-EBZ has been simulated to the final values, click Program to permanently blow the internal fuses to the values in the GUI. Figure 3. No Programming Dialog Box Rev. A | Page 5 of 9 UG-896 AD8556-EVALZ/AD8556CP-EBZ User Guide Table 1. Evaluation Software Dialog Box Button Functions Button Start Connector Product Simulate Program Blow Parity Fuse Blow Master Fuse Read Fuse Values Function Select the connector and the product, and then click Start to begin evaluation. Selects the physical connector on the SDP board that is used to connect to the evaluation board. The connectors are labeled on the top silkscreen of the SDP board. Selects the device under evaluation. Configures the device according to the specified pattern. This button does not blow any fuses. Blows fuses according to the specified pattern. Blown fuses cannot be reprogrammed. Blows the parity fuse. The parity fuse keeps track of the state of the blown fuses. If, for any reason, the state of this fuse is changed either intentionally or unintentionally, the parity flag is set and the alarm is set. Permanently sets the device to the programmed gain and offset and prevents future programming. Click this button only after selecting and programming the gain and the offset. Prior to blowing the master fuse, make sure to first blow the parity fuse, if prompted. Reads back the state of the programmed fuses after they have been blown. The options are as follows: Low sense current: when dropped across a blown fuse (high impedance), creates a voltage that can trigger an internal comparator and provide the right level in the output. High sense current: reads back the fuse states to make sure that the fuses are blown. A code for blown fuses appears in a pop-up box. See the AD8555/AD8556/AD8557 data sheet for more information on the theory of operation; simulation, programming, and read modes; and parity error detection. The AD8555/AD8556/AD8557 data sheet also contains more information on programming procedures for the device. Figure 4 shows the output on Channel 2 under these conditions and configuration. [ ] T T TYPICAL AC SETUP AND RESPONSE 1 AC Input Example Setup requirements are as follows: Power supplies Function generator Scope BNCs and cables 2 Results Ch1 50.0mV When the device is powered with ±2.5 V, and 50 mV of input is applied, the default conditions are BW Ch2 2.00V BW M 400ms A Ch1 2.00mV T 9.600% 11886-003 Figure 4. Output on Channel 2 Figure 5 shows the results of the previous conditions with VOFF = 2.5 V or Code 128. VCC = 2.5 V VSS = −2.5 V Gain 1 = 4 Gain 2 = 17.5 Offset = VSS [ ] T T 1 The overall gain is 70. When the switches are placed in VNEG P1 and VPOS P2, there is one set of outputs. When the switches are changed to VNEG P2 and VPOS P1, the exact voltage is produced, but with the opposite polarity. 2 RT0 and RT1 are the trim potentiometers used for pulse width shaping. Do not change their settings. RT0 is adjusted to create a 5 μs pulse; RT1 is adjusted to create an 80 μs pulse. Rev. A | Page 6 of 9 Ch1 50.0mV BW Ch2 2.00V BW M 400ms A Ch1 2.00mV T 9.600% Figure 5. Output on Channel 2, VOFF = 2.5 V 11886-004 When both switches are on one side (for example, VNEG P1 and VPOS P1), the inputs are shorted together. AD8556-EVALZ/AD8556CP-EBZ User Guide UG-896 [ In Figure 6, overall gain = 100 (G1 = default = 4, G2 = Code 1 = 25, offset = 2.5 V or Code 128). [ ] T T ] T T 1 1 2 Ch1 20.0mV BW Ch2 2.00V BW M T BW Ch2 2.00V BW M 400ms A Ch1 2.00mV T 9.600% Figure 9 shows the output after VCLAMP is set to 0.8 V. Figure 6. Output with Overall Gain = 100 [ ] T ] T T In Figure 7, VIN = 2 mV p-p, G1 = 6.4, G2 = 35, and offset = 2.5 V or Code 128. [ 2.00mV 0.00000s Figure 8. Normal Response 11886-005 Ch1 50.0mV 100ms A Ch1 11886-007 2 1 T 1 2 Ch1 20.0mV BW Ch2 2.00V BW M T 100ms A Ch1 2.00mV 0.00000s 11886-008 2 Figure 9. Response with VCLAMP Set BW Ch2 2.00V BW M 400ms A Ch1 T 9.600% –1.20mV Applying a large gain to an input yields saturation, as shown in Figure 10. The conditions are VIN = 20 mV p-p, G1 = 6.4, G2 = 200, offset = 2.5 V. 11886-006 Ch1 20.0mV Figure 7. Output at VIN = 2 mV p-p, G1 = 6.4, G2 = 35, Offset = 2.5 V [ OUTPUT CLAMP FEATURE ] T T The output of the device can be clamped to the desired level. The output clamp feature is provided to protect the circuitry that follows the AD8556-EVALZ, in case the input to AD8556EVALZ is accidentally larger than anticipated. 1 In normal situations (VSUPPLIES = ±2.5 V, gain = 70, VOFFSET = 2.5 V, input = 40 mV p-p), the response to an input is as shown in Figure 8. Ch1 20.0mV BW Ch2 2.00V BW M 400ms A Ch1 T 9.600% –1.20mV 11886-009 2 Figure 10. Results with Saturation Note that Resistor RT1 and Resistor RT2 are used for pulse stretching; do not adjust them. They are factory-adjusted for optimal results. Rev. A | Page 7 of 9 UG-896 AD8556-EVALZ/AD8556CP-EBZ User Guide EVALUATION BOARD SCHEMATICS EEPROM ID VSS C4 0.1UF AGND R5 R3 100K 100K 1 2 3 6 7 EEPROM_A0 C10 0.1UF SCL_0 AGND R2 AGND 3.3V/20MA E0 E1 5 SDA_0 SDA E2 SCL WC_N VSS 4 M24C02-WMN6TP 0 DNI VSS BLK C2 10UF 100K AGND AGND 0.1UF U4 8 VCC VSS R6 GND GND 8 SN74LV123AD 0 DNI 2 C9 0.1UF GND 7 SN74LV132AD AGND VSS C18 VIO_+3.3V VDD U1 16 VCC U2 14 VCC R4 C7 0.1UF C8 1 VDD VDD C3 0.1UF C1 10UF 0.1UF VDD BLK GND BLK FIT IN 2.75X4.25 2 LAYER BOARD DELETE NC PIN CONNECTIONS P1 FX8-120S-SV(21) 2K R10 JP1 4 DUT VCLAMP VDD AGND 3 A2 Y2 12 GPIO2 4 A3 Y3 11 C21 0 FILT OUT 8 11 1UF 13 10 SN74LV132AD 2 2K 2 C22 200 R16 1 3 P2 3 200 2 AMP227161-1 0.1UF R17 2K R14 S2 VPOS P1 3 9 C17 R21 EONE 12 P2 R13 2 S1 VNEG P1 CW 1 GPIO1 EZERO U2 U2 +VINDC BLK CHWT123M1D9AV2Q TP7 BLK TP6 BLK AGND Y1 13 2 A1 J1 1 2 1 3 GPIO0 VDD CHWT123M1D9AV2Q U3 1 14 VCCAVCCY TP3 BLK 12 CLR_N 11 USB_VBUS TP1 BLK TP2 BLK OTS-8-16-1.27-03 VDD SN74LV123AD VIO_+3.3V AGND VSS -VINDC BLK 5 0.1UF C AMP227161-1 AGND 1 Q_N 6 VSS VSS SN74LV132AD Y4 10 GND 7 2K R18 EN 2K 5 A4 8 R15 SDA_0 SCL_0 GPIO1 Q R/C J2 8 7 DUT OUT 6 DUT VCLAMP DUT IN+ 5 R19 7 1 2 3 4 FILT OUT DUT DIN DUT IN- 1 1UF AGND X1 FILTER_OUT BLK SN74LV132AD U1 9 A 10 B CW 1 5K 2 R12 R7 EONE SIG_ONE VOUT BLK 10K DUT DIN 3 C20 C19 VDD VSS R20 U2 SIG_ZERO 1 SN74LV123AD C13 VCLAMP BLK CLR_N 3 0.1UF C VDD 0.1UF 30K C15 R8 1000PF Q_N 14 VSS 13 VSS ADG3304BRUZ AGND U2 TP5 BLK 4 SIG_ZERO 5 SIG_ONE 6 FX8-120S-SV(21) SN74LV132AD 11886-012 EEPROM_A0 Q R/C D1 1N5817 GPIO0 GPIO2 VDD 15 1000PF C73 0.1UF 1UF C14 0.1UF C5 10UF 5K R11 C6 10UF U1 1 A 2 B C12 R1 EZERO 49.9K VIO_+3.3V C72 0.1UF VIO_+3.3V R9 30K USB_VBUS TP10 BLK C11 0.1UF USB_VBUS VDD 120 119 118 117 116 115 114 113 112 111 110 109 108 107 106 105 104 103 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 C16 P1 TP4 BLK AGND Figure 11. AD8556CP-EBZ Evaluation Board Schematic VDD BLK EEPROM ID GND JP2 VSS=GND C8 AGND AGND 0.1UF GND 8 SN74LV123AD AGND VIO_+3.3V SCL BLK VSS EEPROM_A0 C10 0.1UF SCL_0 AGND N VSS 3.3V/20MA U4 8 VCC SDA BLK 1 E0 2 5 E1 SDA 3 SDA_0 E2 6 SCL 7 WC_N VSS 4 M24C64-WMN6TP FIT IN 2.75X4.25 2 LAYER BOARD C4 0.1UF JP3 USB_VBUS VDD P C23 100UF R2 AGND VSS BLK DELETE NC PIN CONNECTIONS P1 FILT OUT VDD 3 DUT DIN DUT DIN JP1 10K R20 C21 IN+ VDD GPIO1 3 A2 Y2 12 EONE GPIO2 4 A3 Y3 11 C17 FILT OUT 8 11 BLK 1UF 10 13 200 2 J1 5227161-1 VPOS P2 C22 10K R17 10K R14 2 +VINDC BLK ET03MD1CBE EZERO S2 P1 3 Y1 13 P2 R16 2 A1 VNEG CW 1 GPIO0 9 12 200 AGND 3 P1 U2 U2 U3 1 14 VCCA VCCY R13 C14 0.1UF S1 BLK READ_BACK -VINDC BLK BLK R19 CLR_N 11 USB_VBUS ONE DUT IN+ 1 12 CW 1 SDA_0 SCL_0 GPIO1 C 5 VDD SN74LV123AD ZERO BLK AGND Q_N 6 VSS VIO_+3.3V DUT INQ R/C BLK 7 1 9 A 10 B 1UF R12 C13 VSS AGND 16QN65K14040 0.1UF SN74LV132AD 2 5K 5227161-1 IN- R7 DUT VCLAMP 2 U1 EONE J2 12 DUT OUT 11 10 DUT VCLAMP 9 5 6 7 8 PAD SIG_ONE VOUT BLK X1 1 2 3 4 VCLAMP BLK VSS 0.1UF SN74LV123AD AGND FILTER_OUT BLK SIG_ZERO 1 VSS VDD VDD 0.1UF C26 U2 VDD AGND FILTER 1000PF R8 30K C15 VSS 4 CLR_N 3 C29 10UF AGND 16 15 14 13 R10 2K C SN74LV132AD 10K R18 1000PF C27 21 Y4 10 GND 7 10K EN R15 8 1000PF C24 1 2 SN74LV132AD 5 A4 VSS ADG3304BRUZ AGND U2 DIGI_IN BLK 4 SIG_ZERO 5 SIG_ONE 6 FX8-120S-SV(21) FX8-120S-SV(21) TP1 BLK Q_N 14 0.1UF AGND SN74LV132AD 11886-013 EEPROM_A0 R/C AGND 13 C20 0.1UF 10UF Q ET03MD1CBE 1 3 GPIO0 GPIO2 15 D1 1N5817 C73 0.1UF 1UF 100K C6 10UF 5K C19 C28 U1 1 A 2 B C12 R1 EZERO 1000PF C5 10UF VIO_+3.3V C72 0.1UF VIO_+3.3V R11 USB_VBUS VDD 3.3V BLK C16 USB_VBUS 120 119 118 117 116 115 114 113 112 111 110 109 108 107 106 105 104 103 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 R9 30K P1 5V BLK C11 0.1UF C2 10UF C9 0.1UF GND 7 SN74LV132AD AGND VSS C18 VDD U1 16 VCC U2 14 VCC 0.1UF P C25 2 C7 0.1UF C3 0.1UF 100UF N 1 C1 10UF 100K VDD VDD GND BLK TP2 BLK AGND Figure 12. AD8556-EVALZ Evaluation Board Schematic Rev. A | Page 8 of 9 AD8556-EVALZ/AD8556CP-EBZ User Guide UG-896 NOTES ESD Caution ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality. Legal Terms and Conditions By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed. ©2013–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG11886-0-11/15(A) Rev. A | Page 9 of 9