AN-1381 APPLICATION NOTE

advertisement

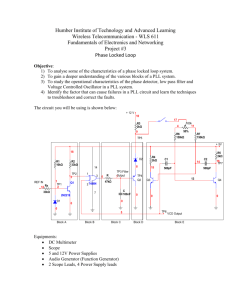

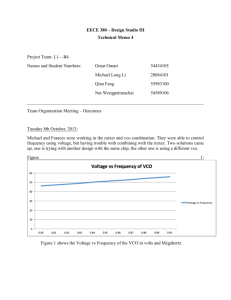

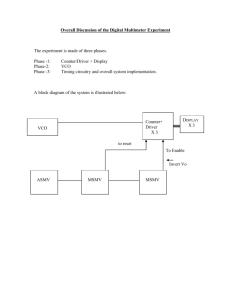

AN-1381 APPLICATION NOTE One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com How to Bypass VCO Calibration for the ADF4355-2 By Robert Brennan 7. VCO CALIBRATION Repeat Step 1 through Step 6 to build a lookup table for all desired frequencies. For Step 1, writing R10, R7, R2, R1, and R0 is only required after the first iteration. R2 and R1 are optional if they have not changed. Bypass VCO Calibration for Faster Lock Times For any given output frequency, the ADF4355-2 uses a certain voltage controlled oscillator (VCO) core, band, and bias code. These three settings are selected automatically during the VCO automatic calibration (AUTOCAL). The settings are read from the ADF4355-2 and stored in a lookup table. Using this lookup table to bypass the AUTOCAL routine dramatically decreases the total lock time when changing the frequency. For example, lock times of less than 30 µs are possible with a 59.7 kHz loop bandwidth. Figure 1 shows an example of a suitable loop filter. R2 5.1kΩ CP C1 220pF R1 2.4kΩ C2 3.3nF CORE AND BAND (R10 DB[28:26] = 1): LE CLK MUXOUT X X 1 0 0 CORE = A VTUNE 0 1 0 0 0 1 BAND = 70 VALUE CORE 001 010 011 100 D C B A 1 0 BIAS CODE (R10 DB[28:26] = 3): C3 100pF LE fPFD = 61.44MHz PM = 46.5° ICP = 0.9mA MUXOUT X Figure 1. Example Loop Filter with a 59.7 kHz Loop Bandwidth VCO Readback Procedure 3. 4. 5. 6. X X X X X X 0 1 1 0 BIAS CODE = 6 Figure 2. VCO Readback The VCO readback procedure is as follows: 2. X NOTES 1. X = DON’T CARE. 2. MUXOUT MUST BE SET TO VCO READBACK (R4, DB[29:27] = 7). 3. VCO READBACK MUST BE SET TO VCO READBACK (R7, DB[14:12] = 7). 4. DATA IS CLOCKED OUT ON THE POSITIVE EDGE OF CLK AND READ ON THE NEGATIVE EDGE OF CLK. READBACK STARTS ON THE FIRST CLK EDGE AFTER LE GOES HIGH. LE MUST STAY HIGH DURING A READ. Because each ADF4355-2 chip is unique, a new lookup table must be generated for every chip. 1. X 13647-002 kVCO = 15MHz/V LBW = 59.7kHz 13647-001 CLK Load all registers to lock to the desired frequency. a. Ensure VCO read is set to VCO core and band (R10, DB[28:26] = 0b001) (see Figure 5). b. Ensure VCO readback is set to VCO calibration complete (R7, DB[14:12] = 0b110) (see Figure 4). c. Ensure MUXOUT is set to VCO readback (R4, DB[29:27] = 0b111) (see Figure 3). d. Ensure AUTOCAL is enabled (R0, DB21 = 0b1); see the ADF4355-2 data sheet for the R0 register map. Wait until MUXOUT outputs a logic high (VCO calibration complete). Load R7 with VCO readback set to VCO readback (R7, DB[14:12] = 0b111). Pulse SPI CLK while LE is kept high. The data outputs on MUXOUT. Extract the data as shown in Figure 2. Load R10 with VCO read set to VCO bias code (R10, DB[28:26] = 0b011). Repeat Step 4 for bias data. Bypass Automatic Calibration (AUTOCAL) to Manually Select VCO and Lock If the required VCO core, band, and bias code for a desired frequency is known (for example, in a lookup table), bypass the VCO calibration routine and set the VCO data manually with the following steps: 1. 2. 3. 4. 5. 6. Rev. 0 | Page 1 of 4 Load R0 with AUTOCAL disabled (R0, DB21 = 0b0). This step is optional if AUTOCAL is already disabled. Load R10 with VCO write set to VCO core and band (R10, DB[31:29] = 0b001). Load R11 with the desired VCO core, VCO band, and VCO bias setting as defined in Figure 6. Note that the VCO core bits are different for read and write. Load R10 with VCO write set to VCO bias code (R10, DB[31:29] = 0b011). Reload R11 with the same value as in Step 3. Lock to the desired frequency by programming R2, R1, and R0, respectively. AN-1381 Application Note COUNTER RESET CP THREESTATE DBR 1 PD MUX LOGIC CURRENT SETTING PD POLARITY DBR 1 10-BIT R COUNTER REF MODE DBR 1 DOUBLE BUFF MUXOUT RESERVED RDIV2 REFERENCE DOUBLER DBR 1 Expanded ADF4355-2 Register Maps DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 0 M3 M2 M1 RD2 RD1 R10 RD2 REFERENCE DOUBLER 0 DISABLED 1 ENABLED R9 R8 R7 R6 R5 R4 R3 R2 R1 D1 CP4 CP3 DISABLED 0 DISABLED ENABLED 1 DIFF 1 CP1 ICP (mA) 5.1kΩ ENABLED 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0.3 0.6 0.9 1.2 1.5 1.8 2.1 2.4 2.7 3.0 3.3 3.6 3.9 4.2 4.5 4.8 0 .......... 0 1 1 0 .......... 1 0 2 . . .......... . . . . . .......... . . . . . .......... . . . 1 1 .......... 0 0 1020 1 1 .......... 0 1 1021 1 1 .......... 1 0 1022 1 1 .......... 1 1 1023 M3 M2 M1 0 0 0 OUTPUT THREE-STATE OUTPUT 0 0 1 DVDD 0 1 0 0 1 1 DGND R DIVIDER OUTPUT 1 0 0 N DIVIDER OUTPUT 1 0 1 ANALOG LOCK DETECT 1 1 0 DIGITAL LOCK DETECT 1 1 1 VCO READBACK C1(0) 1 CP2 0 C4(0) C3(1) C2(0) 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 U1 COUNTER RESET CP3 R DIVIDER (R) U2 U1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 R1 U3 REFIN CP4 R2 U4 SINGLE DISABLED .......... U5 DB0 0 0 R9 U6 DB1 U6 REFERENCE DIVIDE BY 2 R10 CP1 DB2 DOUBLE BUFFERED REGISTER 6, BITS[DB23:DB21] D1 RD1 1 CP2 DB3 ENABLED U5 LDP U2 CP THREE-STATE 0 1.8V 0 DISABLED 1 3.3V 1 ENABLED U4 PD POLARITY U3 POWER DOWN 0 NEGATIVE 0 DISABLED 1 POSITIVE 1 ENABLED 13647-003 0 CONTROL BITS 1DBR = DOUBLE BUFFERED REGISTER—BUFFERED BY THE WRITE TO REGISTER 0. DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 0 0 1 0 0 LE LE 0 0 0 0 0 0 0 0 0 0 VR3 VR2 VR1 0 VR3 VR2 VR1 VCO READBACK 0 0 0 0 1 1 1 1 NORMAL OPERATION RESERVED RESERVED RESERVED RESERVED RESERVED VCO CALIBRATION COMPLETE VCO READBACK 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 LD5 LD4 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 LD2 LD1 C4(0) C3(1) C2(1) C1(1) LOL LD3 LD1 LE SYNCHRONIZATION CONTROL BITS LOCK DETECT MODE 0 FRACTIONAL-N 1 INTEGER-N (2.9ns) LD3 LD2 FRACTIONAL-N LD PRECISION 0 0 1 1 5.0ns 6.0ns 8.0ns 12.0ns 0 1 0 1 LOL LOSS OF LOCK MODE 0 DISABLED 0 DISABLED 1 LE SYNCED TO REFIN 1 ENABLED Figure 4. Register 7 Rev. 0 | Page 2 of 4 LD5 LD4 LOCK DETECT CYCLE COUNT 0 0 1024 0 1 2048 1 0 4096 1 1 8192 13647-004 0 LD MODE VCO READBACK FRAC-N LD PRECISION RESERVED LD CYCLE COUNT LOL MODE RESERVED RESERVED LE SYNC Figure 3. Register 4 VCO READ ADC CLOCK DIVIDER RESERVED DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 VW2 VR3 VW1 VR2 VR1 0 1 0 0 0 0 0 0 0 0 AD8 AD7 AD6 AD5 AD4 DB7 DB6 AD3 AD2 DB5 DB4 DB3 DB2 AE1 ADC 0 DISABLED 0 0 0 0 1 1 1 1 NORMAL OPERATION VCO CORE AND BAND RESERVED VCO BIAS CODE RESERVED RESERVED RESERVED RESERVED 1 ENABLED 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 VCO WRITE NORMAL OPERATION VCO CORE AND BAND RESERVED VCO BIAS CODE RESERVED RESERVED RESERVED RESERVED AD7 .......... AD2 0 0 .......... 0 1 1 0 0 .......... 1 0 2 . . .......... . . . . . .......... . . . . . .......... . . . 1 1 .......... 0 0 252 1 1 .......... 0 1 253 1 1 .......... 1 0 254 1 1 .......... 1 1 255 AD8 DB1 DB0 AE2 AE1 C4(1) C3(0) C2(1) C1(0) AD1 VCO READ 0 0 0 0 1 1 1 1 0 1 0 1 0 1 0 1 1 VR3 VR2 VR1 VW3 VW2 VW1 0 0 1 1 0 0 1 1 0 CONTROL BITS AE2 ADC CONVERSION 0 DISABLED 1 ENABLED AD1 ADC CLK DIV 13647-005 VW3 ADC ENABLE VCO WRITE AN-1381 ADC CONVERSION Application Note Figure 5. Register 10 VCO CORE RESERVED VCO BIAS CONTROL BITS VCO BAND DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 0 0 0 0 0 0 0 0 1 C4 C3 C2 C1 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 C4 C3 C2 C1 B4 B3 B2 B1 BA8 BA7 BA6 BA5 BA4 BA3 BA2 DB2 DB1 DB0 BA C4(1) C3(0) C2(1) C1(0) VCO CORE RESERVED CORE D/NORMAL OPERATION CORE C CORE B CORE A B4 B3 B2 B1 VCO BIAS BA8 BA7 .......... BA2 BA1 0 0 0 0 0 0 0 0 1 0 1 2 3/NORMAL OPERATION 4 5 6 7 8 0 0 . . . 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 Figure 6. Register 11 Rev. 0 | Page 3 of 4 0 0 . . . 1 1 1 1 .......... .......... .......... .......... .......... .......... .......... .......... .......... 0 0 . . . 0 0 1 1 0 0 . . . 0 1 0 1 VCO BAND 0/NORMAL OPERATION 1 . . . 252 253 254 255 13647-006 0 AN-1381 Application Note Read Timing Characteristics Table 1. Read Timing Parameter t1 t2 t3 t4 t5 Limit at TMIN to TMAX 15 15 25 25 10 Unit ns min ns min ns min ns min ns min Description LE high to CLK high CLK high to DATA ready CLK high duration CLK low duration CLK high to LE low (next write) Read Timing Diagram t1 t3 t4 CLK t2 X MUXOUT DB11 DB2 DB1 DB0 t5 13647-007 LE NOTES 1. LE MUST BE KEPT HIGH DURING READBACK. 2. X = DON’T CARE. Figure 7. Read Timing Diagram ©2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. AN13647-0-11/15(0) Rev. 0 | Page 4 of 4