Ultra low-voltage floating-gate (FGUVMOS) amplifiers

advertisement

Ultra low-voltage floating-gate (FGUVMOS) amplifiers

YNGVAR BERG, ØIVIND NÆSS, MATS E. HØVIN, AND HENNING GUNDERSEN

Department of Informatics, University of Oslo, Gaustad Alleén 23, Blindern, N-0316 Oslo, Norway

.

Abstract. This paper presents an approach to programming threshold voltages in floating-gate CMOS

circuits. The threshold voltage programming is exploited in ultra low-voltage ULV) amplifier design.

A threshold voltage programming scheme is presented and several examples of analog ULV circuits are

described. The ULV circuits are used in ULV amplifier design. Measured data are provided.

1. Introduction

10

A

-7

standard transistor

max

I ds

weak inversion model

Ids [A]

S the power supply in standard CMOS pro-9

10

cesses is lowered, the available headroom of

analog circuits is reduced. Looking into the fuexact current

-11

10

ture, ultra low supply voltage (ULV) Vdd < 1V

I bec

C1

is coming. Improved precision in production will

-13

permit a reduced threshold voltage with improved

10

Ids

Vin

matching, but still the threshold voltage will “steal”

C2

an increasing part of the available headroom.

-15

min

10

One possible solution to the matching problem

I ds

Cm

is post-fabrication tuning such as laser-trimming.

Techniques requiring individual tuning of each powered- 10 -17

0.5

0

0.3

0.4

0.1

0.2

up circuit are slow and expensive. Another apVin [V]

proach to threshold matching is to use MOS transistors with capacitive coupling to a floating gate

as indicated in Fig. 1. A change in the stored

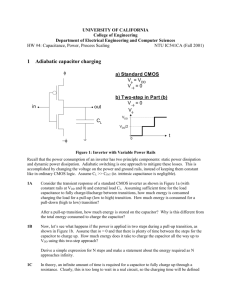

Figure 1: Multiple input n-channel Floating-gate

charge of the floating gate will effectively shift

UVMOS (FGUVMOS) transistor.

the threshold voltage seen from the capacitively

coupled input terminal. The success of this apanalog circuits are presented in section 4, and two

proach is clearly dependent on both the accuracy

examples

of ULV amplifiers are presented in secand the overhead penalty in terms of silicon area

tion

5

and

6 respectively.

and production cost. The floating-gate UV-light

programmable MOS (FGUVMOS) transistor [1]

can be used to program effective threshold volt2. FGUVMOS circuits

ages for floating-gate transistors [2]. The FGUVMOS transistor has been used to design ultra

The generic FGUVMOS circuit is shown in

low-power digital circuits [3].

Fig. 2. To ensure a direct control of the effecIn section 2 the FGUVMOS transistor and

tive threshold voltage or current level in the prothe generic FGUVMOS circuit are presented, and

gramming mode no series transistors are allowed

a programming technique controlling the floating

between supply rails and outputs. Although the

gates is presented in section 3. Ultra low-voltage

design space for a creative circuit designer seems

1

C pjm

C pi1

V pi1

C p2m

C p21

V p21

V p11

where Ibec is the programmed equilibrium point

current, that is the drain-source current of any

FGUVMOS transistor with all control inputs equal

to Vdd /2. The drain current of a multiple input ptype FGUVMOS transistor may then be written

as

V pjm

V p2m

C p11

V fgp1

C p1m

V fgpm

V p1m

V out

V n11

C n11

V n1q

V fgn1

Cl

C n1q

Ids(p−type)

V fgnq

= Ibec

V n2q

V n21

i=1

V nlq

V nk1

Figure 2: The generic FGUVMOS circuit.

rather limited with FGUVMOS circuits, it is possible to create a versatile set of circuit-elements

with familiar behavior. The central design technique is the well-known capacitive division with

the floating-gate as the divided node. Unlike traditional circuits, there is no leakage from the divided node under normal operation.

For a multiple input FGUVMOS transistor each

input has by design an effective coupling capacitance, Ci , to the floating-gate. The input signal

(control gate) is attenuated with a factor ki =

Ci /CT , where CT is the total load capacitance

seen from the gate. ki is called the capacitive division factor for input i.

It is convenient to express the behavior of a

FGUVMOS circuit as a modulation of the equilibrium condition. At the equilibrium point, the

control inputs are equal to Vdd /2 and the transistor currents are equal to Ibec . For simplicity, we

will model the weak inversion behavior knowing

that a similar analysis may be done for strong inversion as well. The input modulation of the drain

current as a function of the ith input terminal may

1

(Vi − Vdd /2)ki }. The acbe expressed as exp{ nU

t

cumulated drain current modulation

of m inputs

Qm

1

is expressed as the product i=1 exp{ nU

(Vi −

t

Vdd /2)ki }. The effective drain current of a multiple input n-type FGUVMOS transistor, see Fig.

1, may then be written as

Ids(n−type) = Ibec

m

Y

i=1

exp{

1

(Vdd /2 − Vi )ki }

nUt

assuming that the slope factor of the p-typeand n-type transistors are equal. The inverted

2

current I ∗ is equivalent to Ibec

I −1 .

Furthermore, we may express the min and max

currents of the n-type transistor in terms of the

balanced equilibrium current and current modulation

C nlq

C nk1

exp{

∗

≡ Ids(n−type)

,

C n2q

C n2l

m

Y

Imax

Imin

= Ibec exp{

1

Vdd ki }

2nUt

= Ibec RKsum

= Ibec R−Ksum

2

Ibec

=

Imax

∗

≡ Imax

,

Pm

1

Vdd } and Ksum = i=1 ki .

where R = exp{ 2nU

t

Assuming that Ksum = 1, the current range (or

noise margin) is R2 .

3. Programming FGUVMOS circuits

Several different tuning schemes are used for

controlling the charge stored on a floating gate.

Several solutions involve injection-based techniques

using high-voltage in combination with dedicated

processes. Recent results [4] indicates that floatinggate tuning may be done in standard, doublepoly CMOS. Utilizing the old technique of UVlight activated conductances, we are able to implement low-power, area-efficient analog circuits.

The threshold of FG-transistors may be tuned to

suitable values[2].

A simplified FGUVMOS tuning technique was

presented in [1, 5]. The FGUVMOS inverter is

shown in Fig. 3. In the operative mode (normal biasing) there are no resistive connections to

1

(Vi − Vdd /2)ki },

nUt

2

0.4

Vin

Vout

0.35

Vout (V) UVlight

VG pf

Cp

Cp

G pgd

V fgp

V well

0.3

0.25

V fgp

V in

Vdd /2

V out

Cn

Cl

V fgn

G pgs

G ngs

G pgb

V out

G ngb

0.2

Cl

V fgn

V psub

Cn

0.15

0

G ngd

G nf

5

10

15

time (minutes)

20

25

30

V+

a)

b)

Figure 4: Measured FGUVMOS inverter output while

exposed to UV-light and reverse biased for 0.8µ double

poly AMS CMOS process. The supply voltage is 0.5V.

A 4W disassembled UV-eraser was used for tuning.

Figure 3: Single input FGUVMOS circuit. a) Operative mode (normal biasing) and b) programming mode

(reverse biasing).

supply rails, V− at Vdd and V+ at Vss .

The supply rails are used to provide the programming voltages. The effective threshold voltage seen from the control gate is

determined by the programming voltages.

The threshold voltage of the gates can be

programmed to allow “perfect” DC transfer

characteristics.

the floating-gate. In the programming mode (reverse biasing) however, the desired UV-activated

conductances Gngd and Gpgd appears. The parasitic UV-activated conductances Gngs , Gnf , Gng2 ,

Gpgs , Gpf and Gpg2 , shown in Fig. 3 b) are

determined by the layout and must considered

when designing the FGUVMOS circuits. The parasitic UV-activated conductances decrease exponentially with the distance from the UV-exposed

area [6]. The UV-windows are located at the transistor terminals (poly/diffusion edge) connected

to the supplies. When reverse biasing the inverter, that is applying a more positive voltage

on gnd compared to Vdd , the source and drain

terminals are interchanged leaving us with a low

impedance common source output. The FGUVMOS programming technique can be described

in a number steps:

4. Terminate the programming by removing the UV-light source when an (any)

output (external) converges to Vdd /2.

The time required to complete the programming is determined by the maximum capacitive load of the floating gates. All internal nodes are driven towards Vdd /2 and all

transistors and circuits are programmed simultaneously. Fig. 4 shows the FGUVMOS

inverter output in the programming mode

for 4 identical inverters on 4 different chips.

The initial floating-gate voltages may vary.

If the the outputs converge to an undesired

value (6= Vdd /2) either V− or V+ has to be

altered. Normally we use only one set of

programming voltages for a chip.

1. Decide the operative (normal biasing)

supply voltage Vdd . The optimal supply

voltage may vary among applications.

2. Apply Vdd /2 to all external inputs. The

digital gates and analog sub-circuits are programmed to get Vdd /2 at any output or internal node when all inputs are Vdd /2.

5. Set the biasing voltages to normal values. All floating-gate have been programmed

simultaneously without accessing the tran-

3. Apply the programming voltages at the

3

−6

0.7

10

Ibec=200nA

Ibec=4nA

0.6

−7

10

Ibec=2nA

0.5

Ibec=180nA

−8

10

Vout (V)

Ids (V)

0.4

−9

10

Ibec=4nA

0.3

0.2

Ibec=200nA

−10

10

0.1

−11

10

0

Vdd=0.3V

−12

10

0

0.1

0.2

0.3

0.4

0.5

0.6

−0.1

0

0.7

0.1

0.2

Vdd=0.5V

0.3

0.4

Vdd=0.7V

0.5

0.6

0.7

Vin (V)

Vin (V)

Figure 6: Measured FGUVMOS inverter characteristics for different supply voltages and current levels.

Figure 5: Measured FGUVMOS inverter currents

(nFET) for different supply voltages,’- -’ represents

Vdd = 0.3V , solid line represents Vdd = 0.5V and ’-.’

represents Vdd = 0.7V . The current level (equilibrium

current) vary from 2nA to 200nA.

tor feeding a differential pair. The current level

is set by the bias transistor, and the minimum

input voltage in a NMOS input pair is given by

Vbias + nVdsat < Vin < Vdd , where n is the slope

factor modeling the body effect. The bias voltage

is proportional to the threshold voltage for a given

bias current. To provide a cut-off in the M Hz

range the bias transistor can not be operated in

deep weak inversion, hence the input voltage and

supply voltage are limited by the threshold voltage and the saturation voltage and the body effect

(Vinmin , Vdd > 1V ).

By eliminating the bias transistor we can decrease the supply voltage further (to n4UT ≈ 200mV ).

The challenge is to design a differential input stage

without the traditional differential pair.

The currents in figure 7 can be expressed as

sistors, gates or sub-circuits individually.

The FGUVMOS inverter, or any FGUVMOS

circuit, may be programmed to different current

levels and supply voltages as shown in Fig. 5 and

6. The inverter threshold can be set to Vdd /2 for

all supply voltages and current levels.

The ULV floating-gate analog circuits presented

in this paper can operate down to approximately

100mV in weak inversion. In the following analysis all transistors are assumed to be in saturation, hence only the saturation voltage and required frequency response limit the minimum usable supply voltage. Typical supply voltages for

the ULV floating-gate circuits are in the range

0.3V to 1.0V .

In

4. Ultra low-voltage floating-gate analog

circuits

Ip

A major challenge for the analog designer is to

cope with the reduced supply voltage in modern

processes. Low-voltage analog design has been

and will be an important aspect to address [7, 8].

The minimum supply voltage in low-voltage circuits can be defined as Vsup,min = Vth + 2Vsat .

Differential amplifiers are biased with a transis-

1

Vdd

(Vi −

)ki } ·

nUt

2

Vdd

1

exp{

(Vout −

)kr }

nUt

2

1 Vdd

(

− Vi )ki } ·

= Ibec exp{

nUt 2

1 Vdd

exp{

(

− Vout )kr }.

nUt 2

= Ibec exp{

∗

In = Ip and ki = kr gives Vout = Vin

≡

Vdd − Vin and In = Ip = Ibec . The output gain

is controlled by the capacitive division factors k i

and kr (Ci and Cr ). By using a slightly smaller kr

4

C pi

Ipi

Ip

Cr

Vin

Cpr

Cnr

Vin

Vout

In

Ci

(a)

Ip

Vin

Vout

Cr

Cr

Vout

Vin

Vout

In

Inr

Ini

C ni

Ci

Ipr

Ci

(b)

(c)

(d)

Figure 7: Floating gate analog inverters, and (d) analog inverter symbol.

0.8

compared to ki we can compensate for the Early

effect.

Matlab [9] simulation of the analog inverter

in Fig. 7 using the EKV [10] transistor model are

shown in Fig. 8 and 9together with spectreS [11]

simulation of the analog inverter in Fig. 7 using

the process parameters for the AMS 0.8µ double

poly process [12] and transistor model level 15.

Note that the analog inverter operates very close

to the supply rails. Measured input output characteristics of the analog inveter is shown together

with simulation results in Fig. 10.

The analog inverter was implemented in the

AMS 0.6µ CMOS process using transistor sizes

10/0.6µ (W/L). Fig. 11 shows the equilibrium

point current (Ibec ) for different nFET programming voltages V+ applied at Vss . The pFET programming voltages V− applied at Vdd was automaticaly selected to provide an output voltage

Vout equal to Vdd /2 (0.4V ) in the programming

mode. We notice that the increase in the euilibrium point current is exponentially dependent on

the programming voltage, hence the increase in

the floating-gate offset is linearly dependent on

the prgramming voltage. The inverter characteristics for equilibrium point currents ranging from

0.5nA to 2µA are shown in Fig. 12.

Idealy the transistor currents should not be affected by the input voltage due to the feedback capacitor. The nFET transistor currents are shown

in Fig. 13. We can examine the quality of the

analog inverter by measuring the gain shown in

Fig. 14.

The mean gain value in the linear range (Vin

spectre

Fig 3 (c)

0.7

Fig 3 (b)

0.6

Vout (V)

0.5

0.4

0.3

0.2

0.1

Fig 3 (a)

0

0

0.1

0.2

0.3

0.4

0.5

Vin (V)

0.6

0.7

0.8

0.9

Figure 8: Input output characteristics.

1.2

Fig 3 (a)

Fig 3 (b)

1.1

spectre

1

Fig 3 (c)

|Gain|

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0

0.1

0.2

0.3

0.4

0.5

Vin (V)

0.6

0.7

0.8

0.9

Figure 9: Gain of analog inverters.

5

Ibec (A)

Vb*

Cb

Ip

Ci

Vin

Cr

Ci

-5

10

-6

10

-7

10

-8

10

-9

10

-10

Vout

Vout

Cr

10

Vin

In

2

Vb

Cb

2.5

Vb

(a)

0.8

3

3.5

Programming voltage V+ (V)

(b)

Figure 11: Measured equilibrium point current Ibec

spectre

for different programming voltages.

0.7

measurement

0.6

Vout (V)

0.5

matlab

0.4

0.3

0.8

Increased equilibrium point current

0.2

0.7

0.1

0.6

0

0.1

0.2

0.3

0.4

0.5

Vin (V)

0.6

0.7

0.8

0.9

0.5

Vout (V)

0

(c)

0.4

0.3

Figure 10: Floating-gate analog inverter circuit with

corresponding symbol. In (c) measurement (solid line)

is shown together with simulation results using SpectreS(dotted line) and matlab (dashed line).The supply voltage is equal to 0.8V .

0.2

0.1

Increased equilibrium point current

0

0

0.1

0.2

0.3

0.4

Vin (V)

0.5

0.6

0.7

0.8

Figure 12: Measured analog inverter characteristics

for equilibrium point currents ranging from 0.5nA to

2µA.

6

-0.93

-0.94

10

-0.95

-5

-0.96

In (A)

10

Gain

10

-6

-7

-0.97

-0.98

-0.99

10

-8

-1

10

-9

-1.01

-10

10

10

10

-9

10

-8

-7

10

-10

10

-6

10

Ibec (A)

Figure 15: Measured analog inverter gain.

-11

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

Vin (V)

ranging from 0.2V to 0.6V ) for the different equilibrium point currents are shown in Fig. 15.

The analog inverter can be programmed to different supply voltages as shown in Fig. 16 and

17. The linear range relative to the supply voltage is reduced for extreme low supply voltages

due to the large relative linear range (≈ 4UT in

weak inversion). The linear range is limited only

by the linear region of the transistors, thus we

may express the linear range in weak inversion as

Lin = Vdd − 0.2V . The analog inverter gain for

supply voltages equal to 0.3V , 0.5V and 0.8V are

shown in Fig. 17. The mean gain value in the linear region is −0.922, −0.980 and −1.01 for supply

voltages 0.3V , 0.5V and 0.8V respectively.

A “digital” double input inverter as shown in

Fig. 18 can be used as a ULV output stage. The

output current of the inverter in Fig. 18 (a) is

given by

Figure 13: Measured nFET transistor current of the

analog inverter.

-0.4

-0.5

-0.6

Gain

-0.7

-0.8

-0.9

Iout

-1

1

Vdd

(Vb −

)kb } ·

nUt

2

1 Vdd

(

− Vin1 )ki1 } ·

(exp{

nUt 2

1 Vdd

exp{

(

− Vin2 )ki2 } −

nUt 2

Vdd

1

(Vin1 −

)ki1 } ·

exp{

nUt

2

= Ibec exp{

Increased equilibrium point current

-1.1

0

0.1

0.2

0.3

0.4

Vin (V)

0.5

0.6

= Ip − In

0.7

0.8

Figure 14: Measured analog inverter gain.

7

-5

10

Vb*

Cb

C i2

0.8

Ip

0.7

Vin2

C i1

Vin1

0.6

Iout

Vout

C i1

0.5

Vout (V)

Vin1

In

Vin2

VDD=0.8V

0.4

Vb

C i2

0.3

Cb

VDD=0.5V

Vb

0.2

(a)

0.1

0

(b)

VDD=0.3V

0

0.1

0.2

0.3

0.4

Vin (V)

0.5

0.6

0.7

Figure 18: Double input inverters. (b) Double input

inverter with bias input.

0.8

Vin2

Figure 16: Measured analog inverter characteristics

Vin2

Iout

Vin1

Vout

for supply voltages 0.8V , 0.5V and 0.3V .

Vin1

I out

Vout

Vb

(a)

(b)

Figure 19: Floating gate amplifiers, with and without

bias input.

exp{

-0.4

1

ki1 = ki2 = ki gives Iout = −2Ibec exp{ nU

(Vb −

t

1

Vdd /2)kb } sinh{ nUt (Vin1 + Vin2 − Vdd )ki }. In order to get a symmetric differential output current

∗

we sustitute Vin with Vin

= Vdd − Vin . Although

the bias input can be used to set the appropriate

current level it will decrease the gain due to the

reduced input capacitive division factors, that is

kimax ≤ 1/2 − kb . If a wide linear range is required for some application we can increase the

linear range by applying a small input capacitive

factor ki1 and ki2 , either by using the bias input

and/or using smaller input cacapitors Ci1 and Ci2 .

-0.5

-0.6

VDD=0.8V

Gain

-0.7

VDD=0.5V

-0.8

VDD=0.3V

-0.9

-1

-1.1

0

0.1

0.2

0.3

0.4

Vin (V)

0.5

0.6

0.7

Vdd

1

(Vin2 −

)ki2 }).

nUt

2

0.8

5. A four transistor ULV FGUVMOS transconductance amplifier

Figure 17: Measured analog inverter gain for supply

voltages 0.8V , 0.5V and 0.3V .

The ULV amplifier can be implemented in different ways using the analog “gates” presented, as

8

Vb*

3 x 10

-6

Cb

2

Cb

Ci

1

Vin1

Ci

Cr

Cr

Vx

Vin2

Ci

Iout [A]

Ip

Ci

Iout

Ci

Vb = 0.3V

-1

In

Cb

0

Vout

Vb = 0.5V

Ci

-2

-3

-0.4

Cb

-0.3

-0.2

Vb

-0.1

0.0

0.1

Vin1 - Vin2 [V]

0.2

0.3

0.4

(a)

15

0

magnitude

10

Iout

Magnitude [dB]

shown in Fig. 19.

The output current of the ultra low-voltage

transconductance amplifier shown in Fig. 20 is

given by

Substituting Vx = Vdd − Vin1 into equation 1

leads to

1

= 2Ib sinh{

(Vin1 − Vin2 )ki2 }. (1)

nUt

35.71

phase

5

0

107.14

-5

142.85

-10

178.56

-15

214.27

-20

0

10

SpectreS simulations of the ULV transconductance amplifier with capacitor values Ci = 11f F ,

Cr = 10f F and Cb = 6f F and transistor size

W/L = 0.8µ/0.6µ (AMS 0.6µ) are shown in Fig.

21. The gain can be increased significantly by increasing the transistor length. Assuming transistor size W/L = 2.0µ/0.8µ (AMS 0.8µ) the cain

is close to 24dB and the CMRR is 48.9dB.

71.43

10

1

10

2

10

3

4

5

10

10

10

Frequency [Hz]

6

10

7

10

8

Phase [DEG]

Figure 20: Symmetric ULV floating gate amplifier.

250

9

10

(b)

Figure 21: Simulation of the floating gate amplifier.

AMS 0.6µ double poly CMOS process and transistor

size (W/L = 1.2µ/0.6µ).

I out1

Vin1

Vout1

6. Differential input/output ULV FGUVMOS transconductance amplifier

Vb

Fig. 22 and 23 show a fully differential FGUVMOS transconductance amplifier. The structure resembles Bram Nauta’s transducer element

[13]. It is, however, quite different. Nauta used six

CMOS inverters, Two for the input steps and two

inverter pairs between the two output nodes. Furthermore, Nauta used the supply nodes to control

the transconductance. For that purpose a tunable

power supply unit had to be incorporated. For

the circuit presented here, the biasing circuitry is

Vb

Vin2

I out2

Vout2

Figure 22: “Gate” level differential input/output

ULV FGUVMOS transconductance amplifier.

9

Vin1

Vb*

Vb*

Vout1

Iout1

2.5

x 10

-5

2

1.5

Iout1 (A)

INV1

Vb

Vin2

INV3

INV4

Vb

1

0.5

0

Iout2

Vout2

-0.5

-1

-1.5

-0.4

INV2

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

0.4

Vin (V)

Figure 23: Differential input/output ULV FGUVMOS transconductance amplifier.

Figure 24: Measured output current of the FGUVMOS transconductance amplifier for different current levels (Ibec ). Vdd = 0.8V .

easier to accomplish without the use of additional

circuitry.

The circuit has no internal nodes, hence no

parasitic poles. Inverters INV3 and INV4 are

shunted resistances connected between the output nodes and the common mode voltage level,

Vdd /2. The value of these resistances are 1/gm,4

and 1/gm,5 , where gm,n is the transconductance

of inverter n. These output resistances are dynamic. For common mode output signals, the

transconductances of the output inverters are at

the maximum, and for differential output signals

the transconductances are at the minimum (the

elements are inverters, so the sign of the current

through the load inverters will be the inverse of

the current through inverters INV1 and INV2).

This gives a low-ohmic load for common mode

signals and a high-ohmic load for differential signals, resulting in a controlled common mode voltage level for the outputs. The transconductances

of the load inverters may also be adjusted by the

bias-terminal, Vb and Vb∗ , giving the ability to

tune the output resistance.

The V-I conversion is performed by inverters

INV1 and INV2, and from the previous derivation

of the output current of the analog FGUVMOS

inverter in expression it is obvious that the input-

0.8

0.7

Vout1 (V)

0.6

0.5

0.4

0.3

0.2

0.1

0

-0.4

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

0.4

Vin (V)

Figure 25: Measured output voltage of the FGUVMOS transconductance amplifier for different current levels (Ibec ). Vdd = 0.8V .

10

20

x 10

-7

3

2

1

Iout1 (A)

Vfgn>Vtn

10

Magnitude [dB]

4

0

0

-10

Vfg<Vt

VDD = 0.8V

-1

VDD = 0.1V

-2

-20

VDD = 0.3V

-3

-30 0

10

VDD = 0.5V

-4

-5

-6

-0.4

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Figure 26: Measured output current of the FGUVMOS transconductance amplifier. Vdd = 0.8V ,

0.5V , 0.3V and 0.1V .

VDD = 0.8V

Vout1 (V)

0.6

VDD = 0.5V

0.4

VDD = 0.3V

0.3

0.2

0.1

VDD = 0.1V

0

-0.4

-0.3

-0.2

-0.1

0

Vin (V)

0.1

0.2

0.3

6

8

10

output relationship is sinh-shaped. Fig. 24 shows

the output current and Fig. 25 shows the output voltage for different current levels (Ibec ). The

supply voltage used for the measurements is 0.8V.

The amplifier can be programmed to extreme low

supply voltages without reducing the current level

as shown in Fig. 26 and 27. The gain for supply

voltage 0.1V is reduced to less than -1, due to operating the transistors in the linear region. However, the amplifier can be programmed to operate

at these extreme low supply voltages although the

inherent linear region of the MOS transistor limits

the practical supply voltage to ≈ 0.3V

As the power supply is lowered the cut-off frequency of the transistor is decreased, hence ULV

circuits should have poor high-frequency performance. The cut-off of the MOS transistor is, however, proportional to the current level, and the

current level of the FGUVMOS transistor may

easily be tuned with the programmed offset voltages on the floating gate. Consequently, the cutoff is adjusted along with the offset voltage. Fig. 28

shows the magnitude response of the FGUVMOS

amplifier for different current levels. Another interesting advantage with the circuit is that the

phase-response may be adjusted with the biasterminals of the load inverters. This property is

very favorable in many applications, especially in

high order systems, i.e. high-order filters, where

0.8

0.5

4

10

10

Frequency [Hz]

Figure 28: Simulated frequency response of the FGUVMOS transconductance amplifier. Vdd = 0.8V

0.4

Vin (V)

0.7

2

10

0.4

Figure 27: Measured output voltage of the FGUVMOS transconductance amplifier. Vdd = 0.8V , 0.5V

0.3V and 0.1V .

11

multiple replicas of the device is used, since the

property may be utilized to improve the phase

margin of intrinsic poles.

[8] P. E. Allen and A.L. Coban: “Low-Voltage Analog IC Design in CMOS Technology”, IEEE

Transactions on Circuits and Systems-I, vol. 42,

no. 11, pp. 955-958, 1995.

7. Conlusion

[9] Matlab reference Guide:

Inc.”, Natick, MA.

A programming technique for floating-gate circuits has been presented. The floating-gates are

programmed using the supply rails and UV-light,

hence no additional programming circuitry is needed.

The tuning technique is used to program an FGUVMOS digital inverter and an FGUVMOS analog inverter to different current levels and supply voltages. Two examples of ULV floating gate

transconductance amplifiers are presented.

“The Math Works

[10] C.C. Enz, F. Krummenacher and E.A. Vittoz:

“An analytical MOS Transistor Model Valid in

All Regions of Operation and Dedicated to LowVoltage and Low-Current Applications.”, Special

issue of the Analog Integrated Circuits and Signal

Processing journal on Low-Voltage Design, vol.

9, pp. 27–44, July 1995.

[11] Cadence Design Systems: “Spectre Reference”,

Product version 4.4.1, Feb. 1997.

[12] Austria Mikro Systeme International: “0.8 um

CMOS Process Parameters”, no. 9933006, rev.

B, Mar. 1997.

References

[1] Y. Berg and T. S. Lande: “Programmable

Floating-Gate Mos Logic for Low-Power Operation”, In Proc. IEEE ISCAS, pp. 1792–1795,

Hong Kong, June 1997.

[13] B. Nauta: “A CMOS Tranceconductance-C Filter Technique For Very High-Frequencies”, IEEE

Journal Of Solid-State Circuits, vol. 27 no. 2,

1992.

[2] Y. Berg and T. S.Lande: “Area Efficient Circuit Tuning with Floating-Gate Techniques”, In

Proc. IEEE ISCAS, Orlando, USA, May-June

1999.

[3] Y. Berg, D. T. Wisland and T. S. Lande: “Ultra

Low-Voltage/Low-Power Digital Floating-Gate

Circuits”, IEEE Transactions on Circuits and

Systems, vol. 46, No. 7, pp. 930–936,july 1999.

[4] C. Diorio, P. Hasler, B. A. Minch, and C. Mead,

“A Complementary Pair of Four-Terminal Silicon Synapses,” Analog Integrated Circuits and

Signal Processing, vol. 13, nos. 1-2, pp. 153-166,

1997.

Yngvar Berg received the M.S. and Ph.D.

degrees in Microelectronics from the Dept. of Informatics, University of Oslo in 1987 and 1992 respectively. He is currently working as an associate

professor with the same department. His research

activity is mainly focused on low-voltage/low-power

digital and analog floating-gate VLSI design.

Øivind Næss received the B.sc and M.Sc.

from the Department of Informatics, University

of Oslo, Norway in 1997 and 1999, respectively.

The M.Sc. thesis concerned design of FGUVMOS

analog filters. His main interests are low-voltage

analog CMOS design, esp. amplifiers and filters.

Hopefully, he will pursue as a Ph.D-student with

[5] Y. Berg, D. T. Wisland and T. S. Lande.

“Floating-Gate UVMOS Inverter”, In proc.

IEEE NORCHIP, november. 1997.

[6] R. G. Benson and D. A. Kerns: “UV-Activated

Conductances Allow For Multiple Scale Learning”, IEEE Transactions on Neural Networks,

vol. 4, no. 3, pp. 434–440, May 1993.

[7] P. E. Allen and A.L. Coban: “A New LowVoltage CMOS Transconductance Cell Based

on Parallel Operation of Triode and Saturation

Transconductors”, Electronic Letters, vol. 31, no.

22, pp. 1886-1887, 1995.

12

amplifiers. Hopefully he will pursue his M.Sc. this

year with the Micro-electronics Group, Department of Informatics, University of Oslo.

the Microelectornics Group, Department of Informatics, University of Oslo.

Mats Høvin was born in Mo i Rana, Norway

on May 9, 1965. He received the E ngineer degree

in electronics from NKI Ingeniør Høyskole, Oslo,

Norway in 1986 a nd the Cand.Scient degree from

the Dept. of Informatics, University of Oslo, No

rway in 1995. He is currently a Ph.D student

at the Microelectronics Systems Gr oup, Dept.

of Informatics, University of Oslo, Norway. His

current research int erests includes analog- and

frequency-to-digital conversion with delta-sigma

no ise shaping, frequency demodulation and low

voltage CMOS design.

Henning Gundersen received his Electronic

Engenieer exam in 1985, he has worked as a Maintenance Engenieer in the Norwegian Broadcasting

Corp. until he started with his M.Sc in 1998, concerning design of FGUVMOS low-voltage analog

13