Qt.......... COWAN Now A&-

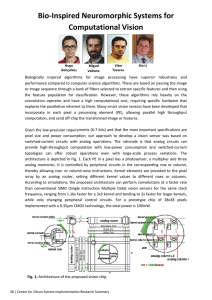

advertisement