Problem Set 7 Solutions

University of California, Berkeley

EE 42/100

Spring 2012

Prof. A. Niknejad

Problem Set 7

Solutions

Please note that these are merely suggested solutions. Many of these problems can be approached in different ways.

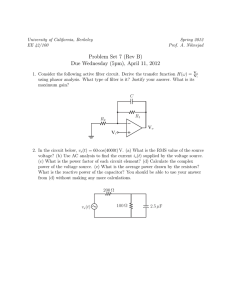

1. The op amp circuit is a form of a non-inverting amplifier, with gain 1 +

Z

1

= R

2 and Z

2

= R

1

|| 1 jωC

. The transfer function is thus given by

Z

2

Z

1

. Here,

H ( ω ) = 1 +

R

1

/jωC

R

1

+1 /jωC

R

2

=

R

1

+

R

2

R

2

+ jωR

1

R

2

C

+ jωR

1

R

2

C

This is a low-pass filter. The maximum gain occurs at DC, when ω = 0. The capacitor becomes a short and we get a gain of 1 + R

1

R

2

, exactly what we would expect from a non-inverting amplifier. As ω → ∞ , the gain goes to 1. This is because the capacitor shorts out and connects V o to V i

.

2. (a) The RMS value of the voltage is simply given by V rms

=

V amp

2

=

√

2

= 30

√

2 V.

(b) To find the current, we can use Ohm’s law with the phasor of the source voltage and the equivalent impedance:

I s

=

V

Z s eq

60 0 ◦

=

200 + 100 || (1 /j (4000)(2 .

5 µ ))

= 0 .

235 11 .

3

◦

A

We thus have the magnitude and phase of the current in the time domain: i s

( t ) = 0 .

235 cos(4000 t + 11 .

3 ◦ )

(c) The power factor of the voltage source is P F s

= cos( φ v

− φ i

) = cos(11 .

3 ◦ ) = 0 .

981.

The power factor for the resistors is 1, since the voltage and current across resistors are always in phase, while the power factor for the capacitor is 0, since they are always 90 ◦ out of phase for a capacitor.

(d) The complex power is simply given by

S =

1

2

V · I

∗

=

1

2

(60 0

◦

) · (0 .

235 − 11 .

3

◦

) = 7 .

05 − 11 .

3

◦

VA

(e) Because of power conservation, the average power drawn by the resistors is opposite to that of the source: P = < ( S ) = 6 .

9 W. We can do the same thing for the reactive power of the capacitor: Q = = ( S ) = − 1 .

38 VAR.

3. Notice that the op amp is in the inverting configuration, with gain − Z

2

Z

1

.

V o

= −

(1 /j (2000)(0 .

1 µ )) || (10k)

1k

V i

The average power is thus just

V 2 rms

R

L

=

=

(2 .

24 /

√

2) 2

1k

− (2

= 2

−

.

j 4)0

5 mW

.

5 0

◦

= 2 .

24 117

◦

V

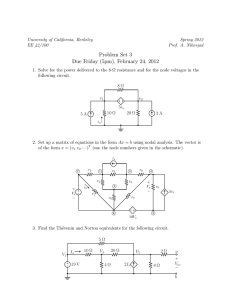

4. To use the maximum power transfer theorem, we first need to find the Th´evenin impedance. Since the circuit contains a dependent source, the easiest way will be to zero out the independent current source (thus getting rid of the left branch) and attach a test voltage to the circuit in place of the load.

6 kΩ

I x

− j 4 kΩ 2000 I x

V t

+

I t

Notice that I t

= I x

. The impedance we want is given by Z

T h

= V t . One thing we can

I t do is to write an equation using Ohm’s law with the two voltage sources in series:

I t

=

2000 I t

+ V t

6000 − j 4000

We thus have the following relationship:

Z

T h

=

V t

I t

= 4000 − j 4000 Ω

The load impedance is just the complex conjugate: Z

L

= Z ∗

T h

= 4000 + j 4000 Ω.

5. One would expect that the node voltages decrease monotonically toward − 20 V from

+20 V, going from left to right, since there is no reason for the voltage to go up in the middle. This also implies that current is in general flowing from left to right.

+20 V

R

1

200 Ω

D

1

V

1

I

R

2

200 Ω

D

2

V

2

R

3

200 Ω

V

3

+ V −

D

3

R

4

200 Ω

− 20 V

Thus it can be inferred that

V

D

1

<

D

1 must be on. If not, V

1

0. But since we inferred that V

2 must be negative to satisfy

≤ V

1

, this would turn D

2 on, shorting V

2 to 0 and causing a contradiction.

So

V

2

D

1 is on. Then V

1

= 0, and since V

2

= 0. Since the voltage drop across R

2

≤ V

1

, this forces D

2 to also turn on such that is 0, we find that I = 0. So all current from

+20 V flows to ground via D

1

, and any current going to the right flows up from ground through D

2

. Both currents flow forward across the diodes.

2

What about D

3

? Suppose it were on. Then V

3

= 0. No current flows through R

3 due to 0 voltage drop, which means the current going through R

4 happen.

D

3 must be off and we get V

3

Hence we have V = V

2

− V

3

= − 10 V.

must come through D

3 to satisfy KCL. But current is not allowed to flow backward across D

3

, so this cannot

= − 10 V, causing D

3 to be backward biased.

6. When v in is positive, both diodes are forward-biased and on. Then the first resistor is shorted, and we simply have v o

= v in

. When v in is negative, both diodes are backward-biased and remain off for a small range, until v in becomes sufficiently negative at − 5 V to cause the Zener diode to go into breakdown mode. Before this, no current flows, so v o

= v in

. Once the Zener diode breaks down, current starts to flow across both resistors, so we have a voltage divider: v o

= 1

2

( v in

− 5).

7. Notice that the circuit is very similar to a clmap circuit, except that a Zener diode is used in place of a battery. If the output voltage attempts to go lower than − 5 V, the

Zener diode breaks down and current flows backward across it, charging the capacitor to 5 V. So the negative peak of the waveform is clamped to − 5 V.

3