Device Independent Process Control of Dielectric

advertisement

Device Independent Process Control of Dielectric

Chemical Mechanical Polishing

by

Taber Hardesty Smith

Bachelor of Science, Rochester Institute of Technology, May 1994

Master of Science, Massachusetts Institute of Technology, June 1996

Submitted to the Department of

Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 27th, 1999

©Massachusetts Institute of Technology, 1999. All Rights Reserved.

A u th o r ....................................................................

Electrical Engineering and Computer Science

September 27th, 1999

Certified by ..............

Boning

Duan(

Associate rofessor

Electrical Engineerin g and Computer Science

Accepted by ..............

MASSACHUSETTS INSTITUTE

OFTECHNOLOGy

FMAF

LIBRARIES

Arthur C. Smith

Chairma n, Department Committee on Graduate Students

Electrical Engineering and Computer Science

I

Device Independent Process Control of Dielectric

Chemical Mechanical Polishing

by

Taber Hardesty Smith

Submitted to the Department of Electrical Engineering

and Computer Science on September 27, 1999, in partial fulfillment

of the requirements for the degree of Doctor of Philosophy

Abstract

The use of the chemical-mechanical polishing (CMP) process in the semiconductor

industry is growing rapidly, and it is a critical step in the manufacturing of integrated circuits. The CMP process is complicated by many factors, and controlling all of these factors in a single controller has been unrealistic. One of the most significant factors

complicating control is the dependency of the polishing process on the pattern layout of

the particular device being polished. The interactions between these patterns and the polishing behavior of a CMP tool make monitoring and controlling the process particularly

difficult. Current techniques focus on the control of a few sites on a single type of layout

being polished on a single tool. We show that using only a few sites does not give insight

into what is happening at sites that are not measured and controlled. Further, by restricting

attention to a single device, these controllers address only pieces of a larger problem and

fail to take into account the effects of different devices being polished on the same tool.

This thesis outlines a comprehensive framework for controlling the polishing of multiple devices with arbitrary layout patterns being polished on a single CMP tool. We explore

the use of an advanced CMP process model in conjunction with an on-line metrology system and a simple filtering algorithm for controlling the average post-polish thickness and

monitoring the global non-uniformity of multiple devices being processed. This framework provides several benefits. First, it allows measurements from any device to be used

to update the tool level model that can be used with any other device being processed. Second, it allows us to measure only a few points, while very accurately controlling the average of the true thickness profile. Third, it allows us to monitor the total non-uniformity of

the polishing process for each device being processed. Experimental work shows that this

approach results in very accurate control of the true average thickness of multiple devices,

with a lot to lot variability of only 100A. In addition, we are able to very accurately predict

the global non-uniformity of the polished wafers. However, the model used was found to

have a minor dependence on the device type, indicating that an improved layout pattern

functional model is necessary to achieve truly device independent control. We explore one

possible model that might reduce these dependencies, and show this model provides a

50% improvement in fitting errors of both raised and down area thicknesses. Despite this,

we find that device dependencies still exist with the improved model, and further work is

necessary to make the model and control strategy completely device independent.

3

Acknowledgments

I would like to thank my wife, Tina, for being the perfect complement of my technical

persona, and for being the source of much joy in my life. I apologize for making her sit

through many conversations bored to tears. She has been a huge supporter of my efforts

and drive to continue. She has sacrificed a lot in her life to make this possible, and much of

the credit goes to her.

I would also like to thank my mother and father, Cheryl Hardesty and Dale Smith, for

making me who I am today, and for always being so supportive of everything that I have

done or ever wanted to do. My brother, Dirk, has been a role model of character and

respect for me since birth. My brother Brett Smith has been a driver of my efforts in everything from soccer to studying all my life. My family thus owns much of the credit.

I don't normally believe in luck, but one phone call five years ago is hard to argue

with. I would like to thank my advisor, Professor Duane Boning, for calling, and subsequently encouraging every idea I have had, keeping me straight and barely under control,

and having faith in me when I was drowning in pressure. He has been an inspiration for

me, who never ceases to amaze me with his ability or character. He has been an outstanding advisor, who I would not have traded for anyone else. Our journey together has been a

long one, yet it seemed to go by so fast. This is what happens when you are having fun,

and working with Duane has been the best.

Most of my experimental work was done in collaboration with Texas Instruments Inc.,

in Dallas, TX, where I spent nine months and a lot of their resources. I was very fortunate

to meet a lot of outstanding people there. I would to thank Dr. Jerry Stefani for many

things, including agreeing to co-advise my thesis. Jerry has been a great friend, mentor,

and supporter throughout my Ph.D work. He made sure we had fun in Texas, and for that I

have many fond memories. He has also been a great mentor, and has taught me a tremendous amount. He is amazing at pulling people and resources together, organizing work

efforts, and championing what he believes in, so the credit for much of my work goes to

him as well. I would also like to thank Dr. Simon Fang. Simon is one the funniest, hardworking, and intelligent people I have ever worked with. Much of the work in this thesis

and other works were the result of one idea caught from the fountain of knowledge

eschewing from Simon. I would also like to thank Simon for helping to manage and direct

much of my work at TI in the Spring of 1998, and for staying up all night in the lab with

me (I still can't figure that one out). I would also like to thank Dr. Stephanie Butler, who

has supported my work from the beginning. She has taught me a lot about semiconductor

manufacturing, process control, organizations, and how to look for relevant and important

problems. I would like to thank Dr. Greg Shinn, for being very supportive of my efforts

and my work in the CMP area at TI. I am also thankful to Leif Olsen for helping out with

my work, and allowing me to constantly interrupt his work to run my experiments. I would

also like to thank many other people at TI, including Chris Baum, Mark Betts, Dr. Scott

Bushman, Alicia Clark, John Clark, Charles Crain, Dr. Michael Daniels, Dr. Santos Garza,

Susie Gauna, Dr. Jarvis Jacobs, Dorothy McAllister, Rita McKern, Justin Scout, Dr. Robert Soper, and Dr. Michael West, who made my stay there a great experience.

Here at MIT, my colleagues in the Process Control and Statistical Metrology Groups

have made my life at MIT a blast. Aaron Gower is the most selfless and honorable person

I have ever met. Thanks go to him for helping to build, set up, or debug every mathemati4

cal, computer, or programming problem I had. Also for all the good times, and for putting

up with me for five years. I would like to thank Sandeep Sadashivapa for lots of good

times outside the office, and wish him the best of luck in his new life outside of MIT. I

would also like to thank Brian Goodlin for a lot of great discussions, and lots of good work

together. Brian taught me a lot about the science of learning, in everything from modeling

to guitar. I would like to thank Dave White for all the great discussions which educated me

on topics related to work, but even more not related to work. From the old days, I would

like to thank Minh Le, who is also a fountain of amazing ideas, for all the heated discussions on work and life, and for keeping in touch. The same for Dr. Ka Shun Wong, and for

being an example of complete diligence that I pale in comparison to. I would like to thank

Eric Stuckey for our work on process control together, and more so for the fun outside

work. Thanks go to Han Chen, for helping out with many theoretical problems, and for

putting up with our craziness in the office. I would to thank Rajesh Divecha and Brian

Stine for teaching me much of what I learned about Statistical Metrology. I would also like

to thank Dr. Dennis Okumu Ouma, who deepened my understanding of these and many

other areas. Tae Park, Tamba Tugbawa, Brian Lee, Charles Oji, Vikas Merhotra, Terence

Gan, and Shiou Lin Sam are to thank for broadening my experience to other areas. I would

also like to thank Angie Nishimoto for her excellent attention to detail and for the great

fun we had thermal energy. I wish all of these fine people the best of luck throughout their

lives.

I'd like to thank Professors Akintunde Akinwande and Tommi Jaakkola for agreeing to

serve on my area exam committee with a very short notice. I would also like to thank Prof.

Jung-Hoon Chun and Prof. John Tsitsiklis for reading my thesis and serving on my committee.

This work was sponsored by in part by the NSF/SRC Engineering Research Center for

Environmentally Benign Semiconductor Manufacturing. We would like to thank Paz

Amit, Avron Ger, and Nova Measuring Instruments Ltd. for their assistance in setting up

the NovaScan on-line metrology tool and performing some of the experiments. We would

also like to thank Joost Grillaert, Dr. Marc Meuris, and IMEC for valuable discussions

regarding the IMEC model.

5

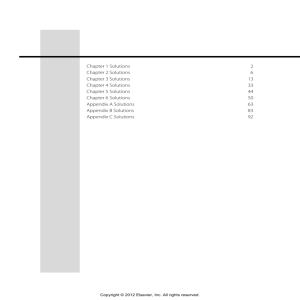

Table of Contents

17

Chapter 1. Introduction ............................................................................................

19

1.1 An Introduction to Run by Run Process Control .........................

24

1.2.1 Blanket Wafer Performance Metrics . . . . . . . . . . . . . . 29

31

1.2.2 Patterned Wafer Performance Metrics . . . . . . . . . . ..

1.2 An Introduction to CMP .......................................

34

1.3 An Introduction to CMP Process Control Issues .......................

1.4 Sum m ary ......................

..

................

..

37

Chapter 2. Control of a Single Device Using On-Line Metrology .........................

41

........

42

2.1 Evaluation of On-Line Metrology for CMP ...........

2.1.1 Measurement Repeatability

......

. . . . . . . . . . . . . . . . . . 45

2.1.2 Reliability . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.1.3 Correlation with Ex-Situ Metrology . . . . . . . . . . . . . . . 49

53

2.2 Throughput and Cost of Ownership Improvements ......................

. . . . . . . . . . . . . . . . . .54

2.2.1 Throughput . . . . ...

. . . . . . 56

. . . . . . . . . .

Reductions

2.2.2 Cost of Ownership

59

2.3 Run by Run Control of CMP with On-Line Metrology ....................

2.3.1 Experimental Setup . . . . . . . . . . . . . . . . . . . . .. 60

2.3.2 The Run by Run Process Control Algorithm . . . . . . . . . . . . 61

2.3.3 Patterned W afer Control . . . . . . . . . . . . . . . . . . . . 62

66

2.4 Sum m ary .......................................................

Chapter 3. Control of Multiple Devices in Dielectric CMP ...................................

69

3.1 Pattern Dependencies in Dielectric CMP ..............................

71

3.2 Modeling of Dielectric CMP .......................................

74

3.3 Problems With Existing Control Methods in Dielectric CMP ..............

83

3.4 Current Methods for Controlling Multiple Devices in Dielectric CMP ....... 87

3.5 The Multiple Device Control Problem for Dielectric CMP ................

92

3.6 A Framework for the Control of Multiple Devices in Dielectric CMP ....... 101

3.6.1 A Device Independent Control Algorithm . . . . . . . . . . . . 103

3.6.2 Further Discussion of the Device Independent Control Algorithm

. . 108

3.7 Experimental Results ............................................

3.7.1 Updating Both Planarization Length and Blanket Removal Rate . . .

3.7.2 Updating Blanket Removal Rate Only . . . . . . . . . . . . .

3.7.3 Correcting for Device Dependencies in the Blanket Rate . . . . . .

7

110

111

116

119

3.8 Sum mary ......................................................

Chapter 4. A Dielectric CMP Model Combining Density and Step Height

Dependencies ..............................................................................................

122

125

4.1 Density and Step Height Dependent Models ...........................

127

4.2 Analysis of the MIT Density Model .................................

131

4.3 A Combined Density and Step Height Model ..........................

134

4.4 Variations of the Time-Density Model ...............................

137

4.5 Polish Time and Device Dependencies ...............................

143

4.6 Sum mary ......................................................

146

Chapter 5. Conclusions and Future W ork ................................................................

149

References ......................................................................................................................

157

8

List of Figures

Chapter 1.

Figure 1.1. An uncontrolled drifting process.

20

..............................

Figure 1.2. SPC control of a drifting process using tuning with WECO rules. ....... 22

24

Figure 1.3. EWMA control of a drifting process ..............................

Figure 1.4. Schematic application of the CMP process in interconnect formation. . . . . 26

Figure 1.5. Chemical-mechanical polishing tool configuration. ..................

Figure 1.6. Diagram of pad, slurry, and surface interactions.

.

27

28

..............

29

Figure 1.7. Blanket wafer measurement sampling patterns. . .....................

Figure 1.8. Blanket wafer removal rate profile. The surface is an interpolation based on the

measured points, which are indicated by the stars.

.....

..............

. .. ....

30

Figure 1.9. Blanket wafer post-polish thickness profile.. ........... .............

30

Figure 1.10. A typical die sampling plan. . . . . . ..............................

31

Figure 1.11. Typical structures used for step height measurement..........

.. .. ....

32

Figure 1.12. A typical step height measurement before planarity is reached . ........ 32

Figure 1.13. A typical step height measurement near planarity. ..................

33

Figure 1.14. The within-die variation of a typical production wafer................

34

Figure 1.15. Average removal rate of blanket sheet film PETEOS wafers...........

35

Figure 1.16. Average removal rate of patterned PETEOS wafers..................

35

Figure 1.17. Within-wafer non-uniformity of blanket sheet film PETEOS wafers. .

36

Chapter 2.

Figure 2.1. Polishing sequence with on-line metrology. ........................

43

Figure 2.2. The on-line pattern recognition system.............................

44

Figure 2.3. Correlation plot of the on-line and ex-situ post-polish patterned wafer

thicknesses . ........................................................

51

Figure 2.4. Polishing with look-ahead wafers, rework, and ex-situ metrology. Total time

per lot with 2 wafer rework is 255 minutes; a throughput of 0.2353 lots per hour. Total

55

time per lot with 24 wafer rework is also 255 minutes........................

9

Figure 2.5. Polishing with look-ahead wafers, rework, and in-line metrology. Total time

per lot with 2 wafer rework is 142 minutes; a throughput of 0.4225 lots per hour. Total

time per lot with 24 wafer rework is 177 minutes; a throughput of 0.3390 lots per hour.

These are improvements of 80% and 44%, respectively . .....................

55

Figure 2.6. Percent reduction in the cost of ownership vs. percent rework for a process with

look-ahead wafers ...................................................

57

Figure 2.7. Controlled average post-polish patterned wafer thickness over the 600 wafer

experim ent . ........................................................

62

Figure 2.8. Average removal rate of patterned PETEOS wafers...................

63

Figure 2.9. Within-wafer non-uniformity of blanket sheet film PETEOS wafers...... 64

Figure 2.10. Average post-polish thickness of patterned wafers using pilot wafers and sheet

film equivalents to control the post-polish thickness of the patterned wafers . ..... 65

Figure 2.11. Controlled average post-polish patterned wafer thickness over the 600 wafer

experiment using five measurement sites .................................

65

Chapter 3.

Figure 3.1. A very densely sampled thickness profile of a typical wafer, including waferlevel and die-level variation components .................................

71

Figure 3.2. Die-level thickness profile of a test device..........................

72

Figure 3.3. Sources of thickness variation in the CMP process . ..................

72

Figure 3.4. Total, within-die, and within-wafer thickness variation of a typical test device

as a function of polishing time . ........................................

73

Figure 3.5. Cross-sectional view of the oxide thickness in a patterned wafer .........

76

Figure 3.6. The MIT density model predictions of the removal rate of the up and down

areas as a function of time for one particular density.........................

78

Figure 3.7. The MIT density model predictions of the up area removal rates and

thicknesses, as a function of time, for different densities......................

78

Figure 3.8. A cross section of the elliptical weighting function used in the density model

to calculate the effective density of the features.............................

80

Figure 3.9. A high-level view of the MIT density model . .......................

80

Figure 3.10. Measurement plan of a test layout pattern (Device #2)................

81

Figure 3.11. Measured and modeled values for the post-polish thickness of the raised and

down areas using the MIT density model .................................

82

Figure 3.12. Measured and modeled values (dashed lines) for the post-polish thickness of

the raised areas for several polish times using the MIT density model . .......... 83

10

Figure 3.13. Blanket wafer removal rate profile and patterned wafer removal rate profiles

84

over the surface of a wafer predicted by the density model....................

Figure 3.14. Example current practice for CMP process control using sheet film

equivalents (SFEs) . .................................................

87

Figure 3.15. Post-polish thickness profiles for two different devices. Measurements were

89

taken over a grid similar to that in Figure 3.10 ............................

Figure 3.16. Multiple device control using a three site average of the thickness . ..... 89

Figure 3.17. The average thickness for two different devices predicted by the MIT density

91

m odel. ....................................................

Figure 3.18. Within die variation (standard deviation of the post-polish thickness) shown

for a design of experiments that varied the table speed and down force over a wide range

.

for the dielectric CMP process . ....................................

93

Figure 3.19. Within-die variation shown over the polishing of 600 wafers. The stars are the

within-die variation measured on four dies on each wafer, and the solid line is the

average of the four die from eight wafers over the 600 wafer run. ..............

94

94

Figure 3.20. Typical structures used for step height measurement . ................

Figure 3.21. Step height measurement for a low density feature, for three different

processes, plotted against the amount removed on a blanket wafer. .............

95

Figure 3.22. Higher density structures used for step height measurements. ......... 96

Figure 3.23. Step height measurement for a low density feature, for three different

processes, plotted against the amount removed on a blanket wafer..............

96

Figure 3.24. The difference in the step height measured at low and high density features,

for three different processes, versus the blanket amount removed. .....

. ......

98

Figure 3.25. The within-die variation, measured at 25 locations in 10 die, for three different

processes, versus the blanket amount removed . ...........................

98

Figure 3.26. A device independent run by run process controller for CMP . ........ 102

Figure 3.27. The average planarization length over the course of 100 six wafer lots (solid

line), and calculated planarization lengths for each of the four die on each of these eight

.................................

wafers (dots) . .............

109

Figure 3.28. Test devices being controlled with the device independent controller. . . 110

Figure 3.29. Measurement plan of Device 1. Circles are points used for control. Crosses

112

and circles are used to determine the true average..........................

Figure 3.30. Measurement plan of Device 2. Circles are points used for control. Crosses

112

and circles are used to determine the true average..........................

Figure 3.31. Map of the dies used for the multiple device control. . ..............

11

113

Figure 3.32. Controlled average thickness of 63 sites on four dies measured following the

experiment and the device number run ..................................

114

Figure 3.33. The minimum, maximum, and range of the polished devices. The dashed lines

represent the predicted values using the model, while the solid lines indicate the values

determined from the 63 point measurements on four dies . ...................

114

Figure 3.34. Parameters extracted from the measured data during the first control

ru n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 15

Figure 3.35. Controlled average thickness of 63 sites on four dies measured following the

experiment and the device number being run..............................

117

Figure 3.36. The minimum, maximum, and range of the polished devices. The dashed lines

represent the predicted values using the model, while the solid lines indicate the values

determined from the 63 point measurements on four dies . ...................

117

Figure 3.37. Measurement plan of Device A. Circles are points used for control and crosses

and circles are used to determine the true average..........................

118

Figure 3.38. Controlled average thickness of 63 sites on four dies measured following the

experiment and the device number being run..............................

120

Figure 3.39. The minimum, maximum, and range of the polished devices. The dashed lines

represent the predicted values using the model, while the solid lines indicate the values

determined from the 63 point measurements on four dies . ...................

120

Figure 3.40. Difference in the average of the measured sites and the average of the

controlled sites (the "true" average) ....................................

121

Chapter 4.

Figure 4.1. A high-level view of the MIT density model. ......................

128

Figure 4.2. The removal rates of the raised and down areas using the IMEC step height

dependent model ...................................................

129

Figure 4.3. Removal rates of the density and step height dependent models for both the

MIT density model and the IMEC model ................................

130

Figure 4.4. Percent difference in removal predictions between the density model and the

IME C model. ......................................................

131

Figure 4.5. Description of the pattern features in the test mask used for model

comparisons . ......................................................

132

Figure 4.6. Measured and modeled values for the post-polish thickness of the raised areas

using the MIT density model (dashed line is the model fit)...................

133

Figure 4.7. Measured and modeled values for the post-polish thickness of the down areas

using the MIT density model (dashed line is the model fit)...................

133

Figure 4.8. Measured and modeled values for the post-polish thickness of the raised areas

using the time-density model (dashed line is the model fit)...................

136

12

Figure 4.9. Measured and modeled values for the post-polish thickness of the down areas

using the time-density model (dashed line is the model fit) ....

............

136

Figure 4.10. Model fit of the step height at contact time as a function of the effective feature

. 138

density .........................................................

Figure 4.11. Model fit of the contact time as a function of the effective feature

density ............................................................

138

Figure 4.12. Measured and modeled values for the post-polish thickness of the raised areas

using time-density model with contact height as a function of density. ......... 140

Figure 4.13. Measured and modeled values for the post-polish thickness of the down areas

using time-density model with contact height as a function of density. . . . . .....

140

Figure 4.14. Model fit for contact step height as a function of the effective feature

density..........................

...........

......... . . . .......

.

141

Figure 4.15. Model errors for raised and down areas as a function of the effective feature

density................................

...................

. . . . 141

Figure 4.16. Measured and modeled values for the post-polish thickness of the raised areas

using time-density model with contact height as a function of line space. ....... 142

Figure 4.17. Measured and modeled values for the post-polish thickness of the down areas

using time-density model with contact height as a function of line space. . ......

142

Figure 4.18. Model fit for step height at contact time as a function of line space. . . . . 143

Figure 4.19. Measured and modeled values for the post-polish thickness of the raised areas

using time-density model with contact height as a function of density for various polish

times. Dashed lines are model fits and stars are experimental data points ........ 144

Figure 4.20. The planarization length as a function of the device number being run (using

the experimental data from the third control run in Chapter 3). ............... 145

Figure 4.21. The blanket rate as a function of the device number being run (using the

146

experimental data from the third control run in Chapter 3) ...................

Chapter 5.

13

14

List of Tables

Chapter 1.

Chapter 2.

Table 2.1. Average differences between the on-line and the ex-situ measurements.

...

52

Table 2.2. Variation added to on-line measurements by polishing, residual slurry,

and wafer loading . .........................................

. . ..... 53

Table 2.3. Breakdown of the variation in the on-line metrology system.............

Chapter 3.

Chapter 4.

Chapter 5.

15

53

16

Chapter 1

Introduction

The use of the chemical-mechanical polishing (CMP) process in the semiconductor

industry is growing rapidly [1]. Its use in the polishing of inter-level dielectrics has provided the ability to significantly increase the number of levels of interconnect in integrated

circuits (ICs). This has provided improvements not only in circuit performance, but also in

product yield. In addition, it is a critical step in the manufacturing of newer generation ICs

which utilize Copper (Cu) and shallow trench isolation (STI) processes [2,3].

While the CMP process provides many benefits to the manufacturing of ICs, it also has

many problems. This is particularly true in a production setting, where the gradual wear in

the polishing pads and the simultaneous processing of several types of ICs on a single polishing tool create changes in the tool operation that are difficult to monitor and control.

Because our current understanding of the process still lags behind its application in the

industry, statistical process control techniques have been the only methods able to achieve

and maintain quality processing. There have been several works on controlling the CMP

process [4-15]. However, these initial works have addressed only pieces of a larger problem. The CMP process is complicated by many factors, and controlling all of these factors

in a single controller has been unrealistic. One of the most significant factors complicating

matters is the manner in which the particular pattern of metal and other components are

laid out within each IC to make the circuit. The interactions between these patterns and the

polishing behavior of a CMP tool make monitoring and controlling the process particu-

larly difficult. As a result, initial work on the process control of CMP focused on simple

methods aimed at monitoring and controlling the polishing of unpatterned or "blanket"

wafers [4-12]. However, as we show in Chapter 2, this is very different than controlling

directly on patterned wafers. Realizing this is critical for implementing any control

scheme in a production wafer fabrication facility (fab), later works began to focus on the

control of patterned wafers [13-15]. Direct control of patterned wafers using a multivariate

non-linear controller which monitors the average removal rate and wafer-level uniformity

was shown in [14], and patterned wafer control using a self-adjusting control algorithm to

control the average post-polish thickness was shown in [15]. These techniques focus on

the control of a few sites on a single type of layout being polished on a single tool. We

show in Chapter 3 that this gives little insight into what is happening to the locations that

are not measured and controlled, and does not ensure that the entire device (or product

type) is polished correctly. In addition, by restricting attention to a single device, these

controllers fail to take into account the effects of different patterns being polished on different tools. For example, a device of one type may wear the CMP pad more than a device

of another type, and this increased wear on the pad reduces the polishing rate of the other

devices. These effects need to be combined into a comprehensive control strategy in order

to properly control the CMP process.

The purpose of this thesis is to outline such a comprehensive framework for controlling the polishing of wafers with multiple arbitrary pattern layouts on a single polishing

tool. The approach allows for the control of multiple devices with completely different

layout patterns simultaneously being polished on a single CMP tool. This is achieved by

combining a CMP model that predicts the post-polish thickness of an arbitrary device lay-

18

out with a feedback control algorithm. We begin in this chapter by reviewing the basics of

run by run process control, the CMP process, and some well-accepted issues involved with

controlling the CMP process.

1.1 An Introduction to Run by Run Process Control

As semiconductor processing entered the late 1980s, control charting and statistical

process control (SPC) had substantially decreased process variability and increased process capability. In SPC techniques, the process output (e.g. deposition thickness) is monitored for different types of deviations from the process target. Traditionally, once an alarm

(statistically significant deviation from the process target) is signaled, the process is shut

down to perform maintenance and to re-optimize the process recipe. One set of rules for

such deviations are known as the Western Electric Company (WECO) rules. A subset of

these rules are:

1. Last point of data is greater than three standard deviations away from the

process target.

2. Two of last three data points are greater than two standard deviations away from

the target in the same direction.

3. Four of last five data points are greater than one standard deviation away from

the target and in the same direction.

4. Last eight data points are all above or all below the target.

Industry response to open-loop statistical process control has been overwhelming and the

use of this type of control has become heavily ingrained the semiconductor industry.

With the decrease in variability, however, new problems were beginning to arise. Many

processes were showing signs of a steady drifting off target [16-20]. Such drifts were often

19

caused by the build-up of material on the interior components of the tools. For example,

the deposition rate in a metal sputtering process is highly correlated to the life of the components within the tool, particularly due to the build-up of the deposited material in the

honeycomb-like collimator used to improve coverage on the surface of the wafer [20]. The

resulting drift in the deposition thickness is shown in Figure 1.1. Classical SPC

approaches assume the process is "in control," and not subject to such drift. Nevertheless,

these methods were often used to monitor and compensate for such problems [21-26].

However, the reduction of variation in semiconductor processing, combined with the

increase in process drift, resulted in a large number of alarms. Operators and engineers

began to make frequent "updates" to the process time in order to quickly bring the tool

back on-line. For example, the process output was often shifted back to the target (in the

sputter deposition case, this is done by adjusting the deposition time) by an amount typically equal to the sample mean of the error over the violation set (i.e. the last five data

points for WECO rule #3). This led to automated SPC control, whereby a simple process

6400 -3

6200

600--

2

- - - -

Ta--a-

000

52005600-

-frge

560*(3n

5800 -

-Y

- - - - - - - - - - - - - -- - - - - - - - - - - -

4.

.

5400

-. -

0

00

5200

0

*

0

4) 5000-

5

0

5

10

520253

4800460015

Run #

Figure 1.1: An uncontrolled drifting process.

20

20

25

30

model was used to automatically adjust the process inputs upon the violation of an SPC

rule. A typical control method assumes a process model is of the form:

y,n[n] = x[n] - t,[n](.1

where yn[n] is the process output (e.g. deposition thickness), x[n] is the process rate (e.g.

deposition rate), and t,[n] is the process time on run n. Typically, the estimate of the process rate is held constant, and the process output is monitored using SPC rules such as the

WECO rules above. When a violation of the rule set occurs, the estimate of the process

rate is updated to the average over the violation set, i.e.

V e {0}

x[n+1] = x[n]

x[n+1] = y,[n]/t,[n]

Ve {1}

(1.2)

(1.3)

n

x[n+1] =

yi]/t,

v e {2}

(1.4)

y,[i]/tP[i]

ve {3}

(1.5)

y,[i]/t,[i]

v E 14},

(1.6)

i=n-2

n

x[n+ 1] =

1

i= n-4

n

x[n + 1] =

1

i = n-7

where v is the rule violated (e.g. zero indicates no violation, one indicates WECO rule #1

was violated, etc.) and y,[i] is the actual process output. As can be seen in Figure 1.2, the

performance of this method in controlling a drifting process can be quite poor, in the sense

that the controlled process is often outside the two standard deviation limits. In this case,

the statistical limits were calculated using the root mean squared error (RMSE) of a linear

least squares fit of historical data of the uncontrolled thickness.

21

6400-

3a

6300

2a

6200

C

6100 -

---CY

0 - ----------------

-----

---

Target

- -------------- ------------------

.C 6000

.2

0-

:.

600

59

-

-

-

-

-

5900---------

a

-

--.

-

-

-

-

-

-

-

-

-

-

-

-

-

-

------------

-

-*

-

-.

-

-

-

-

-

-

--------------

--------------------------

-

--

-a

s

.-

5700---------------------------------------------------

56001

5

10

15

20

25

30

Run #

Figure 1.2: SPC control of a drifting process using tuning with WECO rules.

On the other hand, tools like thermal deposition furnaces experience regular shifting in

their outputs, and, for these tools, the SPC approach works quite well. Other processes

randomly drift away from the target output, but then drift back the other way, continually

wandering about the target. Current CMP tools are a good example of this [11]. These processes, like the steadily drifting processes, suffer from poor performance of automated

SPC techniques.

These problems have caused a shift in control towards continual tuning methods [420,27-42]. One example of this type of control is the exponentially weighted moving average (EWMA) controller. This control method is a combination of the EWMA SPC statistic

[21-24,26] and closed-loop feedback control. An exponentially weighted moving average

of the process output at discrete-time n has the form

x[n + 1] = w . y,[n]- (1 - w) - x[n] ,

where

x[n]

(17)

is the EWMA statistic on run n and w is the EWMIA weight, which is gener-

22

ally restricted to 0< w < 1. Higher values of w result in recent measurements more

strongly affecting the weighted average. This statistic is used to monitor a process output,

or a state of the process, and make small incremental changes to the process recipe in

order to keep the process on target. The closed-loop feedback control method using an

EMWA was developed in [27-28,4,5,16,29]. Examples of the use and study of the EWMA

controller and related variations are given in [4-5,9-12,14,16-17,27-34]. The simplest version of the controller uses a model identical to that given in (1.1), and replaces the tuning

rules (1.2) through (1.6) with (1.7). In other words, the process model is continually tuned.

For the single-variate case, the process input (process time) is calculated as

t,[n + 1]

= yd[n]/x[n +

1]

(1.8)

where Yd[n] is the desired output value.

The EWMA controller provides good control for processes which have small variations over time. Stability for the single-input single-output (SISO) and multiple-input multiple-output cases are well understood and the controller has been shown to be stable over

a large range of model mismatch [16,12]. In addition, the EWMA controller is designed

around a statistically based filter which can be tuned to a given process (i.e. filter noise in

the best possible way while minimizing errors due to real changes in the process), and

methods exist for determining the optimal EWMA weight [12,30,34]. These works have

demonstrated that the performance of the EWMA controller in response to process shifts

and drifts while minimizing the response due to noise is quite good. This is especially true

for systems which have slow dynamics buried in large amounts of noise. For example, the

results of an EWMA controller used to control the deposition thickness of the sputter deposition process above are shown in Figure 1.3. We see the continual adjustment to the pro-

23

6400-

3cy

630- - - - -"- "-- - -"- -'- -"- - - - '-'-- -"-"'-- - - - - - - - - - - - -

6300

2cy

6200

00-

6200 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

G

*

" 61500 - - - - - - - - - - - - - - -.- - - - !- - -- - - - - -

-- - - - - - -

I-I

0

0

S5900------------

5700

--

r-- - - .. -.- .. ..- -

-- -- -- -- -- -- -- -

10

0

5600 L

-------

.. .. ,. 4.. .. .. ..

IIJ

5

.. .. ,.- ..

1

10

0

15

------

.. .. . ..-. . . . .....

25*

20

25

.

.

-a

-3(y

30

Run #

Figure 1.3: EWMA control of a drifting process.

cess results in tighter control of the process (e.g. there are fewer points outside the two

sigma limits).

1.2 An Introduction to CMP

This section outlines some fundamentals of the CMP process before we move on to

discussing a few of the basic issues involved with controlling the CMP process in the next

section. We begin by discussing some basics of the "back-end" manufacturing of integrated circuits (ICs), where CMP is most widely utilized. By back-end, we mean the process technology and steps above the layers of metal and dielectric materials that are used

in the formation of the electrical interconnections between the active components of a circuit (e.g. transistors, as formed in the "front-end" processing). As shown in Figure 1.4, the

interconnect is manufactured by depositing thin films of materials, and selectively remov-

ing or changing the properties of these materials in certain areas. A new "level" of thin

24

film is deposited on top of old films and the process is repeated many times until the interconnect is complete. The goal of the CMP process is to planarize step heights caused by

the deposition of thin films over existing non-planar features, so that further levels may be

added onto a flat surface. This process is outlined in Figure 1.4.

After transistors are formed on the silicon substrate, a pre-metal deposition (PMD) of

dielectric material is laid down, and contacts to the underlying devices are made in the

PMD layer. This via formation often includes a metal CMP process, which is not specifically discussed in this thesis. Following this, the Metal 1 deposition occurs, followed by

patterning and removal of the Metal 1 layer to create the Metal 1 lines. This step is followed by the deposition of an interlevel dielectric (ILD) layer. The patterned metal lines

leave a non-planar surface on the ILD 1 layer. The CMP process is used to planarize this

surface, so that interconnecting metal holes may be etched and filled with material (Via 1),

and the Metal 2 connecting lines may be deposited and patterned. This proceeds to higher

level metals until the circuit is complete. Current generations of ICs have up to seven layers of metal circuitry [43].

The dielectric CMP step in this sequence is critical to determining the performance of

the device, as well as the defectivity rate of the circuit. Without the planarity achieved by

CMP, several problems could occur. First, changes in the vertical height of the surface profile make optical patterning using photolithography difficult. The extremely small feature

sizes require very tight focusing of the light. Any changes in the vertical height in different

regions within the device will cause changes in the focusing and, hence, the sizes of the

features. This lithographic depth of focus limitation results in extremely tight requirements on the planarity of the wafer surface. If these requirements are not met, it could

25

up areas

down areas

stepA

height

ILD 1

Metal 1

a) Cross-sectional diagram of a pre-CMP

interlevel dielectric on top of metal lines.

ILD 1

Metal

1

b) Cross-sectional diagram following CMP.

ILD 2

mtal 2

eVia

1

Eetal ID

c) Cross-sectional diagram following CMP,

and application of Metal 2 and ILD 2.

Figure 1.4: Schematic application of the CMP process in interconnect formation.

result in large variations in the sizes of the metal lines and interconnects, and lead to a degradation in device reliability and performance. Non-planar surfaces can also cause faults in

the circuit as a result of metal depositions from different levels of metal making unin-

26

tended contact. This happens when the metal interconnect holes are etched over the edge

of a step in a non-planar surface. The hole is then etched through the ILD to the underlying

layer, and filled with metal, causing an unintended short between levels. Therefore, the

planarization of ILD layers is critical to the performance and yield of current and future

generation devices. In particular, as device sizes continue to decrease and the number of

metal layers continues to increase, the importance of surface planarity and CMP will also

continue to grow. Future interconnect technology is moving to copper and damascene processes [2-3]. While the details of the process differ, similar demands are placed on good

control of planarity in metal CMP. In Addition, the use of CMP to form shallow trench isolation structures also requires extremely good control planarity in dielectric polish.

In traditional CMP processing, as illustrated in Figure 1.5, the wafer is held in a wafer

carrier and pressed face-down onto a polishing pad, which is affixed to a rotating platen. A

slurry with abrasive material (e.g. silica particles of size 50-100nm) held in suspension is

dripped onto the pad during polishing. The carrier and platen rotate at variable speeds, typically on the order of 30 rpm. CMP tools differ in many aspects, including the number of

platens, the number of polishing carriers per head, the size of the pad in relation to the

wafer size, and rotary versus linear polishing mechanisms.

Slurry Feed

Wafer

Carrier

Platen

Platen

Slurry Feed

Top View

Side View

Figure 1.5: Chemical-mechanical polishing tool configuration.

27

As shown in Figure 1.6, the CMP process preferentially removes material from raised

areas on the surface of the wafer through a combination of mechanical and chemical

action. In dielectric CMP, the chemical action is thought to serve two purposes: a) to

soften, or hydrolyze, the surface of the dielectric material so that the soft pad and slurry

particles can abrade away the surface, and b) to keep particles from agglomerating in the

slurry. Recently, alternative slurries (e.g. CeO 2 particles) and slurry-release mechanisms

(e.g. fixed-abrasive pads) have been reported to exhibit very different behavior [44-45]. In

this work, we focus on conventional oxide polish systems. The preferential removal rate of

the raised areas is thought to be due to the distribution of pressure of the CMP pad on the

raised areas features [46-47], and in particular is related to the density and relative height

of the features, as shown in Figure 1.6 [47]. Dense features tend to support less force per

unit area, because the force of the pad rests on a greater amount area. In contrast, regions

with a significant amount of down (or open) area, have the same force supported by less up

area.

*flMA

7~FkJ7~J\

Metal 1

ILD 1

LJ77Surry

CMP Pad

a) The CMP pad in contact with features.

Metal 1

ILD 1

S lu rry

msamaa

......

...

CMP Pad

.

b) The CMP pad supported by far away (on the order of mm) features.

Figure 1.6: Diagram of pad, slurry, and surface interactions.

28

1.2.1 Blanket Wafer Performance Metrics

The performance of the CMP process is gauged by several different metrics. Although

the process is aimed at reducing the step height on wafers with "patterned" features, several metrics of the polishing of "unpattemed" blanket sheet film wafers are also typically

used. In particular, the removal rate (RR) of material on blanket sheet film wafers is often

used to judge how quickly a process will remove step heights on patterned wafers. Processes with higher removal rates are generally considered better. The RR is determined by

measurement of the oxide film thickness before and after polishing at each of several sites

on the wafer (see Figure 1.7 for two examples). A typical removal rate profile for a blanket

wafer is shown in Figure 1.8, and the resulting post-polish thickness profile is shown in

Figure 1.9. The "removal rate" metric most often used is the average of the amount

removed at each site, divided by the fixed polish time. Differences between polish rates at

the center and edge of the wafer (e.g. "bulls-eye patterns" as seen in Figure 1.8) may arise

due to wafer asymmetry (e.g. wafer flat), non-constant relative pad velocity from the edge

to the center, non-uniform slurry and by-product transport under the wafer, wafer bowing

due to pressure or tool design, or machine drift (with tool or pad age) of any of these

parameters. As a result, the uniformity of the polishing process across the surface of the

+ +

Q

+

+

+

+

+

++

+

+

+ +2

++

+

+

+

+

-6 mm

exclusion

edge

ede+

+

+

49 point sampling pattern

+

25 point sampling pattern

Figure 1.7: Blanket wafer measurement sampling patterns.

29

5000

.24000

3000

S20000

- -.-

1000.

100

50

100

0

-50

-50

y location (mm)

0

50

x location (mm)

Figure 1.8: Blanket wafer removal rate profile. The surface is an interpolation

based on the measured points, which are indicated by the stars.

10000-

8000

-

C 5000 --00

50

100

50

50

0

-50

-50

y location (mm)

x location (mm)

Figure 1.9: Blanket wafer post-polish thickness profile.

wafer is also of concern. In order for all devices on the wafer to be polished to the same

amount, the within-wafer non-uniformity (WIWNU) of a polished unpatterned blanket

wafer is desired to be small (typically 5% or less). The calculation of the WIWNU metric

varies in the industry [48]. One common calculation used is the standard deviation of the

30

amount removed (AR) over the sites on the wafer, divided by the average AR over the several sites, times 100. Other approaches include the standard deviation of the removal rate

or post-polish thickness profiles. These two blanket wafer metrics are generally used to

develop CMP processes, as well as to monitor the CMP process on a lot to lot basis. In

addition, particle and scratching tests are also performed on unpatterned wafers. Particles

and wafer scratching caused by CMP can create severe failures in manufactured circuits

[49], and thus must be carefully monitored.

1.2.2 Patterned Wafer Performance Metrics

In order to verify the planarization of step heights within the wafer, the step heights are

measured at several locations within several die (see Figure 1.10 for a typical sampling

pattern). The sites chosen are usually large features which are easy to find and align on the

measurement tool. Typically, measurement of step heights occurs on several bond pad

structures such as that shown in Figure 1.11. The material stack in the raised area is

14000A of Oxide (PETEOS) on top of 230A of Silicon-Ox-Nitride on top of 6000A of

Aluminum on top of the Silicon substrate. The down areas have had the aluminum

removed. A sample step height measurement using a KLA/Tencor P-20 profilometer taken

Figure 1.10: A typical die sampling plan.

31

Figure 1.11: Typical structures used for step height measurement.

across the structures shown in Figure 1.11 is shown in Figure 1.12, for a 19 second polish

time, i.e. before planarity is reached. Figure 1.13 shows a step height measurement for a

53 second polish time, i.e. near planarity. An important value determined from the measurement is the total indicated range (TIR), i.e. the difference between the maximum and

minimum points of the all the steps within the scan.

Recently, the CMP community has been moving toward the measurement and analysis

ZLI 11 H I

3500-

TIR

63000-

2500 :2000 0

1500 -

1000

E

z

100

200

1500

2000

1000 -

500-

10500

1000

Distance (Microns)

Figure 1.12: A typical step height measurement before planarity is reached.

32

120

100

TIR

80.

'4

0

C

$

60

I0

z

20

0

0

500

1000

Distance (Microns)

1500

2000

Figure 1.13: A typical step height measurement near planarity.

of within-die non-uniformity (WIDNU). The post-polish thickness of 25 sites within a die,

averaged over 10 die on a typical production wafer, is shown in Figure 1.14. Here we see a

large amount of variability in the post-CMP thickness within a die. A general metric for

this is the standard deviation of several sites within a single die. However, a significant

amount of work has gone into understanding this variation [50-57], and much of the work

in this thesis will be based on these ideas. We will thus return to this issue again later.

33

7500,

-.

7000

6500

-

60001.

5500

5000

20

20

15

X (MM)

15

5

10

__10

0

Y ()

0

a) Surface plot of the within-die variation, along with

corresponding measurement points.

8500

8000-

7500-

) 7000C

6500-

6000-

5500 -

0

5

15

10

20

25

Site #

b) Two-dimensional plot of the within-die variation.

Figure 1.14: The within-die variation of a typical production wafer.

1.3 An Introduction to CMP Process Control Issues

Several factors make controlling the CMP process particularly difficult. It is often the

case that there is significant drift in the removal rate over the life of a typical CMP polishing pad [10-12]. Figure 1.15 shows the average blanket removal rate using a data from a

25 point measurement similar to that shown in Figure 1.7 over the course of a 600 wafer

34

polishing experiment. The data shown was taken from the last wafer in the lot. We can see

that the blanket rate has a fairly significant drift; an 11% decrease over the lifetime of a

typical pad. This is also true for the patterned removal rate. Figure 1.16 shows the average

removal rate measured at a single site on an evenly spaced grid of 22 dies of a test device,

similar to a typical production wafer, plotted over the course of the same experiment.

4000

3500F

0

E

0

3000

2500

0

cc

2000

0

I 5U(.

10

20

30

40

50

60

70

80

90

100

Lot #

Figure 1.15:. Average removal rate of blanket sheet film PETEOS wafers.

7500

2

0

7000

E

6500

V

6000

C0

5500

Figure 1.6

10

20

30

40

50

60

70

80

90

100

Lot #

Average removal rate of patterned PETEOS wafers.

35

Again, the data is taken from the last wafer of the lot. Note that there is a corresponding

7% decrease in the average patterned removal rate over the pad lifetime. These decreases

in removal rate have been the focus of most of the initial work in controlling the CMP process. Although the drift is small, if it is not correctly controlled it can lead to significant

differences in the actual average post-polish thickness and the desired average post-polish

thickness.

In controlling the CMP process, the within-wafer non-uniformity on blanket test

wafers is also frequently monitored. However, the WIWNU varies very little over the life a

typical CMP pad, assuming well-designed pad conditioning practices. As shown in Figure

1.17, the WIWNU is fairly consistent over the life of a pad, and the exact value depends on

the particular tool and the component quality (e.g. carrier flatness). On the other hand, the

WIWNU is often the reason the tool is brought down for maintenance. In normal polishing, there is a fall-off in the removal rate near the edge of the wafer. This fall-off is usually

in the 3-6mm edge-exclusion region (shown in Figure 1.7) which is not included in the

04

30

0

10-

z

C

E

E 1015

0

216

0

0o

0_

40

7'0

so

90

100

Lot #

Figure 1.17: Within-wafer non-uniformity of blanket sheet film PETEOS wafers.

36

WIWNU. As the polishing pad ages, this fall-off region moves in closer to the center of

the wafer. The outer measurement points then become significantly different from the

other measurements, and the WIWNU quickly increases. Once the WIWNU exceeds a

certain limit, the tool is brought down, the pad is changed, and maintenance is performed

on the carrier head.

In addition to the removal rate and WIWNU, step height measurements are also taken.

As mentioned above, the step-height is measured on a fixed feature on each particular

device. Because these measurements are time-consuming, only a single step-height measurement on a single feature on a single die of a single wafer in a lot is typically taken. If

the step-height has not been removed to less than a certain level, then the wafers are reworked, meaning they are put back on the polisher for additional polishing. However, care

must be taken to avoid over-polishing. As we saw in Figure 1.14, the within-die non-uniformity can be large, and over-polishing can result in the low areas on the device being

completely removed. As a result, step-height measurements are frequently used only as a

spot check on the process during production, although they are used heavily in the process

development stage (in order to ensure a process is achieving a certain degree of planarization).

1.4 Summary

In this chapter, we outlined the need for chemical-mechanical polishing as a means for

dielectric planarization in the manufacture of integrated circuits, and described the importance of controlling the CMP process in a production setting. Process control in the semiconductor industry has progressed from basic statistical process control to run by run

37

feedback control systems. Various metrics and goals must be achieved in the CMP process, including: removal rate, within-wafer non-uniformity, step-height, total indicated

range, within-die non-uniformity, and wafer-to-wafer non-uniformity. A number of difficulties exist in controlling the CMP process, including the drift in the polish characteristics of blanket and patterned wafer performance metrics over time, and the challenge of

control given a mix of device types on the same tool.

In the next chapter, we turn our attention to controlling the CMP process using the

EWMA controller outlined in this chapter. We will discuss factors that are important to a

production control solution, including the use of integrated metrology and a simple model

update strategy. We will also begin to discuss some of the difficulties in effectively measuring, monitoring, and controlling patterned wafers in the CMP process.

38

39

40

Chapter 2

Control of a Single Device Using On-Line

Metrology

In this chapter, we take the first steps in developing a comprehensive control strategy

for the polishing of patterned wafers in CMP. The previous chapter outlined the basics of

process control, CMP, and the issues involved with controlling the CMP process. This

chapter aims to expand on these topics and begins to cover the details of implementing

CMP run by run process control in a production setting.

There are at least four major issues involved with an implementation of a run by run

control system for use in a production environment: quality, cost, flexibility, and ease of

use. This chapter outlines the use of an EWMA run by run control system with integrated

metrology to control the average post-polish thickness of patterned wafers. An integrated,

or on-line, metrology tool resides on the processing equipment and performs measurement

after the wafers are processed, but before they are unloaded from the tool. The frequent

measurements provided by integrated metrology, combined with proper controller tuning,

result in high quality control of the post-polish thickness. In addition, the automatic measurement of the post-polish wafers and the relatively simple control algorithm provide

maximum ease of use. The simplification of processing using on-line metrology and the

reduction in run to run thickness variation from improved control result in a reduced cost

for the CMP process. However, the methodology provided within this control framework

is limited in flexibility. We will demonstrate this in the following chapter, where we

41

present a comprehensive control framework based on the concepts presented in this chapter.

As stated above, our purpose is to demonstrate run by run control of the average postpolish thickness of patterned wafers using the relatively simple EWMA control algorithm

in conjunction with an on-line metrology system. We will demonstrate that such a system

provides quality control of the average thickness of a single site over multiple dies of a single type of patterned wafers, i.e. a single type of device, with an easy to use system that

reduces cost. First, we present a study of the quality and reliability of an on-line metrology

tool for CMP. This is necessary to insure the quality of our measurements before using

them for control. Second, we outline the cost benefits of an on-line metrology tool, used in

conjunction with a run by run controller. Finally, we demonstrate that the lot to lot drift in

a polishing tool may be eliminated by using the simple (i.e. maximum ease of use)

EWMA control algorithm presented in the previous chapter. We show that, when this relatively simple controller is correctly tuned and frequent measurements are enabled by online metrology, the controlled thickness using this simple control methodology is similar

to or better than that reported in the literature, including those using more complex

approaches.

2.1 Evaluation of On-Line Metrology for CMP

Before an on-line metrology tool can be used for process monitoring and control, the

repeatability and reliability of the tool must be assessed. In addition, some understanding

of how measurements from the on-line tool relate to those of current ex-situ metrology

tools is needed. In this section, we discuss the evaluation of a NovaScan 210 on-line

42

metrology tool from Nova Measuring Instruments, performed on an IPEC 472 CMP polisher.

As shown in Figure 2.1, the on-line metrology tool resides on the polishing tool. Processing begins by moving the wafer from the load station to the primary polishing table.

After polishing, the wafer is normally buffed on a soft felt pad with de-ionized water. After

the buffing, the wafer is loaded into the on-line measurement tool before being placed in

the unload station.

The measurement process for patterned wafers is shown in Figure 2.2. Standard exsitu metrology tools first physically align the position and orientation of the wafer before

performing any software alignment and measurement. However, the on-line tool does not

perform any physical alignment of the wafer, but only performs a software alignment routine to determine the location and orientation of the wafer. Once the position and orientation of the wafer are established, the measurement process proceeds to each specified die.

Within each die, searching begins with the alignment feature (a particular feature on each

Wa.0 F-eed

Sl rry Feed

Wafer

Load

Wafer

Load

On-line

Metrology

Figure 2.1: Polishing sequence with on-line metrology.

43

Wafer Load

8.1A

Software Wafer Alignment

4.3A

Die Alignment

Recognition

Measurement

Site

Recognition

o.5A

Repeat for Each Site

Repeat for Each Die

Figure 2.2: The on-line pattern recognition system.

type of wafer chosen by the user to orient the software with a specific die on the wafer).

Once the alignment feature is located, measurement proceeds to each site. An optional

alignment of each measurement site is performed and a final adjustment to the measurement position is made before the measurement of the site is taken. Measurement then proceeds to all remaining sites within that die. Once the measurement of the sites within the

die is complete, the tool then moves to the next die and begins searching for the alignment

feature of that die. The process then repeats until all dies are measured.

The measurement process is a spectraphotometry process, whereby the intensity of

light of varying frequency is measured to obtain a reflected spectrum. The spectrum is

matched to internal model spectra within the tool. The thickness parameters of the model

are varied, from which the thicknesses of the specified layers is determined.

44

2.1.1. Measurement Repeatability

There are four sources of variability in the measurement process: the variability due to

a) the initial wafer alignment software routine, b) the die stepping and alignment, c) the

site alignment, and d) the actual measurement process. These variances are in a form

referred to as nested variance. The variance of the measurement process is nested within

the variance due to the site alignment which is nested within the variance due to the die

stepping and alignment which is nested within the variance due to the software alignment.

This four-level nested variance structure results in a single sample site measurement having the form

Xijkl -

Wi+D()

+ Sk(ij) + Ml(ik)

(2.1)

where

a 2)

(22

(2.2)

,

aD2

(2.3)

), as2

(2.4)

MI(ijk) ~ N(O, am2)

(2.5)

Wi ~N(p,

Dj(j) - N(

Sk(ij) - N(g

1

This structure has several implications when measuring the variability of the measurement process. In fact, the structure in this general form is extremely complex, and many

works have outlined methods for finding the terms in this structure [50-51, 58-63]. If, for

example, we assume that g, 9i, and giU) are all zero, then the variance of an individual

measurement will be

OT2 =aW2 +

a|

=a

D2 +

+aD

+

s2 +m2

2

M

The variance of the sample average of a wafer, under these assumptions, would be

45

(2.6)

aA

2

=

aW+

1

IUD

2

2

1

2

+Jjas +DSaMG(.7

where D, S, and M are the number of dies, sites, and measurements, respectively. With

this in mind, we now proceed to identify the components of variance in the on-line metrology tool.

The variability of the actual measurement process, am2 , was estimated by repeatedly

measuring the same point on a single wafer, without any physical movement of the wafer

or mechanisms (site alignment or die alignment). This eliminates all the components of

variance except

MI(ijk).

This process was repeated at two locations on the wafer, each with

25 repetitions, to estimate am2 , which is often referred to as the "precision" of the measurement process. The average of the sample standard deviations of these measurements

was 0.5A, and is shown in its corresponding location in Figure 2.2. By averaging these

values, we are assuming that the variation of two sites at different locations are white,

meaning that each site has the same am2

The variation added by the site-to-site movement and the die-to-die movement cannot

be measured individually on this tool, because it cannot be set to perform multiple site or

multiple die measurements without including the software wafer alignment. The withinwafer measurement variation, i.e. that including a2, as , and am2 , was determined as follows. A single patterned wafer was placed on the measurement stage. One site on five die

across the wafer was measured. The standard deviation of the five sites was calculated for

25 repetitions, without movement of the wafer on the stage. It is possible that there is some

wafer variation included in this, because each repetition includes a software alignment.

However, we will neglect this because we believe most of the variation comes from varia-

46

tions in the orientation and position of the wafer on the measurement stage, and this was

not included since the wafer did not move on the stage during the measurement. The average of these 25 five-die standard deviations was determined to be 4.3A, and is also shown

in its corresponding location in Figure 2.2.

In our nested variance structure, each measurement we obtain is at the die-level. In

particular, each measurement consists of one measurement in one site in one die. Thus,

only the D](i),,

Sk(ij),

and MI(Jik)

terms contribute to the variance of each measurement.

Some assumptions on the means of these terms are necessary. Since we have only one

wafer, and since there is only one site and one die in each measurement, we can assume

one mean for all the measurements. Therefore, the average of five of these measurements

would have a variation of

(WA2

=

1aD

+(

5

)()as

+ ( 5 )(

)( 1 )2

=

a2+

as2+ am2)

(2.8)

In addition, since we have only one mean for all the components, these will drop out in the

calculation of the standard deviations. Thus the sample average of the standard deviations

given above is an estimate of the variation from the die variation, the site variation, and the

measurement variation,

DT22= aD

D22+ + aS2 + aM2

M2

cTDT

(2.9)

Note that we may have possibly compounding variations here. We are assuming that the

variation determined from the sample standard deviation of the die measurements is due to

the metrology tool, because we are using the same wafer which is very flat across the

raised features. In fact, if there is within-wafer variation on this wafer, then the standard

deviation of the five die measurements will contain this variation, and should be attribut-

47

able to the wafer, not the metrology tool.

The variability including the measurement, site-to-site, die-to-die, and wafer alignment variability was measured by repeating the previous process, but rotating the orientation of the wafer in-between each measurement. This average variability was determined

to be 8.1A, which is also shown in Figure 2.2. Again, we have assumed that the mean of

the wafers, pi, is fixed over all wafers, because the same wafer was used for all measurements.

We found the repeatability of the measurement process, i.e. 8.1A, to be very good,

considering that the average wafer to wafer variation of blanket wafer polishing is roughly

100A to 300A. The sources of variability are all less than 10,

and some of this may be

due to the wafer itself as mentioned above. This suggests that the repeatability of the

metrology of the tool meets the requirements for CMP. Section 2.1.3 will discuss the variation contributed by wafer loading, small amounts of slurry, and post-polish wafer clean-

ing.

2.1.2. Reliability

The reliability of a metrology tool in a production environment is extremely important.

In light of this, we performed two reliability tests of the on-line metrology tool. In our first

experiment, one site on five dies was measured on 100 wafers with the intention of testing

the alignment success rate as well as the die-level pattern recognition success rate. Our

experiment results show a 100% success rate in wafer alignment. Only one in 500 sites

was not found (most likely due to a bubble), corresponding to a 99.8% success rate. We

performed two additional experiments which measured one site in 22 dies on 24 wafers.

48

Again we found a 100% wafer alignment success rate. Four of 1056 sites were not found,

resulting in a 99.6% success rate.

The reliability of the on-line metrology tool during the run by run control experiment

we outline later was also very good. There was one failure in 96 wafer alignments, a success rate of 99%. The site alignment success rate was 99.7% (7 failures in 2112 measurements). These site-not-found (SNF) errors are generally caused by bubbles in the water

between the wafer and the measurement window. However, it was found that the pattern

recognition trained for this layout had problems finding a site on the far right of the wafer,

which could be due to an inability in the die-level or site-level alignment routines to compensate for inaccuracies in the stepping distance or the wafer alignment.

2.1.3. Correlation with Ex-Situ Metrology

We would also like to understand how these measurements correspond to ex-situ measurements. One site on 22 dies on two sets of patterned wafers were measured on both the

NovaScan 210 on-line metrology tool and on a KLA/Tencor UV1280 ex-situ metrology

tool. The first set consisted of pre-clean pre-polish wafers measured on both tools. The

second set were pre-clean post-polish wafers when measured on the on-line tool and postclean post-polish wafers when measured on the ex-situ tool. Care was taken to set up the

measurement parameters on both tools. These parameters include pattern recognition,

optical properties of the materials being measured, die stepping distances, and site measurement locations. Both the tools are spectraphotometry tools, and thus we expect similar

results.

The on-line and ex-situ measurements from pre-clean pre-polish wafers are linearly

49

correlated with a correlation coefficient of 0.98. The on-line values are, on average, 47A

higher than the ex-situ values. The standard deviation of the errors from this linear fit

(which we will refer to as the spread) is 12A, and the range of the spread is 48A. These