QDs in semiconductor nanowires

advertisement

QDs in semiconductor nanowires

Lars Samuelson

Lund University, Solid State Physics/the Nanometer Structure Consortium

http://www.nano.ftf.lth.se/ Email: lars.samuelson@ftf.lth.se

What types of quantum devices do we talk about?

What may be the advantages of using nanowire techniques?

How do we grow semiconductor nanowires by VLS-mode

& what quality of materials and structures can we achieve?

Examples of quantum-dot devices achieved by August 2004

QDs in semiconductor nanowires

Lars Samuelson

Many colleagues and students have contributed to this work, e.g.:

Jonas Ohlsson, Ann Persson & Sören Jeppesen in CBE-growth

Werner Seifert, Magnus Borgström & Kimberly Dick in MOVPE

Knut Deppert, Martin Magnusson, Martin Karlsson & Brent Wacaser

in aerosol nanoparticle technology

Reine Wallenberg, Torsten Sass & Magnus Larsson in TEM studies

Anders Mikkelsen & Edvin Lundgren in cross-sectional STM

Nicolay Panev, Niklas Sköld & Patrik Svensson in PL studies

Mikael Björk, Claes Thelander & Adam E. Hansen in device processing

and studies of tunneling and single-electron devices

Thomas Mårtensson, Patrick Carlberg & Lars Montelius in array formation

What kind of progress can we expect in the future?

QDs in semiconductor nanowires

Lars Samuelson

- and with financial support from:

Hongqi Xu, Martin Persson, Mats-Erik Pistol & Carina Fasth

in electronic structure and transport theory

QDs in semiconductor nanowires

Lars Samuelson

What types of quantum devices do we talk about?

Devices with their functionality based on controlled design

and performance based on quantum phenomena, such as:

– One-dimensional structures with quantized conductance

– Tunneling via quantum dots resulting in 1D–0D–1D character

– Incorporation of optically active single or coupled QDs

QDs in semiconductor nanowires

Lars Samuelson

What may be the advantages of using nanowire techniques?

TOP-DOWN fabrication of 1D devices

A top-down approach to making one-dimensional quantum

devices. like resonant tunneling via quantum dots. Method

pioneered by Randall and Reed at Texas instruments in the

late 1980s. However, rather unsatisfactory device properties

due to fabrication induced damage and poor lateral control.

– Extremely small devices fabricated via top-down methods

are often dominated by damage induced during processing

– while nanowires form in a self-organized fashion, with atomic

perfection in lateral direction as well as in the growth direction

1

Comparison between top-down & bottom-up fabrication of complex structures

Alternative No. 1: TOP-DOWN fabrication

Start with a block of wood and carve a small

wooden mini-tree with trunk and branches.

Alternative No. 2: BOTTOM-UP fabrication

Plant a seed and control bottom-up growth

of a perfectly functioning Bonsai tree.

Formation of size-controlled GaAs nanowires using aerosol

gold particles as seeds for vapor-liquid-solid (VLS) growth

Deposition of

size selected

catalytic gold

aerosol nanoparticles

Creation of

an alloy between gold

and gallium

(close-up)

VLS growth

of nanowires

using e.g.

CBE, MBE

or MOVPE

R. S. Wagner, Whisker Technology, Wiley, NY, 1970

K. Hiruma, first growth of nanowires in early-mid 90’s

5 nm

Low eutectic

temperatures

Au aerosol particle

- Au/Ga 339°C

- Au/In 454°C

InAs <111>

10 nm

30 nm

2

HRTEM image of a 30 nm wide GaAs nanowire

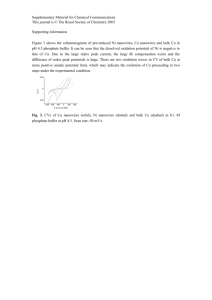

Growth occurs in most cases in the <111>B-direction, as also found

in the early work of Hiruma et al., J. Appl. Phys. 74, 3162 (1993).

We also see stacking-sequence related defects and extended

regions of the wires with either cubic or hexagonal structure.

QDs in semiconductor nanowires

Lars Samuelson

What may be the advantages of using nanowire techniques?

– Extremely small devices fabricated via top-down methods

are often dominated by damage induced during processing

– while nanowires form in a self-organized fashion, with atomic

perfection in lateral direction as well as in the growth direction

– Top-down fabrication, when pushed down to the 10nm level,

require extremely expensive fab-investments, while complex

and high-performance nanowire devices may be fabricated

via simple patterning techniques in combination with selfassembly in the device formation

Growth from patterned catalysts

Tilted view SEM micrograph of the monolithic Si

NIL stamp used. The stamp was fabricated from

a one-inch Si wafer using Cr as dry etching mask.

SEM micrographs of NIL-defined InP nanowire arrays.

The nanowires are 1.5 m long, with a diameter of

290 nm. The dimensions are chosen for a photonic

crystal structure operating at wavelengths of 1 m..

InP nanowire array grown by MOVPE

(metal-organic vapor phase epitaxy)

InAs nanowire arrays grown by CBE

(chemical beam epitaxy)

3

To appear in October-issue of NanoLetters

Diffusion length of In-species on InAs

(111)B is 650nm, independent of wire

Diameter, and on {110}-facets >10m

Formation of heterostructure interfaces between lattice mismatched materials, e.g. InAs/GaAs (7%) & InAs/InP (3.5%):

a comparison between 2D epitaxial growth and wire growth

Lattice mis-match

Growth by

2D epitaxy

Wire geometry

1D wire growth

SK-islands &

dislocations

Radial strain

relaxation

Switching of growth species

in an optimal fashion allows

abrupt interfaces to form

High-resolution TEM

images of 40 nm InAs

nanowire containing a

series of InP barriers,

ranging in thickness

from 2-3 mono-layers,

8 nm, 28 nm to 100 nm.

Growth direction <001>.

TEM-images by T. Sass

and L.R Wallenberg

From Björk et al., ”Onedimensional heterostructures in semiconductor

nanowhiskers”,

Appl. Phys. Lett. 80,

1058 (2002)

QDs in semiconductor nanowires

Transport in InAs nanowires

Device configuration

Lars Samuelson

What types of quantum devices do we talk about?

What may be the advantages of using nanowire techniques?

How do we grow semiconductor nanowires by VLS-mode

& what quality of materials and structures can we achieve?

Examples of quantum-dot devices achieved by August 2004

What kind of progress can we expect in the future?

Voltage (mV)

4

Increasing the size of the InAs dot

RTD

EF < Level splitting

Resonant tunneling diode

RTD effects dominate

EC=e2 /C

EF

~ 15 nm

~ 15 nm

InAs

InP

EF > Level splitting

SET

Single-electron transistor Coulomb blockade

effects will dominate

EF

~ 100 nm

Electrical characterization

EC=e2 /C

~ 100 nm

InAs

InP

100 nm

Modelling of the SET

VSD (mV)

20

0

±20

0

-20

0.2

20 0

0

-20

-0.97

VG (V)

-0.70

To appear in September-issue of NanoLetters

HAADF of DB-RTD

(Reine Wallenberg & Magnus Larsson, nCHREM)

EC constant the shape of

the confining

potential is

unaffected by

the gate voltage

(in contrast to

GaAs/AlGaAs)

HAADF: High-Angle Annular Dark-Field (in STEM)

5

QD based single-photon

Few-particle configurations in a single QD

Single-photon emission from a single QD

sources for quantum information technology

MOVPE-grown co-axial GaAs nanowires with shells of AlGaAs

Ga

In

Ga

Ga

20 nm

InAs

GaAs

AlGaAs

10 W/cm2 180s

Luminescence Intensity / arb. units

GaAs

1,3

1,4

1,5

1,6

1,7

1,8

1,9

2

Energy / eV

QDs in semiconductor nanowires

Lars Samuelson

Recent progress in the formation of complex 3D

Structures using multiple branching into tree- &

forest-like structures

A forest of nanotrees

with multiply seeded

trunks, branches and

leaves, with the entire

tree being single-crystalline and monolithic.

Each level of branches

is seeded by Au aerosol

nanoparticles, allowing

control of:

– diameter

– length

– composition

including formation of

heterostructures inside

branches or at branchleaf interfaces.

Kimberly Dick et al.

6

Top view

Au aerosol particles

deposited on <111>Boriented nanowires

(low density)

Side view

To appear in October-issue of NanoLetters

Epitaxial III-V Nanowires on Silicon

Thomas Mårtensson, C. Patrik T. Svensson, Brent A. Wacaser, Magnus W. Larsson,

Werner Seifert, Knut Deppert, Anders Gustafsson, L. Reine Wallenberg, and Lars Samuelson

Ideal epitaxial nucleation and controlled oriented growth of III-V

semiconductor nanowires on silicon substrates has been achieved.

Efficient room-temperature generation of light on Si is demonstrated

by the incorporation of double heterostructure segments in nanowires.

We expect that advanced hetero-structure devices, such as resonant

tunneling diodes, superlattice device structures and heterostructure

photonic devices for on-chip communication, could now become available

as complementary device technologies for integration with Si.

7

To appear in October-issue of NanoLetters

Growth of epitaxially nucleated

and vertically growing GaP nanowires on Si (111)-substrates.

(A)

A 45° tilt SEM micrograph of GaP

nanowires growing vertically from the

Si (111) surface in the [111] direction.

The wires were grown using 40 nm

Epitaxial III-V Nanowires on Si

To appear in October-issue of NanoLetters

Formation of ideal GaP – GaAsP – GaP

double heterostructures in GaP nanowires grown on silicon substrates.

The luminescence from these nanowires

is as bright as from those grown on GaP

substrates and show negligible thermal

quenching up to room-temperature.

seed Au nanoparticles. Top wire diameter is close to 40 nm.

(B) Top view of the same sample

showing the perfection in the vertical

alignment. Scale bar 1 m.

(C) HRTEM image of the Si substrate

– GaP nanowire interface. The crystal

directions from the Si substrate are

transferred to the nanowire.

Scale bar 10 nm.

QDs in semiconductor nanowires

What kind of progress can we expect in the future?

Since nanowires can form ideal RTDs and SETs, as well as

single quantum dot emitters, single photon on demand devices

may soon become available using nanowire techniques

Nano-photonic light-sources on silicon and, in general, heterostructure devices on silicon can be expected, based on epitaxial

quality III-V nanowires & heterostructures now realized on Si

With the development of a wrap-gate technology for nanowires, high-performance FET devices can be fabricated

Nanowires are likely candidates to give ideal 1D superlattices

8