k A C t

advertisement

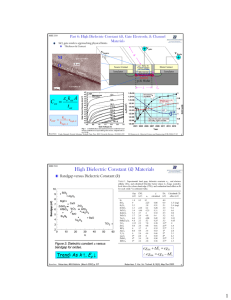

MSE 310/ECE 340 Electrical Properties of Materials Part 6: High Dielectric Constant (k), Gate Electrode, & Channel Materials SiO2 gate oxide is approaching physical limits Thickness & Current +V gate VSource VDrain W M + poly-crystalline Si O Source Contact Insulator S n++ Poly Si Gate Contact or Electrode Drain Contact Insulator SiO2 - Gate oxide n+source - - - - - - - - - - - - - - n+drain channel p-Si Wafer Crystalline Si Cox t EOT Knowlton L tox o kox A tox kox thigh k khigh k Frank, Dennard, Nowak, Soloman, Wong & Taur, Proc. IEEE Circuit & Devices , 89 (2001) 259 MSE 310/ECE 340 Electrical Properties of Materials M. Houssa et al., Materials Science and Engineering R, 51 (2006) 37-85 1 High Dielectric Constant (k) Materials Bandgap versus Dielectric Constant (k) e Hik Ec e Si Trend: As k ↑, Eg ↓ Knowlton Robertson, MRS Bulletin (March 2002) p. 217 e Hik e Si Ec Robertson, J. Vac. Sci. Technol. B, 18(3), May/Jun 2000 2 1 MSE 310/ECE 340 Electrical Properties of Materials High Dielectric Constant (k) Materials Band Offsets: High k on Si Aspects to Consider: 1. Eg 2. Ec & Ev 3. meff Recall in Barrier Region: e kx So: J * e 2 kx 2meff (V Ee ) k k meff meff , J e Hik Ec e Si e Hik e Si Ec Knowlton Robertson, MRS Bulletin (March 2002) p. 217 MSE 310/ECE 340 Electrical Properties of Materials J g (k )T k f leftSide E f f rightSide E f dk 1 E pˆ & g where p m g & g k m 3 High Dielectric Constant (k) Materials Band diagrams of MOS – compare SiO2 to high k materials SiO2; κ~3.9 HfO2; κ~25 PbZr(0.53)Ti(0.47)O3 κ~200 Low S/C doping Knowlton Southwick & Knowlton, IEEE TDMR, 6(2), (2006) 136-145 4 2 MSE 310/ECE 340 Electrical Properties of Materials High Dielectric Constant (k) Materials Need to consider the Thermodynamics of the materials system Ellingham diagram G –vs- Temperature The more negative G is, the more stable the materials system is. Example: Grow Y2O3 on Si, Si will steal oxygen from Y2O3 to form interfacial layer (IL) of SiO2. Why? Y 2O 3 SiO2 Al2O3 GSiO2 GY2O3 SiO2 more stable than Y2O3 R. DeHoff, Thermodynamics of Materials, (Prentice Hall, 1996) Ch. 11, fig. 11.4 Knowlton MSE 310/ECE 340 Electrical Properties of Materials 5 High Dielectric Constant (k) Materials Interfacial layer (IL) of SiO2 Present for HfO2 EOT WRT tS i O 2 & tH f O 2 TiN 3.5 3 SiO2 IL EOT nm HfO2 2.5 2 1.5 1 0.5 0 Crystalline Si Channel 0 2 4 6 8 10 tH f O 2 nm tox ,eff tox , physical Knowlton kox khigh k 12 14 thigh k 6 3 MSE 310/ECE 340 Electrical Properties of Materials High Dielectric Constant (k) Materials EOT: 7 nm HfO2 & 1nm SiO2: EOT ~ 2 nm d 2V d ok dx 2 dx 8 nm HfO2: EOT ~ 1.25 nm Southwick & Knowlton, IEEE TDMR, 6(2), (2006) 136-145 Knowlton 7 MSE 310/ECE 340 Electrical Properties of Materials High Dielectric Constant (k) Materials - NVM Floating Gate NVM Versus SONOS (SiO2-Si3N4-SiO2-Si) NVM SONOS Advantages over Floating Gate: Replace poly-Si floating gate with Si3N4 Stored charge lies in defect (bound) states below Si3N4 conduction band Improved endurance - single defect will not cause the discharge/leakage of carriers Can reduce Thickness of TO Si3N4 thinner than floating gate Poly Si Carriers not “Floating” around Minimizes interaction with neighboring memory cells Thus, can scale down memory cell size BL = Blocking Layer CTL = Charge Trapping Layer TL = Tunnel Layer BL CTL TL Knowlton Todd Wallinger, SONOS Eases Non-Volatile Memory Integration in SoC, Semiconductor International (2007) 8 4 MSE 310/ECE 340 High Dielectric Constant (k) Materials - NVM Electrical Properties of Materials BL CTL TL BL Poly Si CTL TL Floating Gate Flat Band Condition BL TL Poly Si Si Si Energy Band Diagram Energy Band Diagram Si3N4 = CTL Gate stack scaled down in thickness & cell area Knowlton MSE 310/ECE 340 Electrical Properties of Materials Todd Wallinger, SONOS Eases Non-Volatile Memory Integration in SoC, Semiconductor International (2007) 9 High Dielectric Constant (k) Materials - NVM Flat Band Condition BL TL Poly Si Si Si3N4 Energy Band Diagram Gate stack scaled down in thickness & cell area Knowlton Todd Wallinger, SONOS Eases Non-Volatile Memory Integration in SoC, Semiconductor International (2007) 10 5 MSE 310/ECE 340 Electrical Properties of Materials High Dielectric Constant (k) Materials - NVM Multilayer high k dielectric films for memory applications SONOS (poly Si–SiO –SiN–SiO –Si) MANOS (metal–Al2O3–SiN–SiO –Si) Sanghun et al., IEEE TED 52 (2005) 2654.pdf TANOS (Si/SiO2/SiN/A2O3/TaN) Lee et al., Symposium on VLSI Technology Digest of Technical Papers (2006 Knowlton 11 MSE 310/ECE 340 Electrical Properties of Materials Low Dielectric Constant (k) Materials What About Low-k Dielectric Materials? What would they be used for? Cox Knowlton o kox A tox 12 6 MSE 310/ECE 340 Electrical Properties of Materials Engineering a Memory Device – BGE & SP3 Compare and Contrast following Memory Gate Stacks: Stack #: Metal – BL – CTL – TL -S/C Stack 1: TiN–SiO2–Si3N4–SiO2–pSi Stack 2: TiN–Al2O3–Ta2O5–HfO2–pSi Stack 3: TiN–La2O3–ZnO–ZrO2–pSi Knowlton Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 MSE 310/ECE 340 Electrical Properties of Materials Knowlton 13 Engineering a Memory Device – BGE & SP3 Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 14 7 MSE 310/ECE 340 Electrical Properties of Materials Knowlton Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 MSE 310/ECE 340 Electrical Properties of Materials Knowlton Engineering a Memory Device – BGE & SP3 15 Engineering a Memory Device – BGE & SP3 Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 16 8 MSE 310/ECE 340 Electrical Properties of Materials Knowlton Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 MSE 310/ECE 340 Electrical Properties of Materials Knowlton Engineering a Memory Device – BGE & SP3 17 Engineering a Memory Device – BGE & SP3 Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 18 9 MSE 310/ECE 340 Electrical Properties of Materials Knowlton Engineering a Memory Device – BGE & SP3 Soutwick et. al, “An Interactive Simulation Tool for Complex Multilayer Dielectric Devices”, IEEE Transactions on Device & Matls Rel., 11(2), 2011 19 MSE 310/ECE 340 Electrical Properties of Materials MOSFETs – Bandgap Engineering of Channel Consider: Bandgap, mobility, effective mass,lattice matching, quantum confinement of carriers Lattice Constants: aSi = 5.4309 Å aGe = 5.6577 Å Knowlton Cullity, Elements of X-ray Diffraction, 2nd Ed (1978) Appendix 5 From Principles of Electronic Materials and Devices, Third Edition, S.O. Kasap (© McGraw-Hill, 2005) 20 10 MSE 310/ECE 340 Electrical Properties of Materials MOSFETs – Bandgap Engineering of Channel Consider: Bandgap, mobility, effective mass, lattice matching, quantum confinement of carriers Lattice Constants: aSi = 5.4309 Å aGe = 5.6577 Å Cullity, Elements of X-ray Diffraction, 2nd Ed (1978) Appendix 5 Knowlton IBM RJ Antoniadis et al., Continuous MOFET Performance Inc with Scaling - Strain & Channel Matl (2006) MSE 310/ECE 340 Electrical Properties of Materials 21 Part 5: Quantum Effects in MOS Devices Quantization: (cont.) 2D gas in channel SOI Gate-all-around (GAA) MOSFET: Gate-All-Around (GAA) MOSFET is an SOI transistor in which the gate oxide and the gate electrode are wrapped around the channel region. Fabricated using an SOI CMOS process to which two process steps are added a photolithographic step a wet etch step during which a cavity is formed under previously patterned silicon islands. The remarkable features of this MOSFET are that there are two channels (at the top and the bottom of the silicon film, The entire channel area is surrounded by good-quality gate oxide and the gate electrode. Knowlton Colinge & Colinge, S/C Devices 22 11