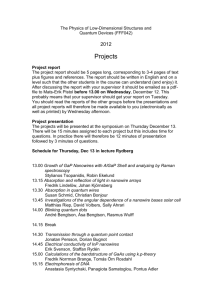

Gate-All-Around Silicon Nanowire MOSFETs: Top-down Fabrication and Transport Enhancement Techniques

advertisement

Gate-All-Around Silicon Nanowire MOSFETs: Top-down Fabrication and

Transport Enhancement Techniques

By

Pouya Hashemi

B.Sc., Electrical Engineering, University of Tehran 2003

M.Sc., Electrical Engineering, University of Tehran 2005

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

at the

Massachusetts Institute of Technology

September 2010

© 2010 Massachusetts Institute of Technology

All rights reserved

Signature of Author ______________________________________________________________

Department of Electrical Engineering and Computer Science

September 3, 2010

Certified by _____________________________________________________________________

Judy L. Hoyt

Professor of Electrical Engineering

Thesis Supervisor

Accepted by ____________________________________________________________________

Terry P. Orlando

Professor of Electrical Engineering

Chair, Department Committee on graduate Students

Gate-All-Around Silicon Nanowire MOSFETs: Top-down Fabrication and

Transport Enhancement Techniques

By

Pouya Hashemi

Submitted to the Department of Electrical Engineering and Computer Science

on September 3rd, 2010 in partial fulfillment of the requirements for the degree

of Doctor of Philosophy in Electrical Engineering and Computer Science

Abstract

Scaling MOSFETs beyond 15 nm gate lengths is extremely challenging using a planar device architecture

due to the stringent criteria required for the transistor switching. The top-down fabricated, gate-all-around

architecture with a Si nanowire channel is a promising candidate for future technology generations. The

gate-all-around geometry enhances the electrostatic control and hence gate length scalability. In addition, it

enables use of an undoped channel, which has the potential to minimize threshold voltage variation due to

reduced random dopant fluctuations. However, there is little known about carrier mobility in Si nanowire

MOSFETs. Because of the different crystal surface orientations, the nanowire sidewalls are expected to

influence carrier transport. In addition, sidewall roughness due to non-ideal lithography and etch processes

can degrade the carrier transport. Technological performance boosters are thus required to enhance electron

and hole transport. Uniaxial strain engineering and maskless hydrogen thermal annealing are investigated in

this thesis to enhance carrier mobility in gate-all-around nanowire MOSFETs.

Uniaxial tensile stress of about 2 GPa was incorporated for the first time into suspended Si nanowire

channels by a novel lateral relaxation and suspension technique. Gate-all-around strained-Si nanowire nMOSFETs were fabricated with nanowire widths in the range of 8 to 50 nm and 8 nm body thickness,

demonstrating near ideal sub-threshold swing and an enhancement in long-channel current drive and

transconductance of approximately 2X for strained-Si nanowires compared to control Si nanowires. Lowfield effective mobility of these devices was extracted using split capacitance-voltage measurements and the

two-FET method. The analysis indicates electron mobility enhancement for strained-Si nanowires over their

unstrained Si counterparts, as well as over planar SOI, specifically at high inversion charge densities.

However, the mobility of these nanowires was shown to decrease with decreasing nanowire width,

consistent with reported data on unstrained Si nanowires. A simple analytical model was developed to

investigate the contribution of the sidewalls to the nanowire width dependence of the electron mobility.

A new design and process technology was developed to accurately investigate the hole mobility of gate-allaround Si nanowires. A conformal high-κ/metal gate process, enabling uniform gating of the nanowire

perimeter, was combined with a maskless hydrogen thermal anneal to reduce sidewall roughness scattering.

Using this optimized process, long-channel devices with ideal sub-threshold swing (~60 mV/dec) and

enhanced current drive were demonstrated, indicating the excellent quality of the nanowire/high-κ interface

and low-roughness sidewalls. Capacitance-voltage characteristics of sub-micron-long Si nanowires were

accurately measured and verified by quantum-mechanical simulations. Increased effective hole mobility

with decreasing nanowire width was observed down to 12 nm for hydrogen annealed nanowires, attributed

to the smooth, high-mobility non-(100) sidewalls.

Thesis Supervisor: Judy L. Hoyt

Title: Professor of Electrical Engineering

4

To my dear mother, Azam Yazdani, for all her love and dedication

ای ﻤﺎم ﻖ و ﺪا ﮐﺎر ﺶ، ا ﻢ دا ﯽ، م

ﻘﺪ ﻢ ﻣﺎ

To my kind aunt, Sima Yazdani, for all the invaluable guidance and

instruction, toward this end and throughout my life

ای ھ ﻪ را ﻤﺎ ﯽ و آ ﻮزش ی، ﻤﺎ دا ﯽ، ﺑﺎ ﻢ

ﺮ ﻖ ا ﻦ ﺪف و ﺮا ﺮ ز ﺪ ﯽ ﻦ

5

ﻘﺪ ﻢ ﺧﺎ

ا ﮫﺎ

6

Acknowledgments

First of all, I would like to express my sincere respect and deepest gratitude to my principal

research supervisor, Prof. Judy L. Hoyt. During the past five years, Judy was the most influential

person to me. She generously helped me in all the ups and downs I encountered in my research and

student life at MIT. She patiently followed every single step of all my experiments and helped me

troubleshoot the process failures and technical difficulties. I would also like to thank Prof. Dimitri

Antoniadis, for all the technical support and helpful discussions on various projects. In fact, I

learned so much from his extensive experience in semiconductor devices and his deep insight to

the device physics. I’d also like to thank Prof. Tomás Palacios for contributing to and enhancing

the quality of this thesis.

The financial support by the FCRP Materials, Structures, and Devices Focus Center and IBM

Ph.D. Fellowship program is acknowledged. I had a great opportunity to discuss to and get

feedback from many professors and industrial directors through annual reviews and teleseminars.

Over the past five years, I was honored to work and collaborate with many outstanding

students, scientists and research staffs members at various universities and industries. Dr. Michael

Canonico of Freescale and Dr. Christian D. Poweleit of ASU are greatly acknowledged for the

Raman and XRD measurements. I would like to thank Mark Mondol, Joel K.W. Yang and Prof.

Karl K. Berggren for spending many hours with me to develop and improve the quality of e-beam

lithography. Dr. Leonardo Gomez , Gary Riggott and Meekyung Kim are highly acknowledged for

helping me with the epitaxial growth and substrate preparation and analysis. Special thanks to Dr.

Leonardo Gomez for being a great officemate and a trustworthy friend. Many thanks to James T.

Teherani who helped me with the device simulations and being a nice friend during my summer

internship at IBM.

Moving this project forward was not possible without assistance and guidance of many staffs at

MIT Microsystems Technology Laboratories who helped me bringing new materials and processes

7

to the Integrated Circuits Lab. I would like to acknowledge Vicky Diadiuk, Paul Tierney, Bernard

Alamariu, Eric S. Lim, Robert Bicchieri, Donal Jamieson, Paudely Zamora, Dan Adams, Kurt

Broderick, and Dennis Ward for trainings and troubleshooting the machines. I am thankful to my

fellow lab members past and present: Dr. Hyung-Seok Lee, Dr. Ingvar Åberg, Dr. Ali Khakifirooz,

Dr. John Hennessy, Dr. Osamah Naygeh, Dr. Andrew Ritenour, Nicole Dilello, Dr. Kevin Ryu, Dr.

Jongwoo Joh, Will Chung, Dr. Daehyun Kim, Dr. Luis Fernando Velásquez-García, Stephen A.

Guerrera, Bin Lu, Omair Saadat, Dr. Jae-kyu Lee, Dr. Ryan Lei, Kevin McComber, Jing Cheng

and Jerome Jianqiang Lin. I acknowledge them for valuable conversations and assisting me with

design of new processes. Special thanks to Leo, Will, Jing, Kevin, Jerome, Kevin, Bin and Joel for

being my lab buddy on weekends and after hours.

I would also like to express my gratitude to Judy’s assistants in the past and present: Rose

Previte, Michele Hudak, and Whitney Rokui. They were great help with administrative tasks. I

would also like to acknowledge the MTL’s administrative staffs and specialists: Deborah HodgesPabon, Pat Varley, Samuel Crooks, Mara Karapetian, and Michael McIlrath. I am also thankful to

the staffs at Department of Material Science and Engineering of MIT: Dr. Yong Zhang, for training

me on TEM and SEM, Libby Shaw for training me on AFM and Dr. S. J. Chen for training me on

the new FIB machine.

I am truly indebted and thankful to my former research Supervisor, Prof. Shams Mohajerzadeh

who motivated me with the world-class research in the field of microelectronic devices. I would

like to show my gratitude to Dr. Ghavam G. Shahidi, Dr. Devendra Sadana, and Dr. Davood

Shahrjerdi for mentoring and supporting me with the industrial research at IBM.

I am heartily thankful to my mother for all her love and dedication and my aunt, for all the

invaluable guidance and instruction, toward this end and throughout my life. My siblings Kousha

and Dena for continuous love and encouragement. Special thanks to my uncles, Dr. Ali and Akbar

Yazdani for all the generous financial and mental supports throughout my life. Finally, I’d like to

thank my love, Azadeh, for bringing happiness to my life and for all the wonderful moments we

had together during the past year.

8

Contents

List of Figures...................................................................................................................................... 13

List of Tables ....................................................................................................................................... 25

Chapter 1: Introduction ................................................................................................................... 27

1.1 Thesis Introduction and Motivation ....................................................................................... 27

1.2 Thesis Outline ......................................................................................................................... 31

Chapter 2: Thesis Background ........................................................................................................ 33

2.1 Introduction to Multi-Gate Devices ....................................................................................... 33

2.2 Scaling Theory of MOSFETs and Advantages of Nanowires .............................................. 36

2.3 Carrier Transport and Scattering Mechanisms....................................................................... 40

2.3.1 Mobility and Velocity ............................................................................................. 40

2.3.2 Scattering Mechanisms ........................................................................................... 43

2.3.2.1 Coulombic Scattering .............................................................................. 44

2.3.2.2 Surface Roughness Scattering ................................................................ 45

2.3.2.3 Phonon Scattering and Confinement ....................................................... 46

2.3.2.4 Thickness Fluctuation Scattering ............................................................ 50

2.3.2.5 Remote Phonon Scattering ...................................................................... 51

2.4 Transport Enhancements Options for Multi-gate MOSFETs................................................ 54

2.4.1 Surface Crystallographic Orientation and Channel Direction ............................... 54

2.4.2 Strain Engineering ................................................................................................... 57

2.4.3 Technological Implementation: New Materials and Processes ............................. 61

2.5 Mobility Extraction for Gate-All-Around Nanowires MOSFETs ........................................ 63

2.6 Chapter Summary ................................................................................................................... 70

Chapter 3: Asymmetrically Strained-Si and Ge Channels .......................................................... 73

9

3.1 Biaxial to Uniaxial Strain Transformation ............................................................................. 73

3.2 Asymmetrically Strained-Ge Nano-Bars ............................................................................... 75

3.2.1 Fabrication and Metrology ...................................................................................... 75

3.2.2 Strain Characterization ............................................................................................ 76

3.3 Suspended Uniaxially Strained-Si Nanowires ....................................................................... 79

3.3.1 Fabrication of Strained-Si Nanowires .................................................................... 79

3.3.2 Raman Characterization and Stress Mapping......................................................... 80

3.3.3 Vertically-Stacked Strained-Si Nanowires ............................................................. 85

3.4 Chapter Summary ................................................................................................................... 88

Chapter 4: Gate-All-Around Uniaxially Strained-Si Nanowire n-MOSFETs .......................... 89

4.1 Introduction ............................................................................................................................. 89

4.2 Device fabrication and Metrology .......................................................................................... 90

4.3 Electrostatics and Threshold voltage ...................................................................................... 93

4.4 Performance Evaluation.......................................................................................................... 96

4.5 Mobility Characterization ....................................................................................................... 99

4.5.1 Split CV Measurements .......................................................................................... 99

4.5.2 Electron Mobility .................................................................................................. 102

4.5.3 Width Dependence of Electron Mobility.............................................................. 104

4.5 Chapter Summary ................................................................................................................. 109

Chapter 5: Device Design and Process Technology for Gate-All-Around Si Nanowire pMOSFETs......................................................................................................................................... 111

5.1 Introduction ........................................................................................................................... 111

5.2 Device Design for Accurate Mobility Extraction ................................................................ 112

5.3 Hydrogen Anneal Process .................................................................................................... 117

5.4 High-κ/Metal Gate Process................................................................................................... 122

5.4.1 ALD Al2O3/WN Stack with O3 Surface Passivation ........................................... 123

5.4.2 Planar SOI Mobility .............................................................................................. 125

5.4.3 Tungsten Nitride (WN) Workfunction ................................................................. 126

10

5.5 Chapter Summary ................................................................................................................. 127

Chapter 6: Hole Transport in Gate-All-Around Si Nanowire p-MOSFETs ........................... 129

6.1 Introduction and Process Splits ............................................................................................ 129

6.2 Device Characteristics .......................................................................................................... 130

6.2.1 Drain Current and Electrostatics ........................................................................... 130

6.2.2 Performance Enhancement by Hydrogen Anneal ................................................ 132

6.3 Hole Mobility Characterization ............................................................................................ 134

6.3.1 Capacitance Measurements and Mobility Extraction .......................................... 134

6.3.2 Charge Distribution and Capacitance Simulations .............................................. 135

6.3.3 Hole Mobility Investigation .................................................................................. 138

6.3.3.1 Nanowires without Hydrogen Anneal................................................... 139

6.3.3.2 Nanowires with Optimized Hydrogen Anneal (Condition B) .............. 140

6.3.3.3 Nanowires with Non-Optimized hydrogen Anneal (Condition C) ...... 143

6.3.4 Width Dependence of Hole Mobility ................................................................... 144

6.4 Chapter Summary ................................................................................................................. 148

Chapter 7: Summary and Suggestions for Future Work........................................................... 151

7.1 Thesis Summary.................................................................................................................... 151

7.2 Suggestions for Future Work................................................................................................ 155

7.3 Contributions ......................................................................................................................... 156

Appendix A: E-beam Lithography with Hydrogen Silsesquioxane Negative-Tone Resist.... 157

A.1 Hydrogen Silsesquioxane Negative-Tone Resist ................................................................ 157

A.2 Hybrid Lithography ............................................................................................................. 162

A.3 Fabrication Process for Ultra-Dense Si Nanowires ............................................................ 164

Appendix B: Raman Spectroscopy of Strained-Si Nanowires .................................................. 167

B.1 Raman Characterization of Suspended Nanowires ............................................................. 167

B.2 Raman Characterization of Ultra-Dense Strained-Si Nanowires ....................................... 169

11

Appendix C: Fabrication Flow and Stress Characterization of Vertically-Stacked Strained-Si

Nanowires ......................................................................................................................................... 173

C.1 Starting Substrates ................................................................................................................ 173

C.2 Fabrication Steps .................................................................................................................. 176

Appendix D: Process Flow for Gate-All-Around Si (Strained-Si) Nanowire n-MOSFETs .. 177

D.1 Fabrication Flow .................................................................................................................. 177

D.2 Gate-Alignment and Stringer Etch ...................................................................................... 180

Appendix E: Process Flow for Gate-All-Around Si Nanowire p-MOSFETs with Highκ/Metal Gate Process ...................................................................................................................... 183

E.1 Fabrication Flow................................................................................................................... 183

E.2 Polycrystalline-Si/WN Gate Stack....................................................................................... 186

Appendix F: Si/Ge Core-Shell Nanowire p-MOSFETs .............................................................. 189

F.1 Fabrication of Si/Ge Core-Shell Nanowire p-MOSFETs.................................................... 189

F.2 Electrical Characterization and Mobility Calculation ......................................................... 191

F.3 Appendix Summary .............................................................................................................. 195

Bibliography..................................................................................................................................... 197

12

List of Figures

Figure 2.1:

Schematic diagram of (a) planar ultra-thin-body SOI, (b) double-gate FinFET, (c)

Tri-gate FET and (d) gate-all-around nanowire FET, viewing in a direction

perpendicular to the current transport, representing the evolution of nanowire FET

from an ultra-thin-body SOI FET. The required criterion on the Si thickness (tSi) for

a given gate length (LG) to have acceptable electrostatics is also shown, indicating

more relaxed channel dimension available for nanowire FET (compared to other

architectures) to be considered as a candidate for a given technology node. ........... 35

Figure 2.2:

Universal dependence of (a) subthreshold slope and (b) drain-induced-barrierlowering (DIBL) on the scaling parameter, for gate-all-around and double-gate

MOSFETs with various oxide and Si thicknesses. Data from Ref. [44]. ................. 37

Figure 2.3:

(a) Capacitance circuit model and conduction band profile of a MOSFET,

introducing the capacitances of source (Cs), drain (Cd) and oxide (Cox) as well as

surface channel charge (Qch) [46, 47]; (b) Simplified capacitance model of the gate

of a MOSFET (CG), displaying the physical oxide thickness (Cox) and the quantum

capacitance (CQ). .......................................................................... ............................ 39

Figure 2.4:

Schematic sub-band structures of two-dimensional electrons for bulk and ultra-thinbody SOI MOSFETs. Structural confinement of the inversion layer in ultra-thinbody SOI MOSFETs decreases the average thickness of the inversion layer (Zav) as

well as phonon-limited mobility and increases the inversion layer capacitance and

threshold voltage (After Uchida et al. [63]). ................................ ............................ 50

Figure 2.5:

Schematic of (left) interface-roughness induced thickness fluctuation scattering and

(right) variation of conduction band due to thickness fluctuation scattering in ultrathin-body SOI channels (After Ref. [64])..................................... ............................ 51

Figure 2.6:

(a) Calculated effective electron mobility of Si inversion layers of MOS system

with insulators indicated. Remote scattering with surface optical phonons,

anisotropic scattering with acoustic phonons and empirical scattering with surface

roughness have been considered (b) Calculated total electron mobility in the

13

inversion layer of a HfO2 /SiO2 /Si system as a function of thickness of the

interfacial SiO2 layer for the three indicated values of the electron concentration in

the inversion layer. The horizontal lines at the far right are the asymptotic limits of

infinite oxide thickness (Results from Fischetti et al. [70]). ........ ............................ 53

Figure 2.7:

Effective electron and hole mobility of Si as a function of inversion charge density

for (100), (111) and (110) surfaces. Mobility is isotropic (direction independent) for

(100) and (111) surfaces. Among all surface/directions, (100) and (110)/<110>

have the highest electron and hole mobility, respectively (Results from Irie et al.

[73]). .............................................................................................. ............................ 55

Figure 2.8:

(a) Schematic of Si conduction band’s equienergy ellipsoids, displaying Δ2 and Δ4

valleys; (b) Equienergy valleys of Si on (110) surface. Four valleys with heavy ml

and two valleys with light mt contribute to the conduction along <110> direction;

(c) Equienergy valleys of Si on (100) surface. Two valleys with heavy ml and four

valleys with light mt contribute to the conduction along <100> or <110> direction,

offering lower conductivity mass compared to (110) surface. .... ............................ 56

Figure 2.9:

(Top) energy and (bottom) equienergy lines of the lowest-lying subbands (HH, LH

and SO) along with the position of the Fermi level for (001), (011) and (111)

relaxed Si surfaces. Spin degeneracy is lifted away from the center of the zone, so

that the density of states given subband depends on spin variables (Results from

Fischetti et al. [65]). ...................................................................... ............................ 56

Figure 2.10: Schematic of electron repopulation in the conduction band equienergy valleys of (a)

(100) Si under <110> uniaxial or biaxial tension, (b) (110) Si under biaxial tension

and (c) (110) Si under <110> uniaxial tension. The current direction for all cases is

along <110>, which is favorable for all cases except case (b) where its mobilityenhanced direction is shown. ........................................................ ............................ 58

Figure 2.11: (a) Relative change in the Si effective mass in the direction parallel and

perpendicular to a [110] uniaxial tension (open symbols: tight binding [82], filled

symbols empirical pseudopotential [82], solid lines: empirical pseudopotential

[83]); (b) Relative change in Si electron ballistic velocity vs. relative change in

mobility for different strains (Results from Khakifirooz et al. [82]). ....................... 59

Figure 2.12: Simulated hole and electron mobility for (100) and (110) silicon substrates as a

function of uniaxial stress along <110> (Results from Packan et al. [74]). ............. 61

Figure 2.13: Schematic of the nano-patterning induced lateral relaxation mechanism. Arrows

with solid border show the direction of the strain and arrows with dashed line

14

shows the lateral relaxation direction. Biaxial stress is preferentially relaxed in the

transverse (lateral) direction. ........................................................ ............................ 63

Figure 2.14: (a) Effective hole mobility vs. inversion charge density (Ninv) for various voltage

shift between capacitance and current measurements (ΔV) due to several

mechanisms such as measurement stress effects; (b) Relative mobility error (with

respect to the case with no shift) as a function of ΔV, for Ninv=1012, 4×1012 and

7×1012 cm-2. While large error is observed for low Ninv, the error is less than 2% at

high inversion charge densities. .................................................... ............................ 66

Figure 2.15: (a) Measured capacitance of planar SOI MOSFETs with Al2O3/WN gate using split

C-V method for devices with mask gate length, Lmask = 0.4, 0.6, 0.8, 1, 1.2, 1.6 and

2 μm. For Lmask = 0.4 μm, the parasitic component (Cpar) contributes to about a

quarter of the total measured capacitance. (b) Plot of maximum capacitance (Cmax)

and the minimum parasitic capacitance (Cpar, min) vs. Lmask. Symbols are measured

data and solid lines are the best fits to the measured data. The difference of the

mask length and the effective gate length (ΔL) was extracted by intersecting the

two fitted lines. ............................................................................. ............................ 68

Figure 2.16: (a) Schematic of the gate-all-around nanowire test structures for effective mobility

extraction, utilizing two FETs with the same number of nanowire (N) and similar

cross-section (central schematic), similar parasitic resistance (i.e. similar contact

design rules and S/D materials) and capacitance (i.e. similar fringing, gate-to-pad

and gate-to-source/drain overlaps)................................................ ............................ 69

Figure 3.1:

Schematic process flow of modified bond and etch-back technique to fabricate

biaxial tensile SSDOI or compressive Ge HOI, after Gomez, et al. [129]............... 74

Figure 3.2:

Schematic diagram of fabrication of highly asymmetric, virtually uniaxial, strainedSi and strained-Ge nano-structures by unilateral relaxation of SSDOI and Ge HOI

substrates. ...................................................................................... ............................ 74

Figure 3.3:

(a) Cross-sectional TEM image of strained-Ge HOI substrate. Tilted SEM images

of (b) 100 nm and (c) 30 nm wide patterned strained-Ge HOI nano-bars prepared

for stress metrology by UV micro-Raman spectroscopy (TEM Courtesy of M.D.

Robertson). .................................................................................... ............................ 76

Figure 3.4:

(a) Raman spectra (325nm excitation) of the Ge LO phonon with overlaid

Lorentzian fit for Ge HOI sample patterned into 30 nm, 50 nm, 100 nm and 300

nm-wide stripes. Dashed line is the signal from the relaxed Ge reference sample.

For clarity, the Raman spectra and corresponding analytical fit are shifted vertically

15

relative to one another (Raman courtesy of M. Canonico (Freescale)); (b) Extracted

biaxial relaxation (solid lines) and Raman peak position (dashed lines) vs. bar width

in strained-Ge layer. ..................................................................... ............................ 77

Figure 3.5:

Schematic process flow of suspended strained-Si nanowires: (a) after spinning ebeam resist, (b) after resist development and strained-Si reactive-ion etching, (c)

after nanowire suspension in dilute HF, and (d) top-down view. (e) Tilted SEM

image of the 20 nm wide strained-Si nanowires in a 100 nm pitch; (f) Tilted SEM

image of the 18 nm wide ultra-dense strained-Si nanowires in a 40 nm pitch (inset:

top view SEM)............................................................................... ............................ 80

Figure 3.6:

(a) Raman spectra (courtesy of M. Canonico (Freescale)) of the Si LO phonon from

unstrained bulk Si (dashed line) and the 40 μm square box (solid line). The

measured Si peak shift is consistent with the strain expected in Si grown on a

relaxed SiGe donor substrate with 30% Ge concentration. (b) Raman spectra at the

center of suspended strained-Si nanowires (30 nm wide), displaying two peaks

corresponding to bulk Si substrate (right) and nanowires (left) with a ~2.1 GPa

uniaxial tension along the nanowires............................................ ............................ 81

Figure 3.7:

(a) Raman spectra (courtesy of M. Canonico (Freescale)) of the Si-Si LO phonon

mode for 30 nm wide suspended strained-Si nanowires with pads attached to the

oxide, as the laser is scanned from pad to pad in a direction parallel to the nanowire

length , as shown in the schematic (b). ......................................... ............................ 82

Figure 3.8:

Total in-plane stress (circles, left axis) and corresponding signal-to-noise ratio

(squares, right axis) for spectra collected from the 2 μm long nanowires midway

between the two pads. ................................................................... ............................ 84

Figure 3.9:

(a)-(c) Schematic of the process flow utilized to realize vertically stacked strainedSi nanowires; (d) top view of the stacked-Si nanowires highlighting the region

where Raman signal was collected; (e) SEM images of N = 1 to 5 level verticallystacked strained-Si nanowires. ...................................................... ............................ 86

Figure 3.10: (a) Raman spectra (courtesy of C. D. Poweleit, ASU) of at the center of array of

suspended strained-Si nanowires with (WNW = 30 and 35 nm, and N = 1 and 5

number of stacked layers); (b) Biaxial strain relaxation (with starting substrates as

reference) vs. number of nanowires as a function of nanowire width, indicating

stress preservation after 5 layer stacking of nanowires. ............... ............................ 87

Figure 4.1:

(a) Fabrication process flow of gate-all-around uniaxial strained-Si nanowire nMOSFETs. (b) Top-view and (c) side-view schematic of suspended uniaxially

16

tensile strained-Si channel fabricated by lateral relaxation and undercutting the

nanowires. Inset shows the nanowire dimensions and stress direction. ................... 90

Figure 4.2:

(a) Sample tilted SEM image of suspended strained-Si nanowires. (b) Top-view

colored SEM image of gate-all-around strained-Si nanowire n-MOSFET with 10

parallel nanowires. The poly-Si/LTO gate stringers at the edge of ion-implanted

source/drain pads were etched using a separate protection mask. ............................ 92

Figure 4.3:

Cross-sectional TEM of gate-all-around n-MOSFETs with (a) elliptical and (b)

circular cross-section strained-Si nanowires. The focused-ion-beam cut is

perpendicular to the nanowire direction (electron transport direction). Heavilydoped poly-Si gate and low-temperature oxide wraps all around the Si

nanowires…................................................................................... ............................ 93

Figure 4.4:

Typical (a) transfer (ID - VGS) and (b) output characteristics (ID - VDS) for a circular

cross-section gate-all-around strained-Si nanowire n-MOSFET with N = 10

nanowires, average nanowire diameter of ~ 8 nm, and LNW ~ 0.65 μm. For (a), the

left axis shows the current in logarithmic scale while the right axis shows it in linear

scale. .............................................................................................. ............................ 94

Figure 4.5:

(a) Plot of subthreshold slope as a function of WNW and LNW for SSOI nanowires

with low-temperature oxide (LTO) and thermal oxide gate dielectrics showing near

ideal subthreshold swing. (b) Variation of threshold voltage (Vth) vs. WNW for SOI

and SSOI nanowires showing Vth shift of -120 ± 30 mV due to uniaxial straininduced conduction band shift. The Vth roll-up for sub 15 nm nanowires is due to

quantum mechanical confinement. ............................................... ............................ 95

Figure 4.6:

Transfer characteristics of gate-all-around Si and strained-Si nanowire n-MOSFETs

(with LTO gate dielectric) showing near ideal subthreshold slope of 65 mV/dec.

and ~2X current enhancement and ~ 0.1 V strain-induced Vth shift. ....................... 96

Figure 4.7:

(a) Extrinsic transconductance (gm) of SOI and SSOI Gate-all-around nanowires vs.

overdrive voltage (VGS-Vth) for nanowires with WNW 20 nm, tNW = 8 nm. SSOI

NW exhibits a 1.95X enhancement in gm, max relative to SOI nanowire devices. The

enhancement at higher overdrives is degraded by increased contribution of the

external resistance. ........................................................................ ............................ 97

Figure 4.8:

(a) Plot of total channel resistance vs. 1/(VGS-Vth-VDS/2) to extract external series

resistance (Rext) for SOI and SSOI nanowires vs. VGS-Vth (WNW 20nm, tNW =

8nm, N = 10). Rext (shown in the figure) is extracted from the intersect of the

extrapolated curve with the vertical axis. (b) Intrinsic transconductance of these

17

devices after correction for Rext. Enhancement factors of 2.1X at maximum gm and

1.86X at VGS-Vth = 0.7 V are due to the uniaxial strain. .............. ............................ 98

Figure 4.9:

Intrinsic gm, max (VDS = 50 mV) vs. WNW for SOI and SSOI gate-all-around devices

with LNW = 0.8 μm, tNW ~ 8 ± 1 nm and N = 10, displaying an average enhancement

in gm, max of ~2X down to sub-10 nm nanowire dimensions. ....... ............................ 99

Figure 4.10: Split capacitance-voltage characteristics of an SSOI nanowire n-MOSFETs (N =

10, WNW ~ 49 nm, tNW ~ 8 nm, LNW = 10 µm) measured at f = 40 kHz and 40X

point averaging to minimize the noise. The gate-channel capacitance (Cgc) was

extracted by subtracting the parasitic capacitance, Cpar, (background and overlap

capacitance, measured from devices without nanowires but with gate overlap on the

S/D regions) was subtracted from the total capacitance (Ctot). (b) Cgc vs. VGS for

SSOI nanowire n-MOSFETs (N = 10, WNW ~ 39 nm, tNW ~ 8 nm, LNW = 10 µm)

extracted at f = 40 kHz and f = 1 MHz. ....................................... .......................... 100

Figure 4.11: Intrinsic gate-channel capacitance-voltage of gate-all-around SSOI nanowires with

WNW = 25, 39, 49 nm. The background and overlap capacitances were subtracted

from the original split-CV. 40 point averaging was used to reduce the noise........ 101

Figure 4.12: (a) Gate-channel capacitance and (b) total channel resistance of SSOI nanowire nMOSFETs (N = 10, WNW ~ 49 nm, tNW ~ 8 nm) with LNW = 10 µm (C1) and LNW = 4

µm (C2) used to extract the mobility using 2-FET method. The extracted Rext is also

shown in (b) ................................................................................... .......................... 102

Figure 4.13: Low-field electron mobility (μeff) vs. charge density (Ninv) of SSOI NW (WNW = 49

nm, tNW = 8.7 nm) measured by split-CV and 2-FET method. μeff for the widest SOI

NW (W = 44nm), planar SOI and SSDOI (tSi = 8.7 nm) (11), and universal are

shown for comparison. .................................................................. .......................... 103

Figure 4.14: Low-field electron mobility (μeff) vs. charge density (Ninv) with WNW ~ 15, 20, 25,

39, 49 nm. The electron mobility plot of fully-depleted ultra-thin-body (8 nm) SOI

is shown for comparison [67]. Mobility is reduced as WNW is decreased, mostly due

to an increase in the contribution of the sidewalls. ...................... .......................... 104

Figure 4.15: (a) Electron mobility for SSOI NWs vs. (a) WNW and (b) the ratio of sidewall to

surface (Wsidewall/Wsurarface , as schematically shown in the inset) at Ninv = 1013 cm-2.

Overlaid are the mobilities of unstrained-Si nanowires (empty triangles: Ref. [23],

empty squares: Ref. [121]). ........................................................... .......................... 105

Figure 4.16: Electron mobility of for SSOI NWs (solid symbols) and SOI NWs (open symbols,

[121]) vs. WNW at Ninv = 1013 cm-2. Lines are the empirical model with rμ = 0.34,

18

0.2 and 0.15 (with rμ decreasing in the direction of the arrow) for SSOI NWs and rμ

= 0.35 and 0.2 for SOI NWs ......................................................... .......................... 107

Figure 5.1:

Process flow utilized to fabricate gate-all-around nanowire p-MOSFETs with highK/metal gate and hydrogen annealing process. ............................ .......................... 113

Figure 5.2:

(a) Schematic of the protection mask to locally release the Si nanowires. (b)

Schematic of the suspended Si nanowires after local release in buffered-oxide-etch,

demonstrating no space available for gate-stringer at source/drain edges. (c)

Schematic of design layout of the Si nanowire MOSFETs, displaying the contact

vias, gate-to-pad overlap (< 100 nm), distance between contact via and the gate

edge (dvia-gate< 400 nm), and between contact via and metal edge (dvia-metal< 400

nm). ................................................................................................ .......................... 114

Figure 5.3:

Schematic device structure of the gate-all-around nanowire MOSFETs designed for

mobility extraction. A-A’ and B-B’ cut-lines represent the device cross-sections

perpendicular and along the nanowire direction, respectively. Device dimensions

(WNW, Wtot, tNW, LNW, Lov and N), channel resistance (RNW and Rov) and capacitive

(Cpar) and resistive (Rext) parasitics are shown on the B-B’ cross-section.............. 115

Figure 5.4:

(a) Tilted and (b) cross-sectional SEM images of the final gate-all-around nanowire

p-MOSFETs with high-κ/metal-gate, with a FIB cut along the suspended nanowire

direction. ........................................................................................ .......................... 116

Figure 5.5:

(a) Schematic and (b) top-view SEM of suspended Si nanowires before and after

high-temperature hydrogen annealing. The right SEM images were enhanced for

brightness, contrast and shadows to magnify the line edge roughness of the Si

nanowires. Reduced sidewall roughness is observed after hydrogen annealing. ... 118

Figure 5.6:

(a) Plan-view SEM images of suspended Si nanowires subjected to hydrogen

anneal at 850°C, with WNW = 14-73 nm; (b) XTEM of on-wafer nanowire test

structure (as-patterned WNW = 20 to 60 nm; step 4 nm) subjected to hydrogen

anneal at 850°C, after device completion. Nanowires are surrounded by conformal

~1 nm ALD O3-SiO2 / 5.5 nm Al2O3 / 30 nm WN gate stack (stack κ = 7.4). For

wide nanowires, tNW = 16 nm; dropping to 13 nm for the circular nanowire. (110),

(111) and (311) sidewall facets are discernible from the XTEM images............... 119

Figure 5.7:

SEM image of array of nanowire test structure (a) as-patterned, (b) after hydrogen

annealing at 875°C and (c) after hydrogen annealing at 900°C. Anisotropic

hydrogen etching and nanowire pinch-off at the pad/nanowire boundaries are

observed for annealing at temperatures higher than 875°C. ........ .......................... 121

19

Figure 5.8:

High-resolution Focused-Ion-Beam (FIB) cross-sectional SEM image of a

nanowire test structure (with as patterned WNW = 20 to 60 nm; step 4 nm) subjected

to hydrogen anneal at 850°C followed by 875°C, after device completion.

Nanowire diameters (dNW, as defined in the SEM image) are scaled from 22 nm

down to sub-10 nm, mostly with circular cross sections. ............ .......................... 122

Figure 5.9:

(a) Split capacitance-voltage characteristics of SOI p-MOSFETs with 7 cycles of

ALD O3, 60 cycles of Al2O3 and WN metal gate, measured at f = 1, 10 and 100 kHz

; The Al2O3 dielectric was deposited using Tri-Methyl-Aluminum (TMA) source at

200°C. (b) Corresponding forward and backward sweeps at f = 100 kHz, showing

80 mV hysteresis ........................................................................... .......................... 124

Figure 5.10: (a) Split capacitance-voltage characteristics of SOI p-MOSFETs with 7 cycles of

ALD O3, 55 cycles of Al2O3 and WN metal gate, showing negligible frequency

dependence at f = 1, 10 and 100 kHz; The Al2O3 dielectric was deposited using TriMethyl-Aluminum (TMA) source at 250°C. (b) Corresponding forward and

backward sweeps at f = 100 kHz, showing no hysteresis. ........... .......................... 125

Figure 5.11: Effective hole mobility vs. inversion charge density (Ninv) for planar SOI devices

with ALD O3-SiO2 / Al2O3 / WN process. Al2O3 was deposited using Tri-MethylAluminum (TMA) at 200°C and 250°C and Tris-Di-Methyl-Amido-Aluminum

(TDMAA) at 200°C. ..................................................................... .......................... 126

Figure 5.12: (a) Schematic of the test structure used to extract the WN workfunction; (b) Plot of

flatband voltage (VFB) vs. capacitance effective thickness (CET) for

WN/Al2O3/SiO2/Si stack as the thickness of the SiO2 is varied. . .......................... 127

Figure 6.1:

(a) Transfer and output characteristics of gate-all-around ~15 nm-diameter

nanowire (LNW = 0.6 µm, N = 500) p-MOSFETs with high-K/metal gate and

hydrogen anneal process, showing ideal sub-threshold slope of 61 mV/dec and very

high on-to-off ratio. ....................................................................... .......................... 131

Figure 6.2:

(a) Subthreshold slope (SS) and (b) threshold voltage (Vth) as a function of WNW for

gate-all-around p-MOSFETs with Al2O3/WN gate stack. All devices show ideal

swing (with a minimum of 60.5 mV/dec for 15 nm circular NW), indicating very

low Dit. ........................................................................................... .......................... 132

Figure 6.3:

Transfer characteristics of 22×15.6 nm gate-all-around nanowire p-MOSFETs (with

N = 500 nanowires) treated with hydrogen anneal at 850°C (condition B) and

without hydrogen anneal (condition A), indicating ideal SS = 61 mV/dec and very

20

high on-to-off ratio (~1010). No hysteresis was observed in the transfer

characteristics. ............................................................................... .......................... 133

Figure 6.4:

Plots of (a) ID vs. gate over-drive voltage (VGS-Vth) and (b) ID vs. VDS for VGS-Vth =

-2 V to 0 V step -0.25 V, for 22×15.6 nm gate-all-around nanowire p-MOSFETs

with hydrogen anneal at 850°C (condition B) and without hydrogen anneal

(condition A), indicating ~1.6X enhancement for linear and saturation current due

to the hydrogen anneal process (condition B). ............................. .......................... 134

Figure 6.5:

Typical split-CV and ID-VGS measurements of 15 nm-diameter circular nanowire

(with LNW= 0.6 and 1.2 µm) for mobility extraction using the 2-FET method. Drain

current was measured at VDS = -50 mV. Current and capacitances are normalized

by the number of nanowires (N = 500). ....................................... .......................... 135

Figure 6.6:

Simulated (nextnano3) hole charge density in nanowires with (a) circular (15.6×14

nm, dNW~15 nm) and (b) elliptical (22×15.7 nm) and cross-sections for VGS-VFB = 1.3 V. Inversion centroid is displaced from nanowire surface by the distance

δQM(VGS). Simulation courtesy of J. Teherani.. ............................ .......................... 136

Figure 6.7:

Measured and nextnano3 simulated inversion capacitance of 15 nm-diameter

circular and 22 nm×15.6 nm elliptical nanowires, demonstrating very good

agreement between measured and simulated results, verifying mobility extraction

method. Only physical dimensions (derived from TEM), κ (extracted from planar

CV measurements) and Qf were input into the simulations. The upper and lower

simulated curves correspond to a metal with high and low density of states,

respectively. Simulation courtesy of J. Teherani. ........................ .......................... 137

Figure 6.8:

Measured (symbols) and simulated (lines) intrinsic capacitances for nanowires

annealed at 875°C (condition C) with nanowire diameter, dNW = 8-17 nm. dNW was

measured by high-resolution cross-sectional SEM and was input into the

simulations for 12 and 17 nm nanowires. For sub-10 nm nanowires, the effective

circular diameter (dNW,eq) was extracted by fitting simulations to the CV

measurements. Simulation courtesy of J. Teherani. ..................... .......................... 138

Figure 6.9:

Effective hole mobility vs. inversion charge density (Ninv, normalized by nanowire

circumference) for nanowires with WNW = 22-72 nm, without hydrogen anneal.

Similar mobilities are observed at high Ninv for various WNW, with a ~20 % drop

compared to planar (100) SOI device. .......................................... .......................... 139

Figure 6.10: (a) Effective hole mobility vs. Ninv (normalized by nanowire circumference) for

nanowires with WNW = 15-72 nm subjected to hydrogen anneal at 850°C (condition

21

B). Monotonic mobility enhancement with decreasing nanowire width is observed,

due to increased contribution of high-mobility sidewalls and reduced sidewall

roughness scattering. Mobility is enhanced by 47% relative to the widest nanowire

and 33% over planar (100) SOI device at Ninv=1.1×1013cm-2. (b) Hole mobility vs.

Ninv for 15 nm circular nanowires demonstrating mobility enhancement over planar

SOI and the highest mobility of nanowires without hydrogen anneal. Significant

enhancement is seen relative to published data for sub-15 nm thickness

nanowires…................................................................................... .......................... 140

Figure 6.11: Hole mobility vs. Ninv, normalized by nanowire physical perimeter (dashed line)

and with quantum-mechanical (QM) correction (symbols) for circular (15.6×14 nm,

dNW ~ 15 nm) and elliptical (22×15.7 nm) nanowires. The QM correction to the

perimeter was calculated using simulations at each gate bias. .... .......................... 141

Figure 6.12: (a) Transfer characteristics of gate-all-around nanowire p-MOSFETs (with dNW ~ 8,

10, 12, 17, 22 nm and LNW = 0.6 µm subjected to non-optimized hydrogen anneal

(condition C). Non ideal swings (>80 mV/dec) suggest that nanowires have high

density of interface traps due to non-optimized condition C. ...... .......................... 142

Figure 6.13: Plots of effective hole mobility vs. inversion charge density, for nanowires with (a)

WNW = 12-32 nm and (b) WNW < 12 nm subjected to non-optimized hydrogen

anneal (condition C). Mobilities are generally reduced due to high density of

interface traps of condition C. ....................................................... .......................... 143

Figure 6.14: Width-dependence of hole mobility for nanowires with and without hydrogen

anneal, at Ninv= 5×1012 and 1013 cm-2. Flat mobility behavior is observed without

hydrogen anneal due to a balance between high-mobility non-(100) planes and

sidewall roughness scattering. The latter mechanism is significantly diminished

with hydrogen anneal (condition B), and more than 57% enhancement is observed

for WNW < 22 nm. .......................................................................... .......................... 144

Figure 6.15: Hole mobility of Si nanowires vs. WNW at Ninv = 1013 cm-2. Symbols correspond to

the experimental results. Lines are the empirical model with μs = 70 cm2/V.s and rμ

= 1.95 (dot-dashed line), μs = 50 cm2/V.s and rμ = 1.95 (solid line), and μs = 70

cm2/V.s and rμ = 0.9-1.42 (dot-dashed line) to fit the experimental data. .............. 145

Figure 6.16: Hole mobility in Si nanowires subjected to hydrogen anneal at 875°C (condition C)

vs. nanowire diameter (width) for Ninv = 5×1012 and 1013 cm-2. Increased mobility is

observed by reducing dNW to 12 nm diameter (elliptical to circular shape transition),

while the mobility of sub-12 nm circular nanowires is reduced as dNW is

decreased... .................................................................................... .......................... 147

22

Figure 6.17: Comparison of the normalized hole mobility (at Ninv = 1013 cm-2) vs. nanowire

width, for various post-suspension treatments. Mobilities are normalized by the

mobility of on-chip planar SOI p-MOSFET, extracted for each process condition.

Similar normalized mobilities are observed for hydrogen annealed nanowires

processed at conditions B and C, in the common range of WNW. .......................... 148

Figure A.1: Plot of relative remaining Hydrogen Silsesquioxane (HSQ) thickness vs. exposure

dose for HSQ on HOI samples exposed at 10 keV and 30 keV. Both samples were

prebaked at 90°C for 4 minutes and developed with 25 wt. % TMAH for 1 minute.

While similar contrast is observed, higher dose is required to expose HSQ at energy

of 30 keV. ...................................................................................... .......................... 158

Figure A.2: Contrast curve for 4% XR-1541 Hydrogen Silsesquioxane (HSQ) exposed at 30 keV

and developed in 0.26N TMAH and 25 wt. % TMAH at the room temperature. The

contrast is significantly enhanced using 25 wt. % TMAH. ......... .......................... 160

Figure A.3: Contrast curve for 4% XR-1541 Hydrogen Silsesquioxane (HSQ) prebaked at 200°C

and 90°C for 2 minutes, exposed at 30 keV and developed in 25 wt. % TMAH for 1

minute. While similar contrast is observed, prebaking at 90°C has a wider exposure

window. ......................................................................................... .......................... 160

Figure A.4: (a) Typical plan-view SEM image of 20 nm-wide 4% XR-1541 Hydrogen

Silsesquioxane (HSQ) line and (b) corresponding line edge profile. HSQ was

developed in 25 wt % TMAH for 60 seconds. (c) Tilted SEM image of HSQ lines

(various width) on Si wafer after Si etch and (d) magnified cross-sectional SEM of

17.3 nm HSQ line (with an aspect ratio of ~5) on a Si fin........... .......................... 161

Figure A.5: SEM images of the e-beam alignment marks with various sizes in the range of ~0.2

µm to ~ 6 µm created by photolithography and over-exposure... .......................... 162

Figure A.6: SEM image of nanowire/pad structure created using hybrid lithography process (a)

before Si reactive-ion etching and (b) after Si reactive-ion etching and photoresist

ashing. ............................................................................................ .......................... 163

Figure A.7: SEM images of ultra-dense 10 nm 6% XR-1541 Hydrogen Silsesquioxane (HSQ)

lines in 30 nm pitch achieved by a salty developed. .................... .......................... 164

Figure B.1: Raman spectra of the Si-Si LO phonon mode as the laser is scanned from pad to pad

in a direction parallel to the nanowire length for (a) 40 nm, (b) 25 nm and (c) 20

nm-wide nanowires. The nanowires are ~25 nm thick and 2 μm long................... 168

23

Figure B.2: Total in-plane stress extracted from the data assuming biaxial isotropic strain for each

spectrum along the Raman line scan for nanowires with widths of (a) 40, (b) 30, (c)

25, and (d) 20 nm. ......................................................................... .......................... 169

Figure B.3: (a) Low (b) and high laser power spectra of the Si LO phonons from the nanowires

and substrate. Thermal expansion contributes to an apparent ~0.18 GPa total inplane stress shift in the high power case....................................... .......................... 170

Figure B.4: (a) Raman spectra of the Si-Si LO phonon mode and (b) total in-plane stress as the

laser is scanned from pad to pad in a direction parallel to the nanowire length, for

ultra-dense 18 nm-wide nanowires. The nanowire pitch size was reduced to 40 nm

to improve the Raman signal-to-noise ratio. ................................ .......................... 170

Figure C.1: Schematic of starting as-grown epitaxial substrates with (a) single and (b) N = 5

period superlattice of strained-Si/Si0.7Ge0.3; (c) Raman spectra of the Si LO phonon

from the as grown substrate with N = 5 periods using 4 different excitation

wavelengths which vary the penetration depth into the layers. No change in Raman

peak position was observed using different laser lines with different penetration

depths, indicating similar stress in all layers; (d) Raman spectra of starting

substrates with N=1 to 5 periods using 458 nm laser and (e) relative Raman shift

from a Si reference corresponding to strained-Si and relaxed SiGe peaks. For all

samples (up to 5 periods), the starting substrates show fully strained Si. The bulk Si

signal is successfully eliminated for an excitation wavelength of 458 nm via the

intervening thick relaxed SiGe layer. ........................................... .......................... 174

Figure D.1: (a) SEM image of the gate photoresist on the S/D anchors after successive alignment

corrections, demonstrating excellent alignment(< 30 nm accuracy). (b) SEM image

of the photoresist masking layer to etch poly-Si stringers from the S/D anchor

edges. Note this is a test structure with no poly-Si gate (not a real device) to

demonstrate the position of the stringer-etch mask. ..................... .......................... 180

Figure E.1:

(a) Optical photograph of in-situ N+ doped poly-Si wafer pieces deposited at 560°C

and annealed at temperatures between 600°C and 700°C, demonstrating color

change from green to magenta as the temperature is increased; (b) Plot of sheet

resistance as a function annealing temperature, for in-situ N+ doped poly-Si

deposited at 560°C.. ...................................................................... .......................... 187

Figure F.1: (a) Top-view schematic of Si/Ge nanowire PMOS device with N parallel nanowires

and a cutline indicating where the TEM cross-section was obtained; (b) crosssection TEM image of Si-core/Ge-shell NW with Al2O3/WN gate stack. ............. 190

24

Figure F.2: (a) Transfer characteristics of Si-core/Ge-shell nanowire p-MOSFET for various core

Si nanowire widths in the range of 20–50 nm; (b) Output characteristics of Sicore/Ge-shell nanowire p-MOSFET with WSi-NW = 20 nm; (c) Measured inversion

capacitance of each wire normalized per wire length as a function of WSi-NW. ..... 191

Figure F.3: (a) Hole mobility of Si-core/Ge-shell multi-nanowire p-MOSFETs with Al2O3/WN

gate stack, as a function of inversion charge density; (b) Hole mobility and

enhancement factor over the widest wire with WSi-NW = 70 nm, as a function of

core-Si NW width, indicating enhanced hole transport with decreasing wire

width… .......................................................................................... .......................... 192

Figure F.4:

Finite element (a) transverse and (b) longitudinal stress simulations of wide (WSi-NW

= 55 nm) and narrow (WSi-NW = 20 nm) Si-core/Ge-shell nanowires based on 1.4

GPa intrinsic stress of the gate stack. Both nanowires show similar longitudinal

compressive stress. The wide nanowire shows transverse compression while narrow

nanowire shows transverse tension in the top Ge surface. ........... .......................... 194

List of Tables

Table 6.1:

Process splits for post-suspension nanowire treatment, indicating pre-dielectric

cleaning and hydrogen annealing conditions. .............................. .......................... 129

Table A.1:

Optimized process flow for e-beam lithography using HSQ negative-tone

resist........ ....................................................................................... .......................... 158

Table C.1:

Process flow utilized to realize vertically stacked strained-Si nanowires. ............. 176

Table D.1:

Process flow to fabricate gate-all-around nanowire n-MOSFETs.......................... 177

Table E.1:

Process flow to fabricate gate-all-around nanowire p-MOSFETs.......................... 183

25

26

Chapter 1

Introduction

1.1 Thesis Introduction and Motivation

Complementary Metal-Oxide-Semiconductor (CMOS) technology has been scaled during the

past 30 years with a drive to continuously increase the density of devices on a chip and increase

the switching performance of transistors, the major components of electronic circuits. Towards

the end of the ITRS roadmap [1], in which the channel length is predicted to be aggressively

scaled, careful device design consideration is required due to the trade-offs between device

current drive, short channel effects and power consumption. The on-state current (Ion) of a

MOSFET is represented by

/

(1.1)

where W is the device’s width, VDD is the power-supply voltage, Vth is threshold voltage, Qs is

the inversion charge density and v is the velocity near the source region (injection velocity). The

power consumption, Pdiss, can be approximated by [2]

27

10

(1.2)

where PD, PS, α, f, CL, and S are dynamic power dissipation, static power dissipation, activity

factor, operating frequency, load capacitance, and sub-threshold slope, respectively and Ileak

represents the total leakage current from gate and junction sources, and Ith is the drain current at

Vth. In order to maintain low power consumption, lower VDD and leakage current, higher Vth and

steeper S is required according to equation (1.2). On the other hand large gate capacitance, low

Vth and high velocity are required to achieve a high performance in terms of Ion. In addition to

the trade-offs for Vth and VDD, the choice of high CG requires thinner dielectric which can

increase direct tunneling which enhances the leakage and increases the power consumption.

From the electrostatics point of view, high substrate doping is required for aggressively-scaled

planar devices to control the short channel effects. The high doping results in increased junction

and gate-induced-drain leakage (GIDL) [3], degraded on current due to the increased Coulombic

scattering [4] and increased variation in threshold voltage [5]. In addition, extension and halo

implants needed to control short channel effects increase source/drain parasitic series resistance

which degrade the current drive [6]. Considering the trade-off between the current drive, short

channel effects and power consumption [7], conventional Si MOSFETs fail to satisfy the device

requirements and new materials and device architectures are required for future CMOS

generations.

To enhance the current drive, new channel materials such as strained-Si, SiC, SiGe, Ge, III-V

have been extensively investigated over the past 20 years, by many academic and industrial

researchers with some representative papers given in references [8-13]. Uniaxially strained-Si

technology with tensile liner and embedded SiGe stressors was incorporated into main-stream

28

CMOS production starting at the 90 nm technology node [14]. To further continue scaling and

improve the current drive high-permittivity-dielectric (high-κ)/metal gate technology has also

been commercialized by Intel in the 45 nm technology node.

This has been shown to

dramatically improve the gate leakage and power consumption for both NMOS and PMOS

devices [15]. Ultra-thin-body and multi-gate SOI devices have been shown to provide excellent

scalability and immunity to short-channel effects [16, 17]. The geometry enables excellent

electrostatic control by the gate and the lightly-doped Si channel dramatically reduces the

random dopant fluctuation and Vth variation [16]. In addition, these device architectures benefit

from lower capacitive parasitics and junction leakage due to the presence of a thick buried oxide.

Among various options for a multi-gate device architecture, such as double-gate, tri-gate,

etc., the nanowire (NW) channel with a wrap-around gate, so called Gate-All-Around (GAA),

has the largest advantage in terms of electrostatic integrity as will be discussed in Chapter 2.

Two approaches are generally used to fabricate Si NWs as well as other semiconductor NWs:

bottom-up and top-down. In the first method, NWs are usually grown using a metallic catalyst on

a separate substrate, usually through a Vapor-Liquid-Solid (VLS) growth mechanism. After a

chemical or mechanical separation step, the NWs are harvested and transferred to another

substrate [18-20]. In the top down-approach, the NWs are fabricated using a CMOS compatible

technology, such as lithography-based patterning and etching [21]. Unlike the bottom-up

approach where the NWs are randomly distributed, the top-down method enables accurate

positioning of the NWs across the wafer and facilitates the ultra-large-scale-integration for highperformance nano-electronic circuits. Moreover, due to process difficulties related to the length

of grown NWs, NW release and gate-etch process, most of the VLS grown NW transistors have

an omega-shaped gate (Ω-gate) geometry and are thus not full gate-all-around [18].

29

In a long channel MOSFET, carriers encounter various scattering mechanisms on their path

toward the drain terminal. Carrier mobility is a well known benchmark to judge the intrinsic

performance of a long channel MOSFET. Equation (1.1) indicates that the injection velocity near

the source determines the on-state current of a short channel device. As will be discussed in

Chapter 2, state-of-the art short channel devices do not operate in the fully ballistic regime (they

are at roughly 60% of the ballistic limit) and mobility is related to velocity through effective

mass and ballistic ratio. Therefore, understanding the carrier mobility is beneficial to design and

engineer new devices for future CMOS generations. To date, very few groups have examined the

intrinsic transport in Si NWs [22-25]. The presence of significant resistive and capacitive

parasitics as well as lack of large capacitance due to the small size of the NW channel adds

complexities to the extraction of the intrinsic NW characteristics. In most of the published

reports, either over-simplified calculations or in-complete device charge simulations lead to

inaccurate and unreasonable mobility extraction [25]. While in the other reports with more

careful extraction techniques and design, the lack of a well-behaved top-down process (as

compared to the bottom-up-fabricated NWs with smooth, near ideal sidewalls) results in

significant mobility degradation for smaller NW sizes [23], which is not intrinsic to NWs in

general.

This thesis is about transport enhancement techniques in GAA MOSFETs. As part of this

thesis, the fabrication of Si NWs with uniaxial tensile strain is demonstrated using a novel topdown scheme. The Si NW channel combines the suspended structure required for GAA

architecture as well as built-in uniaxial tension with potential for electron transport enhancement.

The performance of novel GAA Si NW n-MOSFETs with uniaxial strain is analyzed in this

thesis. GAA Si NW p-MOSFETs were also fabricated and analyzed. In order to accurately

30

extract the hole mobility of Si NWs, a process was designed and developed using an optimized

hydrogen anneal process to form smooth, high-quality NW sidewalls. The process also benefits

from utilization of a high-κ /metal gate technology required for future CMOS generations and to

avoid the complexity which occurs when extracting mobility of NWs due to non-uniform nature

of common dielectrics such as crystal orientation-dependent thermally grown or low-temperature

oxide. Mobility enhancement over planar SOI MOSFETs is observed for both engineered nchannel and p-channel NW GAA MOSFETs. The observations provide insights into the physics

of NW MOSFETs which are of interest for future low-power, high-performance CMOS

technologies.

1.2 Thesis Outline

Chapter 2 briefly overviews the background physics and methods incorporated in the next

chapters to facilitate the understanding of the rest of this thesis. The universal scaling and

transport theory of MOSFETs is provided and various scattering mechanism are briefly

discussed. Prospects and possible candidates to enhance the transport of multi-gate devices are

also presented. In addition, mobility extraction methodology used in this thesis is discussed at the

end of this chapter.

Chapter 3 presents the fabrication and stress characterization of novel asymmetrically

strained-Ge and silicon nano-bars/wires with potential transport enhancements for future multi-

31

gate CMOS. Device design, fabrication and characterization of GAA Si NW n-MOSFETs with

and without strain are presented in chapter 4. Detailed intrinsic transconductance and electron

mobility extraction for strained-Si NW n-MOSFETs with various dimensions are provided in this

chapter.

Device design considerations to accurately investigate the hole mobility in Si NW MOSFETs

with a high-κ/metal gate process are presented in chapter 5. An optimized high-κ/ metal gate and

high-temperature hydrogen anneal process is described and the role of hydrogen anneal is

investigated. Chapter 6 investigates the electrical performance of Si NWs with the above process

and detailed hole mobility extraction down to 8 nm NW dimensions is discussed.

Chapter 7 summarizes and concludes the thesis and suggestions for future work to further

enhance the transport in multi-gate NWs are given. In addition, the process and characterization

details are presented in Appendices A-E. Finally, fabrication and hole transport in Si/Ge coreshell NWs is presented in Appendix F.

32

Chapter 2

Thesis Background

This chapter briefly overviews the background physics and methods required to facilitate the

understanding of the rest of this thesis. After an introduction to multi-gate MOSFETs, the

scaling theory of the MOSFET is briefly discussed in section 2.2 of this chapter. Section 2.3

overviews the transport theory and major scattering mechanisms in Si MOSFETs. Possible

transport enhancement solutions for planar and multi-gate MOSFETs are provided in section 2.4,

including discussion of surface orientation and channel direction, strain engineering and new

processes and channel materials. Finally, section 2.5 presents the extraction methodologies to

characterize the carrier mobility in gate-all-around nanowire transistors.

2.1 Introduction to Multi-gate Devices

Conventional bulk Si technology has been the mainstream technology since the beginning of

the CMOS industry. As the channel scales from one generation to the next, increased channel

doping and halo implant are required to control short channel effects. In addition, junction

leakage is a determining factor for the overall off-state leakage. Moreover, the source/drain to

33

bulk capacitive parasitics are more pronounced in aggressively scaled MOSFETs. These parasitic

capacitances are significantly reduced by partially-depleted (PD) Silicon-On-Insulator (SOI)

technology which has been in production by a few groups for low-power applications [26]. On

the other hand, utilizing fully-depleted (FD) SOI technology where the entire channel is depleted

due to the thin Si body, the gate control is significantly enhanced compared to the bulk Si. In

addition to the reduced parasitics and junction leakage, the lightly-doped or undoped Si

minimizes random dopant fluctuations and thus decreases the threshold voltage variation, which

is a concern for nanoscale state-of-the art transistors. Moreover, from the process point of view,

the issues related to halo and implant damage and device isolation are essentially eliminated for

ultra-thin body FD SOI technology compared to the bulk Si process [16].

In order to control short channel effects in planar SOI MOSFETs and maintain reasonable

electrostatics at a given gate length, LG, a critical Si thickness, tSi on the order of LG/3 is required

[27, 28]. As an example, for the 15 nm node technology, a gate length of 15 nm is indicated by

the International Technology Roadmap for Semiconductors (ITRS), which demands a FD-SOI

technology with a Si body thickness of around 5 nm. In addition to manufacturing issues

regarding the control of Si critical thickness dimension, the confinement of carriers results in

degradation of carrier transport (as discussed in section 2.3) and large external resistance.

Therefore, multi-gate devices have been suggested to further relax the critical Si dimension as

well as benefit from the aforementioned FD-SOI device and process technology. For this

purpose, planar double-gate [29], fully DEpleted Lean-channel TrAnsistor (DELTA) [30],

vertical double-gate (FinFET) [31-34], triple-gate (Tri-gate) [35], omega-shaped gate (Ω-gate)

[36], penta-gate [37], Inverted T-channel FET [38], Φ-FET [24], and Gate-All-Around (GAA)

nanowire [21-24], [39-42] have been suggested by various researchers over the past decade.

34

While most of these multi-gate technologies have been experimentally shown to benefit from

excellent electrostatics and short-channel effects, they commonly suffer from a complicated

fabrication process technology compared to planar bulk or SOI technology. Figure 2.1 shows the

device schematic of (a) ultra-thin body planar FD SOI, (b) double-gate FinFET (c) tri-gate and

(d) GAA NW MOSFETs. The critical Si dimensions to sustain acceptable electrostatics [36] are

also presented. It can be seen that the criterion of Si film thickness is successfully relaxed for the

nanowire MOSFET, which is naturally evolved from double-gate FinFET technology.

Figure 2.1: Schematic diagram of the device cross-section, viewed in the direction of the current

transport for (a) planar ultra-thin-body SOI, (b) double-gate FinFET, (c) Tri-gate FET and (d) gate-allaround nanowire FET, representing the evolution of nanowire FET from an ultra-thin-body SOI FET. The

required criterion on the Si thickness (tSi) for a given gate length (LG) to have acceptable electrostatics is

also shown, indicating more relaxed channel dimension available for nanowire FET (compared to other

architectures) to be considered as a candidate for a given technology node.

35

2.2 Scaling Theory of MOSFETs and Advantages of

Nanowires

The scaling behavior and electrostatics of thin-body SOI (single or multi-gate) and gate-allaround nanowire MOSFETs is determined by the surface potential in the channel which results

in the injection of carriers from the source to the drain terminal. The electrostatic potential, Φ, in

the channel can be solved using Poisson’s equation, with a parabolic solution in the form of

equation (2.1) as suggested by Young [27]:

Φ ,

(2.1)

where z and r are directions along and perpendicular to the current direction, respectively. The

1D Poisson’s equation for the surface potential (Φs), for various channel geometries, can be

simplified to:

Φ

Φ

Φ

Φ

(2.2)

where Φg , Φbi, ρ, N and εs are gate and built in potentials, mobile and channel doping densities

and channel permittivity, respectively. The solution to the second-order differential equation

(2.2) has an exponential form given by

Φ

exp (2.3)

where λ is the so called natural length or screening length, representing the length scaled for

channel potential variation. The natural length contains information about the device geometry.

The analytical solutions for double gate and gate-all-around structures are given by equations

(2.4) and (2.5), respectively [43, 44]:

36

εS

2ε

ε tS

4εS t

1

2εS t S ln 1

2

tS t

(2.4)

ε tS

(2.5)

16

where tSi, εSi, tox and εox are the physical thickness and permittivity of Si and dielectric,

respectively. With the scaling parameter, α, defined as

(2.6)

2

there is a universality for scaling of various devices with different architecture or geometries.

Figure 2.2 shows a simulation-based example of the universality of sub-threshold slope and

Drain-Induced-Barrier-Lowering (DIBL) for GAA and double-gate MOSFETs for various oxide

and Si thicknesses [44]. Recent results by Bangsaruntip et al. for short channel GAA Si NWs and

planar FD-SOI MOSFETs also provide experimental evidence for this universality [42].

Figure 2.2: Universal dependence of (a) subthreshold slope and (b) drain-induced-barrier-lowering

(DIBL) on the scaling parameter, for gate-all-around and double-gate MOSFETs with various oxide and

Si thicknesses. Data from Ref. [44].

37