슬라이드 제목 없음

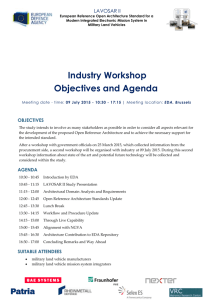

advertisement

EDA Trends on IP-Based Design

1999. 7. 31.

Nak-Woong Eum

EDA Trends on IP-Based Design

nweum

-1-

Contents

▣ Introduction

◈ Co-design versus IP-based design

◈ System level design language initiative

◈ Roadmap of system level design

▣ Trends of Design Reuse

▣ Requirements on IP-Based Design

▣ Trends of IP Design

◈ IP Design Tools

◈ IP Verification

◈ IP Security

▣ Conclusion

EDA Trends on IP-Based Design

nweum

-2-

Introduction

▣ Forecast of SIA (Semiconductor Industry Association)

◈ Silicon density : 58 %/year, but CAD tool capacity : 21%/year

7

◈ Silicon density in 2001 : 10 gates/chip System-on-a-chip (SoC)

▣ New Concept : Design reuse

◈ Reusable Core, Module, or Block : Virtual Component

◈ VC + License (copyright, patent and trade secrete) IP (Intellectual Property)

▣ System Level Design

◈ Co-design : SLDL (System Level Design Language) Initiative

o Deliver an entirely new technology at the front end of the process

o Facilitate reuse by allowing true HW/SW co-design and system constraint budgeting

◈ IP-based design : VSI (Virtual Socket Interface) Alliance

o Establish common standards that will facilitate large-scale design reuse on silicon

o Provide better infrastructure for HW implementation by leveraging existing technologies

EDA Trends on IP-Based Design

nweum

-3-

Introduction

System Level Design ?

▣ Perspectives of Systems

◈ System function

◈ Processing platform on which that system is running

◈ Methodology and process by which the function is mapped onto the platform

▣ SoC may include

◈ Dual DSP/micro-controller chips, the drive toward standard embedded

software/operating systems/hardware platforms

◈ Mapping a system onto a processing platform is not trivial

▣ New approach to SLD (current approach: manual)

◈ Reassigning the division of labor between processors, memory hierarchies, operating

systems, and compilers in order to optimize design cost

▣ Drawbacks of existing languages and methodologies

◈ Model of concurrency requires high overhead when running on a target platform

“System-level design is neither software design nor hardware design, and the languages

and tools for doing them are not applicable at the system level” - Cary Ussery

EDA Trends on IP-Based Design

nweum

-4-

Introduction

Scope of Co-design

▣ Design flow model

co-verification, validation

specification capture

model creation,

description generation

functional specification

design space exploration

transformation, allocation,

partitioning, estimation

specification refinement

memories, interfacing,

arbitration, generation

system-level description

software&hardware design

EDA Trends on IP-Based Design

software synthesis, high-level synthesis,

logic synthesis, ...

nweum

-5-

Introduction

Co-design Research Focus

global system specification and design

specification language

exploration&partitioning&

architecture selection

software interface&

hardware

communication

synthesis

synthesis

synthesis

co-verification

prototype/real product development

property assessment (performance, cost, power, ...)

EDA Trends on IP-Based Design

- by D. Gajski

nweum

-6-

Introduction

System Level Design Language

▣ Requirements and Features for SLDL

◈ Requirements and constraints

o Specify the value and the meaning of the parametric values

o State things in a domain-independent fashion

o Specify cross-domain constraint specification

◈ Hardware/software co-design

o Support abstract performance models of microprocessors, real-time operating systems, and

application algorithms

o Provide semantic consistency for interfaces of performance models regardless of abstraction

level

o Allow smooth transition from system-level into implementation domains

o Establish a structured mapping between an event at the system level and an event, or a set of

events, at the component level

◈ Formal semantics

o Partial specifications permit incomplete descriptions that can be analyzed using formal

consistency techniques

EDA Trends on IP-Based Design

nweum

-7-

Introduction

System Level Design Language (Cont’d)

▣ Phase I :

◈ Cross-domain constraint specifications (timing and operational parameters)

◈ Information flow between components

◈ Structural descriptions of component interaction

▣ Phase II :

◈ Consistent abstractions of time

◈ Consistent semantics for information flow

◈ Integrating several behavioral models

by “Bridging semantics”

Semantic Requirements Cube (S. Schulz)

EDA Trends on IP-Based Design

nweum

-8-

Introduction

System Level Design Language (Cont’d)

SLDL Plug and Play Architecture (S. Schulz)

EDA Trends on IP-Based Design

nweum

-9-

Introduction

System Level Design Language (Cont’d)

▣ Rosetta (www.inmet.com/SLDL)

◈ Sponsored by VHDL International, EDA Industry Council, IEEE DASC, European

CAD Standardization Initiative, and U.S. Air Force Research Labs

◈ Describe SoC design constraints and behavior at architectural levels prior to HW-SW

partitioning

◈ SLDL assisted silicon is scheduled by Q4 2000

▣ VHDL+ (www.eda.org/sid)

◈ VHDL extensions to cover system and interface based design

◈ Proposed by “System and Interface Design” Working Group

◈ Submitted to IEEE NesCom (National Engineering Standards Committee) at April 1999

▣ Suave (www.cs.adelaide.edu.au/~petera)

◈ VHDL extensions for system-level modeling

◈ One of individual experiences

“Considerations on system-level behavioural and structural modeling extensions

to VHDL,” VHDL International Users Forum(VIUF), pp. 42 -50, 1998

EDA Trends on IP-Based Design

nweum

-10-

Introduction

Roadmap of Design & Test - SIA

EDA Trends on IP-Based Design

nweum

-11-

Introduction

Roadmap of System Level Design - SIA

EDA Trends on IP-Based Design

nweum

-12-

▣ Introduction

▣ Trends of Design Reuse

▣ Requirements on IP-Based Design

▣ Trends of IP Design

▣ Conclusion

EDA Trends on IP-Based Design

nweum

-13-

Trends of design reuse

Design Reuse

Mix-and-Match

EDA Trends on IP-Based Design

nweum

-14-

Trends of design reuse

Types of IP (Core, VC)

▣ Soft: Synthesizable RTL HDL

▣ Firm: {Floor-planning + generic library} or {Placement + target library (no

routing)}

▣ Hard: Physical layout

▣ AMS hard: Physical layout + Analog mixed signal specific features

- from VSIA

EDA Trends on IP-Based Design

nweum

-15-

Trends of design reuse

Issues Relating to IP

▣ Standardization of IP Deliverables : A key to mix-and-match

◈ Integration : Interfacing IPs

◈ Verification : Function, performance, fabrication

▣ Marketing

◈ IP marketing strategy, media, license, pricing policy

▣ Security

◈ Tradeoff between accessibility and marketability

▣ Management

◈ Version control, search, backup and interface between CAD tools

Target is design reuse !!

EDA Trends on IP-Based Design

nweum

-16-

Trends of design reuse

Organizations for EDA Standardization

▣ International organizations

◈ IEC (International Electrotechnical Commission) : www.iec.ch

◈ ISO (International Organization for Standardization) : www.iso.ch

▣ Some regional and national organizations

◈ CENELEC(European Committee for Electrotechnical Standardization): www.cenelec.be

◈ ANSI (American National Standards Institute) : www.ansi.org

▣ De facto standard organizations

◈

◈

◈

◈

◈

◈

IEEE (Institute of Electrical and Electronics Engineers) : www.ieee.org

EIA (Electronic Industries Association) : www.eia.org

SI2 (Silicon Integration Initiative, formerly CFI) : www.si2.org

ECSI (European CAD Standardization Initiative) : www.ecsi.org

OVI (Open Verilog International) : www.ovi.org

VI (VHDL International) : www.vhdl.org

See “www.eda.org” for further info.

EDA Trends on IP-Based Design

nweum

-17-

Trends of design reuse

Organizations for IPs

▣ IP Standard Deliverables

◈ VSI Alliance (www.vsi.org) : Jun. 1996

o Establish common standards for large-scale design reuse on silicon

o Provide an infrastructure for HW implementation by leveraging existing technologies

Define, develop, authorize, test and promote open standard specifications

relating to data formats, interfaces, and test methodologies.

▣ IP Business & Marketing

◈ RAPID (www.rapid.org) : Sep. 1996

o RAPID : Reusable Application-Specific Intellectual Property Developers

o IP market research, legal issues and industry activities

◈ Design and Reuse (www.design-reuse.com) : Oct. 1997, A private company but public

o IP yellow pages and IP selector

o IP marketing/sales assistance service

o Tools and services on IP qualification and IP prototyping are scheduled

EDA Trends on IP-Based Design

nweum

-18-

Trends of design reuse

VSI Alliance

▣ Steering Working Group (SWG)

◈ First specification for VC deliverables : “Architectural Document”, Mar. 1997.

▣ Committees : Pilot (PC), Technical (TC), Marketing (MC)

▣ Development Working Groups (DWG): Define details of VC deliverables

◈ System Level Design

o “VSIA System Level Design Model Taxonomy Document”, Jan. 1999.

◈ Manufacturing Related Test

o “Test Data Interchange Formats and Guidelines for VC Providers”, June 1999.

◈ On-chip Busses

o “On-Chip Bus Attributes”, Aug. 1998.

◈ Mixed Signal Design

o “Analog/Mixed-Signal VSIA Extension”, June 1998.

◈ Implementation/Verification

o “Soft and Hard VC Structural, Performance and Physical Modeling”, May 1999.

◈ IP Protection

◈ Virtual Component Transfer

EDA Trends on IP-Based Design

nweum

-19-

Trends of design reuse

VSI Alliance (Cont’d)

▣ VSI-Compliant Chips - Pilot Committee

◈ Applying VSI standards to actual chip development

o Validation of VC documents

o Promotion of VC documents

◈ Do not discriminate membership in the participation

1997

1998

1999

VSI Spec development

Spec adoption

VSI-compliant chips in

production

Milestone of Pilot Project

EDA Trends on IP-Based Design

nweum

-20-

Trends of design reuse

Soft IP Design Flow

From block integration

DEVELOP

specification

for prototype chip

TRANSLATE

Verilog<->VHDL

InterHDL

SYNTHESIZE

to multiple

technologies

Design Compiler

REGRESSION

TEST

translated code

VSS/Verilog/VCS,

ModelSim

RUN gate sim on

one technology

VSS/Verilog/VCS,

ModelSim

RUN TESTS

on multiple

simulatiors

FORMAL

VERIFICATION

RTL vs. gates

Formality

CREATE

user docs

(Datebook)

DESIGN chip

SYNTHSIS chip

Design Compiler

Scan insertion, ATPG,

and coverage analysis

Test Compiler

FLOORPLAN

PLACE

and ROUTE

VERIFY timing

FABRICATE

TEST chip

in demo board

EDA Trends on IP-Based Design

RELEASE

- from RMM

nweum

-21-

Trends of design reuse

Soft IP Productization Flow

- from Mentor Graphics

EDA Trends on IP-Based Design

nweum

-22-

Trends of design reuse

Hard IP Productization Flow

- from Mentor Graphics

EDA Trends on IP-Based Design

GDSII, SPEF, SDF, LEF,

SPICE are also needed to

describe physical data.

nweum

-23-

▣ Introduction

▣ Trends of Design Reuse

▣ Requirements on IP-Based Design

▣ Trends of IP Design

▣ Conclusion

EDA Trends on IP-Based Design

nweum

-24-

Requirements on IP-based design

Requirements on IP-Based Design

▣ Standardization of IP Deliverables

◈ Data format

◈ Test

◈ Interface

▣ IP Verification

▣ Modeling Guideline for Design Reuse

EDA Trends on IP-Based Design

nweum

-25-

Requirements on IP-based design

Deliverables of VC - VSIA

▣

▣

▣

▣

▣

▣

▣

Behavioural model

Emulation model

Test sheet

Synthesizable RTL HDL model

Related Test Bench

Gate level net-list

Test Vector

EDA Trends on IP-Based Design

nweum

-26-

Requirements on IP-based design

Deliverables of VC - VSIA (Cont’d)

EDA Trends on IP-Based Design

nweum

-27-

Requirements on IP-based design

Deliverables of VC - VSIA (Cont’d)

EDA Trends on IP-Based Design

nweum

-28-

Requirements on IP-based design

Data Formats Relating to VC

▣ Standard data formats defined by VSIA

◈

◈

◈

◈

Verilog (IEEE 1364-1995)

VHDL (IEEE 1076-1987)

EDIF (2 0 0)

VC Hspice (1.0) - Avant!

o Structural netlist for transistor level VC

o Connectivity between the devices, not including parastics

◈ VC LEF (1.0) - Cadence

o Physical data for hard VC

o Interface pins, routing obstructions, power and ground connections

◈ GDSII (6 0 0) - Cadence

o Physical implementation of VC

o Used for LVS, DRC, mask generation

◈ SPEF (IEEE P1481, v1.0.4) -SI2

o A part of the Delay and Power Calculation System standard from SI2

o SPEF : Standard Parasitics Exchange Format

o Detailed parasitics on the interface nets of hard VC

EDA Trends on IP-Based Design

nweum

-29-

Requirements on IP-based design

Interfacing IPs

▣ PCB ( = Processor + Peripheral) shrinks to SoC

▣ Interface between HW and HW

◈ FIFO-based interface: I/O

◈ On-chip bus is required

global system specification and design

specification language

exploration&partitioning&

architecture selection

software

synthesis

interface&

communication

synthesis

hardware

synthesis

co-verification

prototype/real product development

property assessment (performance, cost, power, ...)

Co-design research focus

EDA Trends on IP-Based Design

nweum

-30-

Requirements on IP-based design

Interfacing IPs (Cont’d)

▣ On-chip bus : System Bus & Peripheral Bus

▣ Candidates for standard on-chip bus

◈ ARM (www.arm.com)

o ASB(Advanced System Bus) / APB(Advanced Peripheral Bus)

◈ IBM (www.chips.ibm.com)

o PLB(Processor Local Bus) / OPB(On-chip Peripheral Bus)

◈ PALM Chip (www.palmchip.com)

o M Bus / Palm Bus

◈ Mentor Graphics (www.inventra.com)

o FISP Bus

◈ OMI (www.omimo.be)

o PI (Peripheral Interconnect) Bus

◈ Fujitsu (www.fujitsu.com)

o Spcl Bus

Hierarchy of on-chip bus (from VSIA)

EDA Trends on IP-Based Design

nweum

-31-

Requirements on IP-based design

IP Verification

▣ REQUEST (REuse and QUality ESTimation) Project

◈ http://eis.informatik.uni-oldenburg.de

◈ Project Goals

o Raise the level of abstraction for modeling as well as the degree of model reusability.

o Improve the quality of VHDL models in terms of readability, reusability, suitability for further

design steps (synthesis), testability, simulation efficiency, and confidence in validation.

◈ Partners

o

o

o

o

o

o

o

o

o

SIDSA (Spain) - Project leader

Deutsche Telekom AG (Germany)

France Telecom CNET (France)

Italtel (Italy)

Telefonica I+D (Spain)

LEDA Languages for Design Automation (France)

Cadence (formerly: Synthesia, Sweden)

Politecnico di Milano (Italy)

OFFIS (Germany)

EDA Trends on IP-Based Design

nweum

-32-

Requirements on IP-based design

Modeling Guideline

▣ VHDL

◈ Is very powerful and flexible

◈ Support algorithm, timing functionality, and physical structure

◈ Provide a lot of freedom in the choice of modeling styles to describe a single thing

▣ Modeling rules are depend on

◈ Style of the developer

◈ Modeling culture of the company

Interoperability may be poor

▣ Modeling Guideline

◈ Standards

◈ De facto standards

◈ Individual experiences

EDA Trends on IP-Based Design

nweum

-33-

Requirements on IP-based design

Modeling Guideline (Cont’d)

▣ International standard

◈ IEEE 1076.4, “Standard VITAL ASIC Modeling Specification”

o VITAL : VHDL Initiative Towards ASIC Libraries (www.eda.org/vital/)

◈ EIA-567A, “VHDL Hardware Component Modeling and Interface Standard”

o EIA : Electronics Industries Alliance (www.eia.org)

▣ De facto standard

◈ OMI 326, “VHDL Coding Standard”

o OMI : Open Microprocessor systems Initiative

◈ TIREP, “A VHDL Modeling Guide”

o TIREP : Technology Independent Representation of Electronic Products

◈ ESA, “VHDL Modeling Guidelines”

o ESA : European Space Agency

EDA Trends on IP-Based Design

nweum

-34-

Requirements on IP-based design

Modeling Guideline (Cont’d)

▣ Synthesis

◈ IEEE Std 1076.3-1996, “IEEE Standard VHDL Synthesis Packages”

◈ IEEE PAR 1364.1, “Verilog Synthesis Subset”

◈ European VHDL Synthesis Working Group (EVSWG), “Level-0 VHDL Synthesis

Syntax and Semantics”

▣ Simulation

◈ IEEE Std 1164-1991, “IEEE Standard Logic Package”

◈ IEEE 1076.4, “Standard VITAL ASIC Modeling Specification”

◈ ESA, “VHDL Modeling Guidelines” & “VHDL Models for Board-level Simulation”

▣ Test

◈ IEEE Std 1029.1-1991, “Waveform and Vector Exchange Specification (WAVES)”

▣ Analog modeling

◈ IEEE DASC 1076.1, “VHDL-AMS: Analog and Mixed Signal Extensions for VHDL”

▣ Another factors considered previously

◈ FSM, protocol, timing, performance, test bench

EDA Trends on IP-Based Design

nweum

-35-

Requirements on IP-based design

Modeling Guideline (Cont’d)

Status

Guidelines

std

Intended usage

de facto

syn-

simu-

std

thesis

lation

Relation to VHDL

test

full

VITAL

o

o

o

EIA-567A

o

o

o

ESA mod. guide

o

o

o

ESA board-level

o

o

o

OMI 326

o

TIREP

o

VHDL-AMS

o

Synth. 1076.3

o

WAVES

o

Std_logic_1164

o

EDA Trends on IP-Based Design

o

o

o

o

subset

sion

o

o

o

o

o

o

o

o

exten-

o

o

o

nweum

-36-

Requirements on IP-based design

Modeling Guideline for Reuse

▣ Needs :

◈ Consistency, Readability, Portability, Interoperability, Synthesizabiliy in RTL Code

▣ Modeling guideline recommended by Synopsys

◈

◈

◈

◈

◈

Register all outputs (even inputs if possible)

Not latch but flip-Flop

Single edge & single clock

Avoid state dependent timing

Use synchronous RAM

▣ HDL RTL Coding Rules of Synopsys

◈

◈

◈

◈

◈

◈

Naming convention : signal, variable, port name and more

Coding for portability

Guidelines for clocks and resets

Coding for synthesis

Designing with memories

Code profiling

EDA Trends on IP-Based Design

nweum

-37-

▣ Introduction

▣ Trends of Design Reuse

▣ Requirements on IP-Based Design

▣ Trends of IP Design

(IP Design Tools, IP Verification, IP Security)

▣ Conclusion

EDA Trends on IP-Based Design

nweum

-38-

Trends of IP design

IP Design Teamwork

TEST

TEAM

DESIGN

TEAM

SYNTHESIS

TEAM

SPECIFY and DOCUMENT

functional requirements, I/O, timing, performance

area, goals, and test strategy

CREATE behavioral model and test cases

DEVELOP

macro

testbench and

test cases

TEST

SPECIFY

block function, I/O,

timing, test stategy

CODE and

TEST

COORDINATE

timing specs

between blocks

SYNTHESIZE

SYNTHESIZE

CHECK AGAINST EXIT CRITERIA

EDA Trends on IP-Based Design

Macro

Specifications,

behavioral

model

Macro

partitions

and block

specifications

Block

design

Block

integration

- from RMM

nweum

-39-

Trends of IP design

IP Design Tools

▣ CoreBuilder & CoreConsultant (Synopsys)

◈ CoreBuilder : IP creation

◈ CoreConsultant : IP reuse

▣ MORE (Measure Of Reuse Excellence) Program - www.synopsys.com

EDA Trends on IP-Based Design

nweum

-40-

Trends of IP design

IP Verification

- from TransEDA

EDA Trends on IP-Based Design

nweum

-41-

Trends of IP design

IP Verification (Cont’d)

▣ Factors

◈

◈

◈

◈

◈

◈

Modeling Rule Check

Easy of simulation / synthesis

HDL Lint

Code / FSM Coverage

Clock domain analysis

Testability in RT level

RTL Design

(VHDL, Verilog)

Lint

Code Coverage

Integration

FSM Coverage

Synthesis/Timing

SDF

Floorplan

Place & Route

EDA Trends on IP-Based Design

nweum

-42-

Trends of IP design

IP Verification Tools

▣ Modeling guideline

◈ ProVHDL(LEDA), ProVerilog(LEDA), Nova-ExplorerRTL(Avant!)

▣ Lint

◈ VHDLint & VeriLint (Avant!)

▣ Code coverage

◈ Coverit (Avant!), HDLScore (Summit Design), VHDLCover (TransEDA), CoverMeter

(Synopsys), Nova-ExplorerRTL(Avant!)

▣ Testability

◈ Testit (Avant!), DFT Advisor (Synopsys), CoverPlus (TransEDA)

▣ Timing

◈ Nova-ExplorerRTL(Avant!)

▣ Power Analysis

◈ Coolit (Avant!), PowerSure (TransEDA)

EDA Trends on IP-Based Design

nweum

-43-

Trends of IP design

Modeling Guideline Checker

▣ ProVHDL

◈

◈

◈

◈

RMM : reuse

OMI 326 : synthesis, simulation, test

IEEE 1076.3 : synthesis

User customization

- from LEDA

EDA Trends on IP-Based Design

nweum

-44-

Trends of IP design

Lint Analysis

▣ Goal : Purification of RTL code before synthesis and simulation

▣ Checks

◈ Syntax and semantics

◈ Questionable synthesis constructs

◈ Questionable simulation constructs

▣ Reduces design iterations

EDA Trends on IP-Based Design

nweum

-45-

Trends of IP design

Code Coverage Analysis

▣ Goal : Verification of testcases

◈ tightly coupled with a simulator

▣ Captures toggle counts of

◈

◈

◈

◈

signals

variables

execution counts of expressions

conditional branches.

▣ Reports

◈ the switching activity of each testcase

◈ the coverage summary on all testcases

◈ any potential power reduction in the design

EDA Trends on IP-Based Design

nweum

-46-

Trends of IP design

Testability Analysis

▣ Goal : Enhancing the overall testability (Observability & Controllability)

▣ Detects

◈ Design For Test (DFT) rule violations

◈ Questionable testability in RTL code and gate-level netlist

▣ Reports

◈ Uncontrollable clock, reset and memory control signals

◈ Recommendations to fix each DFT violation

EDA Trends on IP-Based Design

nweum

-47-

Trends of IP design

Timing Analysis

Snake path analysis

Clock domain analysis

Asynchronous loop detection

EDA Trends on IP-Based Design

Longest/shortest path analysis

nweum

-48-

Trends of IP design

Power Analysis

▣ Goal : Power analysis at RTL

◈

◈

◈

◈

◈

◈

◈

Find and correct problems early using real RTL code, real circuit activity

Explore package alternatives & make decisions early

Predict performance with multiple usage models

Analyze cooling & mechanical tradeoffs

Ensure IP power characteristics match user’s requirements

Eliminate wasted power

Manage power risk - eliminate re-design

EDA Trends on IP-Based Design

nweum

-49-

Trends of IP design

IP Security

▣

▣

▣

▣

Krypton (www.leda.fr)

CyclopsPro/Gates (www.topdown.com)

Visual IP (www.summit-design.com)

IP Evaluation Kit : Mentor Graphics + GateField + Aptix

◈ Mentor Graphics (http://www.inventra.com/inventra)

◈ GateField (www.gatefield.com)

◈ Aptix (www.aptix.com)

EDA Trends on IP-Based Design

nweum

-50-

Trends of IP design

IP Security (Cont’d)

▣ Krypton (www.leda.fr)

◈ Transforms VHDL input into a functionally equivalent model

o

o

o

o

Names are scrambled and made unreadable (still ASCII)

Constant declarations are removed and their values are propagated throughout the code

All locally static expressions are removed and replaced by their values

Comments are removed and indentations broken

EDA Trends on IP-Based Design

nweum

-51-

Trends of IP design

IP Security (Cont’d)

▣ CyclopsPro/Gates (www.topdown.com)

◈ Generates cycle-based simulation model from VHDL or Verilog netlists

◈ Accelerates simulation 10 to 50 times

◈ Reduces memory demands 70-80%

EDA Trends on IP-Based Design

nweum

-52-

Trends of IP design

IP Security (Cont’d)

▣ Visual IP (www.summit-design.com)

◈

◈

◈

◈

Generates protected simulation model Run-time licensing required

Can controls internal signal visibility

Back annotation of timing via protected SDF files

Simulators supported :

o

o

o

Model Technology's ModelSim

Cadence's Leapfrog and Verilog-XL

Synopsys' VCS and VSS

EDA Trends on IP-Based Design

nweum

-53-

Trends of IP design

IP Security (Cont’d)

▣ IP Evaluation Kit : Mentor Graphics + GateField + Aptix

◈ IP Source : Inventra (Mentor Graphics)

◈ Transportation : Serially numbered IP in a flash-based FPGA (GateField )

o Protects reverse-engineering

◈ Evaluation : Plugging those FPGAs into a reconfigurable prototyping system (Aptix)

o Verify IPs in the target system through MP4

Configuration of the evaluation using System Explorer, MP4 of Aptix

EDA Trends on IP-Based Design

nweum

-54-

Conclusions

▣ Design reuse is important concept.

▣ A reusable block or module can be sold as a product.

Profiles of IP Providers

- from Design and Reuse

EDA Trends on IP-Based Design

nweum

-55-