Relatively Simple CPU and 8085 microprocessor Instruction Set

advertisement

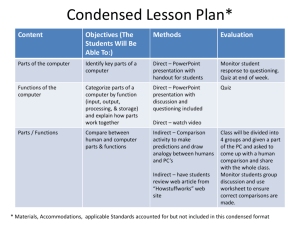

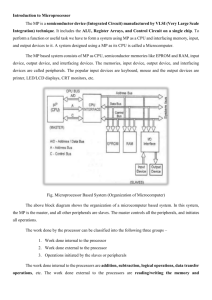

Relatively Simple CPU and 8085 microprocessor Instruction Set Architecture Presented by: Chi Yan Hung Class: Cs 147 - sec 2 Fall 2001 Prof: Sin-Min Lee Topics to cover • Relatively Simple Instruction Set Architecture • 8085 Microprocessor Instruction Set Architecture • Analyzing the 8085 Instruction Set Architecture • Summary Relatively Simple microprocessors, or CPU Designed as an instructional aid and draws its features from several real microprocessors Too limited to run anything as complex as personal computer It has about the right level of complexity to control a microwave oven or other consumer appliance Instruction Set Architecture (ISA) Memory Model Registers Instruction set Memory Model This microprocessor can access 64K ( = 216 ) bytes of memory Each byte has 8 bits, therefore it can access 64K 8 bits of memory 64K of memory is the maximum limit, sometimes a system based on this CPU can have less memory Use memory to map I/O Same instructions to use for accessing I/O devices and memory Registers • Accumulator (AC), is an 8-bit general purpose register • Register R, is an 8-bit general purpose register. It supplies the second operand and also it can be use to store data that the AC will soon need to access. • Flag Z, is an 1-bit zero flag. Z is set to 1 or 0 whenever an instruction is execute • Other registers that cannot be directly accessed by programmer Instruction Set Data movement instructions Data operation instructions Program control instructions • Data movement instruction for the Relatively Simple CPU Instruction Operation NOP No operation LDAC STAC MVAC MOVR AC = M[] M[] = AC R = AC AC = R AC – accumulator register R – general purpose register /M[] – 16-bit memory address • NOP -- performs no operation • LDAC -- loads data from memory and stores it in the AC • STAC -- copies data from AC to memory location • MVAC -- copies data in AC to register R • MOVR -- copies data from R to AC • Data operation instruction for the Relatively Simple CPU Instruction Operation ADD SUB INAC CLAC AC = AC + R, If (AC + R = 0) Then Z = 1 Else Z = 0 AC = AC - R, If (AC - R = 0) Then Z = 1 Else Z = 0 AC = AC + 1, If (AC + 1 = 0) Then Z = 1 Else Z = 0 AC = 0, Z = 1 AND OR XOR AC = AC R, If (AC R = 0) Then Z = 1 Else Z = 0 AC = AC R, If (AC R = 0) Then Z = 1 Else Z = 0 AC = AC R, If (AC R = 0) Then Z = 1 Else Z = 0 NOT AC = AC, If (AC = 0) Then Z = 1 Else Z = 0 AC – accumulator register Z – zero flag R – general purpose register • Program control instruction for the Relatively Simple CPU Instruction Operation JUMP JMPZ GOTO If (Z = 1) Then GOTO JPNZ If (Z = 0) Then GOTO Z – zero flag -- 16-bit memory address Note: • Each instruction is having an 8-bit instruction code. • LDAC, STAC, JUMP, JUMPZ, and JPNZ instructions all require a 16-bit memory address, represented by /M[]. These instructions each require 3 bytes in memory. Instruction formats for the Relatively Simple CPU byte 1 Instruction code byte 2 Low-order 8 bits of byte 3 High-order 8 bits of Example: 25: JUMP 1234 H instruction stored in memory: 25th byte 25: 0000 0101 26th byte 26: 0011 0100 27th byte 27: 0001 0010 H -- in hexadecimal format (JUMP) (34H) (12H) • Example program using Relatively Simple CPU coding The Algorithm of the program 1: total = 0, i = 0 2: i=i+1 3: total = total + i 4: IF i n THEN GOTO 2 What exactly this algorithm doing is: 1+ 2 + … + (n – 1) + n The Relatively Simple CPU coding of the program CLAC STAC total STAC i Loop: LDAC i INAC STAC i MVAC LDAC total ADD STAC total LDAC n SUB JPNZ Loop total = 0, i = 0 i = i +1 total = total +1 IF i n THEN GOTO Loop Relatively Simple microprocessors, or CPU Designed as an instructional aid and draws its features from several real microprocessors Too limited to run anything as complex as personal computer It has about the right level of complexity to control a microwave oven or other consumer appliance Instruction Set Architecture (ISA) Memory Model Registers Set Instruction Set Memory Model This microprocessor is a complete 8-bit parallel Central Processing Unit (CPU). Each byte has 8 bits Isolated I/O, input and output devices are treated as being separate from memory. Different instructions access memory and I/O devices Register Set • • • • • Accumulator A, is an 8-bit register. Register B, C, D, E, H, and L, are six 8-bit general purpose register. These registers can be accessed individually, or can be accessed in pairs. Pairs are not arbitrary; BC are a pair (16- bit), as are DE, and HL Register HL is used to point to a memory location. Stack pointer, SP, is an 16-bit register, which contains the address of the top of the stack. • • • • • The sign flag, S, indicates the sign of a value calculated by an arithmetic or logical instruction. The zero flag, Z, is set to 1 if an arithmetic or logical operation produces a result of 0; otherwise set to 0. The parity flag, P, is set to 1 if the result of an arithmetic or logical operation has an even number of 1’s; otherwise it is set to 0. The carry flag, CY, is set when an arithmetic operation generates a carry out. The auxiliary carry flag, AC, very similar to CY, but it denotes a carry from the lower half of the result to the upper half. • The interrupt mask, IM, used to enable and disable interrupts, and to check for pending interrupts Instruction Set Data movement instructions Data operation instructions Program control instructions Data movement instruction for the 8085 microprocessor Instruction MOV r1, r2 Operation r1 = r2 LDA STA PUSH rp PUSH PSW POP rp POP PSW IN n OUT n A = M[] M[] = A Stack = rp (rp SP) Stack = A, flag register rp = Stack (rp SP) A, flag register = Stack A = input port n Output port n =A r, r1, r2 – any 8-bits register / M[] – memory location rp – register pair BC, DE, HL, SP(Stack pointer) n – 8-bit address or data value Data operation instruction for the 8085 microprocessor Instruction Operation Flags ADD r ADD M INR r IN M DCR n DCR M XRA M CMP r CMA A=A+r A = A + M[HL] r=r+1 M[HL] = M[HL] + 1 r=r-1 M[HL] = M[HL] - 1 All All Not CY Not CY Not CY Not CY All All None CY – carry flag A = A M[HL] Compare A and r A = A Program control instruction for the 8085 microprocessor Instruction Operation JUMP Jcond CALL GOTO If condition is true then GOTO Call subroutine at Ccond RET Rcond If condition is true then call subroutine at Return from subroutine If condition is true then return from subroutine cond – conditional instructions NZ (Z = 0) Z (Z = 1) P (S = 0) N (S = 1) PO (P = 0) PE (P = 1) NC (CY = 0) C (CY = 1) Z – zero flag, S – sign flag, P – parity flag, C – carry flag Note: • Each instruction is having an 8-bit instruction code. • Some instructions have fields to specify registers, while others are fixed. Instruction formats for the Relatively Simple CPU byte 1 byte 2 Two-byte Instruction code value Example: 25: MVI r, n instruction stored in memory: 25th byte 25: 00xxx110 26th byte 26: xxxx xxxx Specifies r (MVI r) (low-order memory) byte 1 Three-byte byte 2 byte 3 Instruction code Low-order 8 bits High-order 8 bits Example: Example: 25: 25: MOV rp, r1,r2 LXI instruction instructionstored storedininmemory: memory: 25th 25thbyte byte 25: 25: 00rp 00000001 0001 26th 26thbyte byte 26: 26: xxxx xxxxxxxx xxxx 27th 27thbyte byte 27: 27: yyyy yyyyyyyy yyyy memory) Specifies rp (LXI (MOV) rp) (low-order (specifies memory) r1) (high-order (specifies r2) • Example program using 8085 microprocessor coding The Algorithm of the program 1: total = 0, i = 0 2: i=i+1 n + (n - 1) + … + 1 3: total = total + i 4: IF i n THEN GOTO 2 The 8085 coding of the program LDA n i=n MOV B, A XRA A sum = A A = 0 Loop: ADD B sum = sum + i DCR B JNZ Loop STA total i=i-1 IF i 0 THEN GOTO Loop total = sum Analyzing the 8085 ISA The 8085 CPU’s instruction set is more complete than that of the Relatively Simple CPU. More suitable for consumer appliance. Too limited to run anything as complex as personal computer Advantages of the 8085’s ISA vs. Relative Simple CPU It has the ability to use subroutines It can incorporate interrupts, and it has everything the programmer needs in order to process interrupts. The register set for the 8085 is mostly sufficient, thus less coding apply which will improve task completion. The instruction set is fairly orthogonal. E.g. no clear accumulator instruction Disadvantages of the 8085’s ISA Like the Relatively Simple CPU, it cannot easily process floating point data. Summary of ISA 1. The ISA specifies a. an instruction set that the CPU can process b. its user accessible registers c. how it interacts with memory 2. The ISA does not specify how the CPU is designed, but it specifies what it must be able to do. 3. The ISA is concerned only with the machine language of a microprocessor because CPU only executes machine language program, not any kind of high-level program. 4. When designing an ISA, an important goal is completeness: a. instruction set should include the instructions needed to program all desired tasks. b. instruction should be orthogonal, minimizing overlap, reducing the digital logic without reducing its capabilities within the CPU. c. CPU should includes enough registers to minimize memory accesses, and improve performance. 5. An ISA should specifies the types of data the instruction set to process. 6. An ISA should specifies the addressing modes each instruction can use 7. An ISA should specifies the format for each instruction THE END