S8 HV MOS CHARACTERIZATION

advertisement

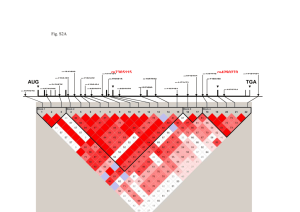

“LAYOUT” EFFECTS HOW LAYOUTS CAN CHANGE CMOS AND HOW DO CIRCUIT SIMULATIONS ACCOUNT FOR THE CHANGE BOB PEDDENPOHL MODELING MANAGER CYPRESS MODELING CENTER LEXINGTON, KY 04/04/07 AGENDA (ACRONYM TEST) BSIM BASICS, NEW FEATURES BERKLEY SHORT CHANNEL IGFET MODEL STI EFFECT OR LOD EFFECT SHALLOW TRENCH ISOLATION OR LENGTH OF DIFFUSION WPE WELL PROXIMITY EFFECTS OPC OPTICAL PROXIMITY CORRECTION 2 Cypress Confidential AGENDA BSIM BASICS, NEW FEATURES LENGTH-OF-DIFFUSION (LOD) WELL PROXIMITY EFFECTS (WPE) OPTICAL PROXIMITY CORRECTION (OPC) 3 Cypress Confidential BSIM BASICS SPICE SIMULATION OF MOS (ONLY APPROXIMATIONS!) HAND CALC: Ids = width/length * Cox * Mobility * (Vgs – Vth - Vdsat) * Vds SPICE CALC: Ids = w/l * 1/TOX * U0 * (Vgs – VTH0 – VDSAT) * Vds TERMINOLOGY SPICE MODEL PARAMETERS (BSIM3 PARAMETERS) INSTANCE PARAMETERS SIMULATION PARAMETERS (BIAS CONDITIONS) MODEL EXAMPLE: .model nshort.1 nmos TOX = 4.19e-9 NETLIST EXAMPLE: m1 d g s b nshort w =25 l=0.5 m=1 ad=50 pd=27..delvth0=0.0 sa=1.04 sb=1.04 v1 g s 1.8 v2 d s 0.9 v3 b s 0.0 COMMAND RUN EXAMPLE spectre mynetlist.scs WAVEFORM VIEWER TO REVIEW SPECTRE OUTPUT FILES 4 Cypress Confidential BSIM3 VS BSIM4 WHAT ARE UPGRADES IN BSIM4? LOD WPE RF MODELING IMPROVEMENTS BSIM: http://www-device.eecs.berkeley.edu/~bsim3/ BSIM = BERKELEY SHORT-CHANNEL IGFET MODEL 5 Cypress Confidential MODEL DEVELOPMENT PROCESS SELECT “GOLDEN” WAFER MEASUREMENT (DC, AC, TRAN) EXTRACT WAFER CASE MODEL RO MEAS = RO SIMS CENTER TO EDR NOMINAL (TT) SKEW MODELS (FF, SS, FS, SF) QA & RELEASE TO DESIGN 6 Cypress Confidential AGENDA BSIM BASICS, NEW FEATURES LENGTH-OF-DIFFUSION (LOD) WELL PROXIMITY EFFECTS (WPE) OPTICAL PROXIMITY CORRECTION (OPC) 7 Cypress Confidential LAYOUT CHOICES & LOD BEST VALUE FOR Sa, Sb? WHY BIGGER DIFFUSIONS? Sa Sb Sa Sb Sa 8 Cypress Confidential Sb MEASURED DATA VTH DUE TO STI STRESS Sa, Sb Instance params for LOD Sa Sb Sa Sb Nmos VTH Variation Optical Effect and STI Effect 0.70 0.69 STI Effect VTH 0.68 0.67 Site1 0.66 Site2 0.65 Site4 0.64 Proximity Effect 0.63 0.62 Width=7 P ro xB ars# 2 LOD=1.04 9 Width=7 P ro xB ars# 1 LOD=1.04 Width=7 P ro xB ars# 0 LOD=1.04 Width=7 P ro xB ars# 0 LOD=0.925 Cypress Confidential Width=7 P ro xB ars# 0 LOD=0.68 Width=7 P ro xB ars# 0 LOD=0.28 LOD MODEL EQUATIONS Sa ELECTRICAL PARAM SPICE/MODEL EQN (APPROX) MODEL FITTING CURVE Vth VTH0 + KVTH0 Vth vs Sa, Sb Vth w/ Vbs Vth + K2 + STK2 Vth@Vbs vs Sa, Sb Ids_linear (Ids vs Vds) Mobility = U0 + KU0 Idslin vs Sa, Sb Ids_sat Vsat = VSAT + KVSAT Ids vs Sa,Sb Rout (Output Resistance) Rout = 1/Gds + STETA0 Rout vs Sa,Sb STRESS MODEL PARAMETERS f(Sa,Sb) 10 Cypress Confidential Sb SPICE WITH LOD EFFECTS BEST VALUE FOR Sa, Sb? WHY? Sa 11 Sb Sa Sb NETLIST WITH LOD m1 d g s b nshort w =25 l=0.5 m=1 ad=50 pd=27..delvth0=0.0 sa=1.04 sb=1.04 IDS SPICE APPROX WITH LOD SPICE CALC: Ids = w/l * 1/TOX * (U0 + KU0) * (Vgs – VTH0 – VDSAT) * Vds ALTERNATIVES TO MODELING? MODEL INSTANCE PARAMETERS + MODEL PARAMETERS DRC ENFORCE SINGLE SA, SB VALUE ALLOWED CORNER MODELS PUT WIDER VARIATION INTO MODEL ADVANTAGES/DISADVANTAGES? SIMULATION TIME & ACCURACY, MODEL DEVELOPMENT TIME SILICON AREA INCREASES Cypress Confidential AGENDA BSIM BASICS, NEW FEATURES LENGTH-OF-DIFFUSION (LOD) WELL PROXIMITY EFFECTS (WPE) OPTICAL PROXIMITY CORRECTION (OPC) 12 Cypress Confidential WPE BACKGROUND 0.74 nwell 0.73 Vth 0.72 Wspc 0.71 0.7 0.69 Wspc 0.68 0.67 0 2 4 6 Wspc 13 WHAT’S THE CAUSE? http://www.ieee-cicc.org/06-8-6.pdf Cypress Confidential 8 RECALL PROCESSING STEPS 14 Cypress Confidential NWELL IMPLANT EFFECTS CMOS 15 HIGH ENERGY ATOMS BOUNCE OFF PHOTORESIST http://www.ieee-cicc.org/06-8-6.pdf (see paper diagrams) WHY WPE NOW? SPICE MODEL OF WPE REFERENCE: HIGH ENERGY IMPLANTERS WANT DEEP IMPLANT LOW RES PATH SUPRESS BJT LATCHUP Vth = VTH0 + KVTHOWE*(sca+WEB*scb + WEC*scc) Vth@Vbs = K2 + K2WE * (sca + WEB*scb +WEC*scc) Mobility = U0 * (1+KU0WE*(sca + WEB*scb+WEC*scc) COMPACT MODEL COUNCIL WEBSITE BSIM4 MANUAL FROM BERKELEY WEBSITE Cypress Confidential SPICE WITH WPE EFFECTS nwell INSTANCE PARAMS ALL FUNCTION Wspc Sca, scb, scc Wspc ELECTRICAL PARAM SPICE/MODEL EQN (APPROX) MODEL FITTING CURVE Vth VTH0 + KVTHOWE*(sca+WEB*scb + WEC*scc) Vth vs sca,scb,scc Vth w/ Vbs Vth + K2 + K2WE * (sca + WEB*scb +WEC*scc) Vth@Vbs vs sca,scb,scc Mobility U0 * (1+KU0WE*(sca+WEB*scb+WEC*scc) IDS Lin vs sca,scb,scc NETLIST WITH WPE m1 d g s b nshort w =25 l=0.5 m=1 ad=50 pd=27..delvth0=0.0 sca=1.1 scb=0.5, scc=3 16 IDS SPICE APPROX WITH WPE ADVANTAGES/DISADVANTAGES/ALTERNATIVES? SPICE: Ids = w/l * 1/TOX * (U0 + f(KU0WE) * (Vgs – VTHO + f(KVTHOWE) – Vdsat) * Vds Cypress Confidential AGENDA BSIM BASICS, NEW FEATURES LENGTH-OF-DIFFUSION (LOD) WELL PROXIMITY EFFECTS (WPE) OPTICAL PROXIMITY CORRECTION (OPC) 17 Cypress Confidential RF FET Modules Layout With poly proximity bars M=2 M=4 Standard Layout Without poly proximity bars Is performance the same? 18 Cypress Confidential OPC BACKGROUND OPTICAL PROXIMITY CORRECTION (OPC) DURING LIGHT EXPOSING OF PHOTORESIST FINAL SHAPES ON SILICON NOT MATCH DRAWN SHAPES BASED ON SURROUNDING ENVIRONMENT With proximity bars Standard Layout Without proximity bars 19 Cypress Confidential MEASURED DATA VTH DUE TO STI STRESS Sa, Sb Instance params for LOD Sa Sb Sa Sb Nmos VTH Variation Optical Effect and STI Effect 0.70 0.69 STI Effect VTH 0.68 0.67 Site1 0.66 Site2 0.65 Site4 0.64 Proximity Effect 0.63 0.62 Width=7 P ro xB ars# 2 LOD=1.04 20 Width=7 P ro xB ars# 1 LOD=1.04 Width=7 P ro xB ars# 0 LOD=1.04 Width=7 P ro xB ars# 0 LOD=0.925 Cypress Confidential Width=7 P ro xB ars# 0 LOD=0.68 Width=7 P ro xB ars# 0 LOD=0.28 MEASURED DATA VTH DUE TO PROXIMITY AND STI STRESS Nmos VTH Variation Optical Effect and STI Effect 0.70 0.69 STI Effect VTH 0.68 0.67 Site1 0.66 Site2 0.65 Site4 Proximity Effect 0.64 0.63 0.62 Width=7 P ro xB ars# 2 LOD=1.04 21 Width=7 P ro xB ars# 1 LOD=1.04 Width=7 P ro xB ars# 0 LOD=1.04 Width=7 P ro xB ars# 0 LOD=0.925 Cypress Confidential Width=7 P ro xB ars# 0 LOD=0.68 Width=7 P ro xB ars# 0 LOD=0.28 DRAWN NOT EQUAL FINAL OPC “SIMULATION” TOOL IN: LAYOUT, OUT: POLY SHAPES Lcenter Ledge Ltrans 22 W/L/M Lcenter Ledge Ltrans 3/0.15/2 0.15 0.214 0.17 Cypress Confidential M=2 AND M=4 COMPARISON W/L/M Lcenter Ledge Ltrans 3/0.15/2 0.15 0.214 0.17 3/0.15/4 (edge) 0.15 0.204 0.185 3/0.15/4 (center) 0.15 0.234 0.185 23 Cypress Confidential SAME DRAWN L, BUT SILICON VARIES DESIGNING WITH OPC 24 NO SPICE MODEL EFFECT RELY ON CLDRC, NOT PERFECT ACCOUNT FOR IN YOUR DESIGN? L(DRAWN) = L(SI) Cypress Confidential MEASURED DATA VTH DUE TO PROXIMITY AND STI STRESS Sa Sb Sa Sb Nmos VTH Variation Optical Effect and STI Effect 0.70 0.69 STI Effect VTH 0.68 0.67 Site1 0.66 Site2 0.65 Site4 Proximity Effect 0.64 0.63 0.62 Width=7 P ro xB ars# 2 LOD=1.04 25 Width=7 P ro xB ars# 1 LOD=1.04 Width=7 P ro xB ars# 0 LOD=1.04 Width=7 P ro xB ars# 0 LOD=0.925 Cypress Confidential Width=7 P ro xB ars# 0 LOD=0.68 Width=7 P ro xB ars# 0 LOD=0.28 CONCLUSIONS LOD/WPE IMPACT TRANSISTOR PERFORMANCE, ACCOUNT FOR BY: NEW PHYSICAL EFFECTS RELY HEAVILY ON INSTANCE PARAMETERS OR CLDRC MODEL ACCURATE AT COST OF MODEL DEVELOPMENT DRC RULES EASIER DESIGN KIT AT COST OF AREA INTERACTION OF THE MODEL WITH CAD TOOLS 26 GOOD DESIGNER: LIMIT THESE EFFECTS AS MUCH AS POSSIBLE IN LAYOUT REVIEW MODELS TO ENSURE EFFECTS ARE INCLUDED Cypress Confidential APPENDIX EXECUTIVE SUMMARY PROBLEM STATEMENT TRANSISTOR PARAMETRIC SHIFTS DUE TO PROXIMITY EFFECTS PHOTO/ETCH: DENSE VS ISOLATED STI STRESS: POLY-STI EDGE SPACING WHAT WAS DONE ELECT/OPTICAL CHAR OF DENSE VS ISOLATED ON L8 PHOTO/ETCH VS STI STRESS CHAR ON S8 WHAT NEEDS TO BE DONE (TO BE FORMALIZED) WHAT LIST OF TEST STRUCTURES TO QUANTIFY IMPACT TEST STRUCTURES MODELING TEST STRUCTURES PLACEMENT ON L8/S8 FRAMES WHO SBJ PED JFE OPC METHODOLOGY FOR ISO/DENSE CONSISTENCY FNG TECHNOLOGY MODELING 28 TECHNIQUES FOR STRESS RELIEF TDR RULES FOR MIN LOD, FIXED LAYOUT METHODOLOGY UPDATE FOR STRESS PARAMETER EXTRACTION IN BSIM4 Cypress Confidential HRP PED MEASUREMENTS: COMPLETE MOS 29 FET DC (VTH0, RDSW) FET AC (CGDO,DLC) DIODE DC (JS,JSW) DIODE AC (CJ, CJSW) Cypress Confidential Stress Equations in Model Measurements done by SBJ As NMOS gets closer to STI Edge, VT Increases, IDS and Gm Decrease As PMOS gets closer to STI Edge, |VT| Decreases, IDS and Gm Increase. STI induced Stress degrades NMOS and enhances PMOS characteristics (why enhanced?) More measurements are planned. Data is plotted for # of proximity bars and length of diffusion (LOD). 30 Cypress Confidential W=3.01 L=0.15 M2 L = 0.158-0.008=0.15um at center L=0.222-0.008 = 0.214um at edge Transition region from edge before L becomes 0.15um 0.17um Impact will be larger for W=1.65 31 Cypress Confidential W=3.01 L=0.15 M4 L = 0.158-0.008=0.15um at center L=0.232-0.008 = 0.234um at edge of center two fingers L=0.212-0.008 = 0.204um at edge of outer fingers Transition region from edge before L becomes 0.15-0.155um = 0.185um 32 Cypress Confidential