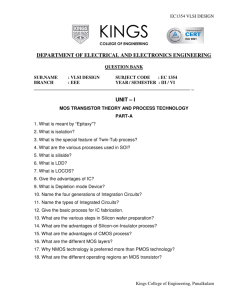

Question Bank VLSI

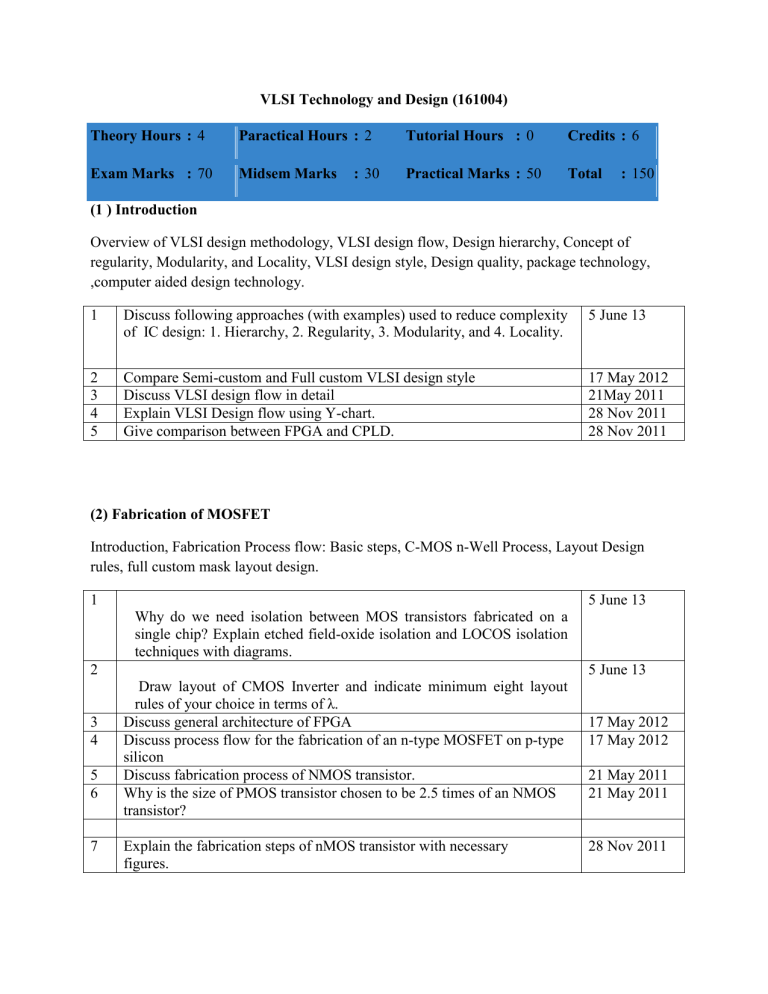

VLSI Technology and Design (161004)

Theory Hours : 4

Exam Marks : 70

(1 ) Introduction

Paractical Hours : 2

Midsem Marks : 30

Tutorial Hours : 0

Practical Marks : 50

Credits : 6

Total : 150

Overview of VLSI design methodology, VLSI design flow, Design hierarchy, Concept of regularity, Modularity, and Locality, VLSI design style, Design quality, package technology,

,computer aided design technology.

1 Discuss following approaches (with examples) used to reduce complexity of IC design: 1. Hierarchy, 2. Regularity, 3. Modularity, and 4. Locality.

2 Compare Semi-custom and Full custom VLSI design style

3 Discuss VLSI design flow in detail

4 Explain VLSI Design flow using Y-chart.

5 Give comparison between FPGA and CPLD.

5 June 13

17 May 2012

21May 2011

28 Nov 2011

28 Nov 2011

(2) Fabrication of MOSFET

Introduction, Fabrication Process flow: Basic steps, C-MOS n-Well Process, Layout Design rules, full custom mask layout design.

1

Why do we need isolation between MOS transistors fabricated on a single chip? Explain etched field-oxide isolation and LOCOS isolation techniques with diagrams.

2

Draw layout of CMOS Inverter and indicate minimum eight layout rules of your choice in terms of λ.

3 Discuss general architecture of FPGA

4 Discuss process flow for the fabrication of an n-type MOSFET on p-type silicon

5 Discuss fabrication process of NMOS transistor.

6 Why is the size of PMOS transistor chosen to be 2.5 times of an NMOS transistor?

7 Explain the fabrication steps of nMOS transistor with necessary figures.

5 June 13

5 June 13

17 May 2012

17 May 2012

21 May 2011

21 May 2011

28 Nov 2011

(3) MOS Transistor

The Metal Oxide Semiconductor (MOS) structure, The MOS System under external bias,

Structure and Operation of MOS transistor, MOSFET Current- Voltage characteristics, MOSFET scaling and small-geometry effects, MOSFET capacitances

1

Derive expression for the maximum possible depth of the depletion region in two-terminal MOS structure.

2 Calculate the threshold voltage for a polysilicon gate nMOS transistor with the following parameters: NA = 2 x 1016 cm-3, ND = 2 x 1019 cm-3, tox = 300 x 10-8 cm, and Nox = 1010 cm-2. Take kT/q = 26 mV, ni = 1.45 x 1010 cm-3, q = 1.6 x 10-19 C, εox = 3.97 x 8.85 x 10-14 F/cm, εsi =

11.7 x 8.85 x 10-14 F/cm.

3 What do you understand by gradual channel approximation? Derive expression for the drain current flowing through n-channel MOSFET as a function of VGS, VDS, and VBS.

4 Explain constant field scaling device reduction strategy and show that the power density does not change in a device scaled using this technique.

5 Explain Band Diagram of the MOS structure, at surface Inversion. Derive the expression of threshold Voltage.

6 Calculate the threshold voltage VTO at VSB = 0, for a polysilicon gate nchannel

MOS transistor, with the following parameters: Substrate doping density NA =1016 cm-3, polysilicon gate density ND =2 x 1020 cm-3, gate oxide thickness tox=500 Angstrom and oxide interface fixed charge density Nox= 4 x 1010 cm-2, φF( gate) = 0.55V. Physical constants :

Thermal voltage =KT/q = 0.026 volt

Energy Gap of silicon(Si) =Eg = 1.12 eV

Intrinsic Carrier Concentration of silicon = ni =1.45 x 1010 cm –3

Dielectric constant of vaccume = εo =8.85 x 10-14 F/cm

Dielectric constant of silicon = εsi = 11.7 x εo F/cm

Dielectric constant of silicon dioxide = εox = 3.97 x εo F/cm

7 Discuss procedure to measure data for experimental determination of the

Parameters kn, VTO and substrate bias coefficient.

8 Define or briefly discuss following: (MIX CHAPTER)

1. Narrow channel effect

2. Observability in testing

3. Causes for chip reliability

4. Negative photoresist

5. Need of H-tree Clock distribution network

6. Power delay product

7. Need of Domino CMOS logic

9 Define and briefly discuss following. (MIX CHAPTER)

1. Yield

5 June 13

5 June 13

5 June 13

5 June 13

17 May 2012

17 May 2012

17 May 2012

17 May 2012

17 May 2012

2. Positive photoresist

3. Substrate bias effect (body effect)

4. Noise margin

5. Master –slave flip-flop

6. Controllability in testing

7. PLD

10 Explain the band diagram of MOS Structure at surface inversion and derive the expression for threshold voltage.

11 Consider a MOS system with the following parameters: tox =200Aº ,

ΦGC = - 0.85 V,

NA= 2*1015 cm-3,

Qox= q* 2 *1011 C/cm2

07

1) Determine the threshold voltage V under zero bias at room temperature

(T = 300 ºK). Note that εox=3.97ev and εsi=11.7ev.

2) Determine the type (p-type or n-type) and amount of implant.

12 With neat sketch explain gradual channel approximation and derive the equation for drain current in linear region mode and saturation mode.

13 Effect of channel length modulation and substrate bias on drain current of

NMOS transistor

14 Derive threshold voltage equation for short channel effect.

15 Derive the drain current equation for MOSFET using Gradual

Channel Approximation (GCA).

16 Consider a MOS system with the following parameters: tox = 200 Ǻ

φGC = -0.85 V

NA = 2 x 1015 cm-3

Qox = q x 2 x 1011 C/cm2

Determine the threshold voltage VTO under zero bias at room temperature. Note that εox = 3.97ε0 and εsi = 11.7 ε0.

21 May 2011

21 May 2011

21 May 2011

21 May 2011

21 May 2011

28 Nov 2011

28 Nov 2011

(4) MOS Inverters: Static characteristics

Introduction, Resistive load Inverter, Inverter with n-type MOSFET load (Enhancement and

Depletion type MOSFET load), CMOS Inverter

1 5 June 13

Derive expressions for VIH and VIL for CMOS Inverter

2 Draw the CMOS Inverter circuit and Voltage Transfer Characteristic

(VTC) for different operating regions of the nMOS and pMOS transistors.

Derive critical voltage points VIL,VIH.

3 Discuss the effect of supply voltage scaling on VTC (voltage transfer characteristic) of CMOS Inverter. What is the minimum VDD below which VTC exhibits hysteresis effect?

17 May 2012

5 June 13

4 Consider a CMOS Inverter circuit with the following parameters:

VDD=3.3V, VTO,n=0.6V , VTO,p= - 0.7V, kn=200 μA/V2, kp=80

μA/V2.Calculate the noise margin of the circuit.

5 Draw circuit of resistive load inverter. Derive VIH , VIL ,VOL and VOH for resistive load inverter.

7 Design a resistive load inverter with R = 1k>, such that VOL = 0.6V.

The enhancement-type nMOS driver transistor has the following parameters:

VDD = 5.0V

VTO = 1.0 V

γ = 0.2 V1/2

λ = 0

μnCox = 22.0 μA/V2 a. Determine the required aspect ratio, W/L. b. Determine VIL and VIH.

8 Draw the inverter circuit with depletion type nMOS load. Mention the operating regions of driver and load transistors for different input voltages. Derive critical voltage points VOH, VOL and VIL for depletion- load nMOS inverter.

9 Explain two input depletion load NOR gate and derive the necessary equations for the same.

(5) MOS Inverters Switching characteristics and Interconnect Effects

17 May 2012

21 May 2011

28 Nov 2011

28 Nov 2011

28 Nov 2011

Introduction, Delay-time definitions, Calculation of Delay times, Inverter design with delay constraints, Estimation of Interconnect Parasitic, Calculation of interconnect delay, Switching

Power Dissipation of CMOS Inverters

1

Define propagation delay and derive expression for τPHL for CMOS

Inverter. Assume ideal step as an input to CMOS Inverter.

2 Draw input and output waveform during high to low transition of output for a CMOS inverter and derive expression for τPHL

3 Draw and discuss three stage ring oscillator circuit.

4 Design of a depletion-load NMOS inverter:

μncox= 30 μA/V2 ,

VT0 = 0.8 V (enhancement-type),

VT0 = - 2.8 V,(depletion-type),

γ= 0.38 V1/2,

|2 ΦF| = 0.6 V,

VDD = 5 V.

07

1) Determine the (W/L) ratios of both transistors such that: i) the static (DC) power dissipation for Vin = VOH is 250 μW, and ii) VOL = 0.3 V.

5 June 13

17 May 2012

17 May 2012

2) Calculate VIL and VIH values, and determine the noise margins

5 Consider a CMOS inverter circuit with the following parameters:

VDD = 3.3 V,

For NMOS VTO, n = 0.6 V, μn Cox=60 μ A/V2 , (W/L)n=8

For PMOS VTO, p = - 0.7 V, μp Cox=25 μ A/V2 , (W/L)p=12.

Calculate noise margin and Vth of the circuit.

6 How will you calculate propagation delay times tpHL and tpLH for

CMOS Inverter?

7 Write a note on CMOS Ring Oscillator circuit.

8 Draw input and output waveforms during high to low transition of output for a CMOS inverter. Derive expression for τPHL.

21 May 2011

21 May 2011

28 Nov 2011

28 Nov 2011