Sequential Networks

advertisement

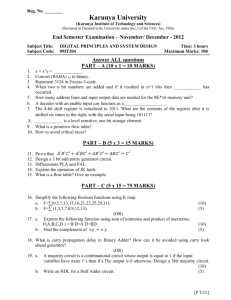

Sequential logic networks V. Sequential network design State-machine structure (Mealy) output depends on state and input typically edge-triggered D flip-flops 1 Sequential logic networks V. Sequential network design State-machine structure (Moore) output depends on state only typically edge-triggered D flip-flops 2 Sequential logic networks V. Sequential network design Flip Flop : summary D Flip flop q : Current state D S-R Flip flop S Q Q : Next state C Characteristic Table Characteristic Equation D q Q 0 0 1 1 0 0 1 1 0 1 0 1 q Q=D SR J Q R Q’ J-K Flip flop C Q K Q’ Q’ C S R q Q J K q Q 0 0 0 0 1 1 1 1 0 1 0 0 1 1 --- 0 0 0 0 1 1 1 1 0 1 0 0 1 1 1 0 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 00 01 0 1 1 11 10 d 1 d 1 Q = S + R’q q 0 0 1 1 0 0 1 1 JK 0 1 0 1 0 1 0 1 00 01 0 11 10 1 1 1 1 1 Q = Jq’ + K’q Transition Table (Excitation Table) 3 q Q D qQ SR qQ JK 00 01 10 11 0 1 0 1 00 01 10 11 0 1 0 d 00 01 10 11 0 1 d d d 0 1 0 d d 1 0 Sequential logic networks V. Sequential network design Flip Flop : summary Characteristic table : For each input and state combination, define the next state of the flip flop Characteristic equation: Define the next state (Q) as a function of current state and input to the flip flop Transition table (excitation table): For each transition type, define the inputs that cause the transition 4 Sequential logic networks V. Sequential network design Major design steps Step 1: Start from state diagram or word description Step 2: Construct a State/Output table Moore machine: one output per state (one output column) Mealy machine: One output per state and for each input combination (one output column per input combination) Step 3: Reduce the number of states in State/output table by removing redundant states (a state is redundant if for the same input combinations) it has the same next state and output as another state. Step4: Encode the states in binary (for n states, log2n bits are required). Each bit in the code represents a flip flop. Step5: Substitute corresponding binary codes to states in the State/Output table Step6: Separate the state table into flip flop next state maps (one map for each bit or flip flop) Step7: Use the flip flop next state map to derive flip flop excitation maps (this step depends on the type of flip flop used in the design) Step8: Use the flip flop excitation maps to determine excitation equations for the flip flop (these equations define the input logic of the flip flop) Step 9: Use the State/Output table to define the output logic circuit Step10: Draw the circuit, including flip flop, flip flop input circuits and output circuit. 5 Sequential logic networks V. Sequential Network Design Example 1 Step1: Problem Description (Word description) Design a sequential machine that detects a 01 sequence. The detection of sequence sets the output, Z=1, which is reset (Z=0) only by a 00 input sequence Note: The input is scan one bit at a time 6 Sequential logic networks V. Sequential Network Design Example 1: STEP 1 Step1: State Transition Diagram of the sequential machine: Recall that a State Transition Diagram consists of : States (representated by circles) Transitions (represented as arcs) between states Transitions are labelled by input that cause them Output are associated with – input labels (MEALY MACHINE) – State labels (MOORE MACHINE) 7 Sequential logic networks V. Sequential Network Design Example 1: STEP1 State diagram of example 1 (Mealy Machine): 0/0 1/1 1/1 1/0 A 0/0 B C 0/1 State Description: A : initial state (sequence does not begin) B : 0 is detected, expecting a 1 C : 01 sequence detected, output set to 1 Must detect a 00 to reset output to 0 First 0 detected, go to B to wait for second 0 8 Sequential logic networks V. Sequential Network Design Example 1: STEP 2 State/Output table 0/0 1/1 1/1 1/0 A 0/0 C B 0/1 For each (current state, input) pair, specify: •Next State •Output State/Output table (Mealy Machine) NS Output X=0 X= 1 X=0 X= 1 CS A B C 9 B B B A C C 0 0 1 0 1 1 Sequential logic networks V. Sequential Network Design Example 1: STEP2 State diagram (Moore Machine): 0 1 1 1 A,0 0 B,0 0 1 D,1 C,1 0 A: Waiting for start of sequence 01 and output 0 B: 0 is detected, wait for 1 and output 0 C: Sequence 01 is detected, output 1 and wait for 00 to reset output D: Start of 00 is detected; wait for the final 0 to reset output • when we get 0, go to B and output 0 •When we get 1, go back to C to wait for 00 sequence 10 Sequential logic networks V. Sequential Network Design Example 1: STEP 2 0 1 1 1 A,0 0 0 State /Output Table: NS CS A B C D 11 B,0 Output X=0 X= 1 B B D B A C C C 0 0 1 1 1 D,1 C,1 0 Sequential logic networks V. Sequential Network Design Example 1: STEP 3 Reduce the number of states in STATE/OUTPUT table: NO Redundant states in example 1 State /Output Table: NS CS A B C D 12 X=0 X= 1 Output B B D B A C C C 0 0 1 1 Output does not Depend on input X Sequential logic networks V. Sequential Network Design Example 1: STEP 4 State Assignment: Encode the different states There are 3 states We need two States Variable y1 and y0 • y1 is the leftmost bit (Flip flop 1) • y0 is the rightmost bit (Flip flop 0) One possible state assignment: A 00, B 01, C 10 : State code 11 is not used (don’t cares …) There are many more state assignments: For example, We could use the following assignments A 11, B 10, C 01 : State code 00 is not used (don’t cares …) A 10, B 11, C 00 : State code 01 is not used (don’t cares …) 13 Sequential logic networks V. Sequential Network Design Example 1: STEP 5 Substitute State Codes in the State/output table State assignment: A 00, B 01, C 10 NS CS X=0 A B C B B B Output X= 1 X=0 X= 1 A C C 0 0 1 0 1 1 State/Output table (Mealy Machine) NS Output X=0 X= 1 X=0 X= 1 CS 14 00 01 10 11 01 01 01 dd 00 10 10 dd 0 0 1 d 0 1 1 d Unused state code Sequential logic networks V. Sequential Network Design Example 1: STEP 6 Flip Flop Next State Maps State/Output table (Mealy Machine) CS y1 (flip flop 1) y0 (flip flop 0) 00 01 10 11 NS Output X=0 X= 1 X=0 X= 1 01 01 01 dd Flip flop 1 Current Next state Y1 00 01 10 11 15 0 0 1 d 0 1 1 d Flip flop 0 Current Next state Y0 X (y1y0) 00 10 10 dd X (y1y0) 0 1 0 0 0 d 0 1 1 d Flip flop Next state maps 00 01 10 11 0 1 1 1 1 d 0 0 0 d Sequential logic networks V. Sequential Network Design Example 1: STEP 7 Flip Flop Excitation Maps •Determine transitions of flip flop •For each transition, give the input that cause the transition (Depends on the type of flip flops) Assume JK flip flop for y1 and y0 Flip flop 1 (J1, K1) Current Next state Y1 0 0 0 0 d 0 1 J1 K1 J1 K1 1 0 1 1 d Next transition for X=0 and X=1 16 X (y1y0) X (y1y0) 00 01 10 11 Flip flop 1 (J1, K1) Current Next state Y1 00 01 10 11 0 0 d d d 0 d 1 1 d d d d d 0 d Sequential logic networks V. Sequential Network Design Example 1: STEP 7 Flip Flop Excitation Maps Assume JK flip flop for y1 and y0 Flip flop 0 (J0, K0) Current Next state Y0 Flip flop 0 Current Next state Y0 00 01 10 11 0 X (y1y0) 1 J0 K0 J0 K0 0 1 1 1 1 d 0 0 0 d Next transition for X=0 and X=1 17 X (y1y0) 00 01 10 11 1 d 1 d d 0 0 d d 0 d d d 1 d d Sequential logic networks V. Sequential Network Design Example 1: STEP 8 Flip Flop Excitation Equations (Input circuits of flip flops) • Derive K- Maps from excitation maps • Use K-maps to derive flip flop input equations J1 y1y0 X Flip flop 1 (J1, K1) Current Next state Y1 J1 input 00 01 11 10 0 1 d d d d 0 0 1 0 X (y1y0) 0 J1 = x•y0 1 J1 K1 J1 K1 00 01 10 11 0 0 d d d 0 d 1 1 d d d d d 0 d K1 y1y0 X K1 input 0 1 00 01 11 10 d d d d d d 1 0 K1 = x’ 18 Sequential logic networks V. Sequential Network Design Example 1: STEP 8 Flip Flop Excitation Equations (Input circuits of flip flops) • Derive K- Maps from excitation maps • Use K-maps to derive flip flop input equations J0 y1y0 X 11 10 d d d d 1 0 X (y1y0) 0 1 J0 K0 J0 K0 1 d 1 d d 0 0 d d 0 d d J0 input d 1 d d J0 = X’ K0 y1y0 X K0 input 0 1 00 01 11 10 d d 0 1 d d d d K0 = X 19 01 0 1 1 0 Flip flop 0 (J0, K0) Current Next state Y0 00 01 10 11 00 Sequential logic networks V. Sequential Network Design Example 1: STEP 9 Determine the output logic circuit Z tate/Output table (Mealy Machine) y1y0 00 01 10 11 NS Output Z X=0 X= 1 X=0 X= 1 01 01 01 dd 00 10 10 dd 0 0 1 d 0 1 1 d y1y0 X 0 1 00 01 11 10 0 0 0 1 d d 1 1 Z = y1 + x•y0 K-map of output Z 20 Sequential logic networks V. Sequential Network Design Example 1: STEP 10 Input circuit Draw the circuit: (Flip flops and logic gates) J1 Q y1 Memory components K1 X J0 CLK K0 Q y0 Output circuit OR 21 Z Sequential logic networks V. Sequential Network Design Homework Design the 01 sequence detector as a Moore machine. The ouput is reset 0 when a 00 sequence is detected. Design the detectector using: • clocked JK flip flops • clocked D flip flops 22 Sequential logic networks V. Sequential Network Design Example 2 Give the state diagram of a clocked sequential circuit that recognizes the input sequence 1010, including overlapping. For example, for the input sequence X = 00101001010101110, the corresponding output Z is Z = 00000100001010000 Overlapping State diagram (Moore Machine): 1 1 0 1 0 A,0 B,0 0 C,0 D,0 1 1 0 0 23 E,1 Sequential logic networks V. Sequential Network Design Example 3 Design a Moore synchronous sequential circuit to detect a string of of three or more consecutive 1’s in an arbitrary input string. Design the detectector using: • clocked JK flip flops • clocked D flip flops 24 Sequential logic networks V. Sequential Network Design Example 4 Using D flip flops, design a Moore synchronous sequential comparator circuit to determine which of the two multi-bits binary numbers X and Y (of equal Length) is larger. The comparison is carried out from left (Most Significant Bit) to right. Both MSB are used as input to the circuit. Assume two outputs Z1Z2 such that: Z1 = 1 if X > Y Z2 = 1 if X < Y Z1= Z2 = 0 if X = Y 25 Sequential logic networks V. Sequential Network Design Example 5 Design a two-bit clocked sequential counter circuit that counts clock pulses. 26 Sequential logic networks Design examples Example1 Give the state diagram of a clocked sequential circuit that recognizes the input sequence 1010, including overlapping. For example, for the input sequence X = 00101001010101110, the corresponding output Z is Z = 00000100001010000 Example2 Design a Moore synchronous sequential circuit to detect a string of of three or more consecutive 1’s in an arbitrary input string. Design the detectector using: • clocked JK flip flops • clocked D flip flops Example3 Using D flip flops, design a Moore synchronous sequential comparator circuit to determine which of the two multibits binary numbers X and Y (of equal Length) is larger. The comparison is carried out from left (Most Significant Bit) to right. Both MSB are used as input to the circuit. Assume two outputs Z1Z2 such that: Z1 = 1 if X > Y Z2 = 1 if X < Y Z1= Z2 = 0 if X = Y Example4 Design a two-bit clocked sequential counter circuit that counts clock pulses. 27